Abstract

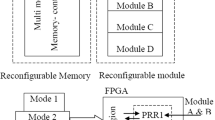

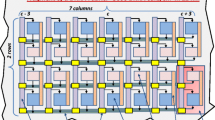

This paper presents a TriMedia processor extended with an IDCT reconfigurable design, and assesses the performance gain such an extension has when performing MPEG-2 decoding. We first propose the skeleton of an extension of the TriMedia architecture, which consists of a Field-Programmable Gate Array (FPGA)-based Reconfigurable Functional Unit (RFU), a Configuration Unit managing the reconfiguration of the RFU, and their associated instructions. Then, we address the computation of the 8 × 8 (2-D) IDCT on such extended TriMedia and propose a scheme to implement the 1-D IDCT operation on the RFU. When mapped on an ACEX EP1K100 FPGA from Altera, the proposed 1-D IDCT exhibits a latency of 16 and a recovery of 2 TriMedia@200 MHz cycles, and occupies 45% of the logic cells of the device. By configuring the 1-D IDCT on the RFU at application launch-time, the IEEE-compliant 2-D IDCT can be computed with the throughput of 1/32 IDCT/cycle. This figure translates to an improvement over the standard TriMedia of more than 40% in terms of computing time when 2-D IDCT is carried out in the framework of MPEG-2 decoding. Finally, the proposed reconfigurable IDCT is compared to a number of existing designs.

Similar content being viewed by others

References

J.T.J. van Eijndhoven, F.W. Sijstermans, K.A. Vissers, E.-J.D. Pol, M.J.A. Tromp, P. Struik, R.H.J. Bloks, P. van der Wolf, A.D. Pimentel, and H.P. Vranken, “TriMedia CPU64 Architecture,” in Proceedings of International Conference on Computer Design (ICCD ‘99), Austin, Texas, 1999, pp. 586–592.

J.T. van Eijndhoven and F. Sijstermans, “Data Processing Device and method of Computing the Cosine Transform of a Matrix,” U.S. Patent No. 6,397,235, 2002.

A.K. Riemens, K.A. Vissers, R.J. Schutten, F.W. Sijstermans, G.J. Hekstra, and G.D.L. Hei, “TriMedia CPU64 Application Domain and Benchmark Suite,” in Proceedings of International Conference on Computer Design (ICCD ‘99), Austin, Texas, 1999, pp. 580–585.

K.R. Rao and P. Yip, Discrete Cosine Transform. Algorithms, Advantages, Applications}, San Diego, California: Academic Press, 1990.

J.L. Mitchell, W.B. Pennebaker, C.E. Fogg, and D.J. LeGall, MPEG Video Compression Standard}, New York, New York: Chapman & Hall, 1996.

C. Loeffler, A. Ligtenberg, and G.S. Moschytz, “Practical Fast 1-D DCT Algorithms with 11 Multiplications,” in Proceedings of the International Conference on Acoustics, Speech, and Signal Processing (ICASSP ‘89), 1989, pp. 988–991.

“IEEE Standard Specifications for the Implementations of 8 × 8 Inverse Discrete Cosine Transform,” IEEE Std 1991, pp. 1180–1990.

S. Brown and J. Rose, “Architecture of FPGAs and CPLDs: A Tutorial,” IEEE Transactions on Design and Test of Computers vol. 13, no. 2, 1996, pp. 42–57.

Altera Corporation, ACEX 1K Programmable Logic Family}, Datasheet, San Jose, California, 2000.

J.T. van Eijndvhoven, G.A. Slavenburg, and S. Rathnam, “VLIW Processor has Different Functional Units Operating on Commands of Different Widths,” U.S. Patent No. 6,076,154, 2000.

S. Vassiliadis, S. Wong, and S. Cotofana, “The MOLEN ρμ-coded Processor,” in 11th International Conference on Field-Programmable Logic and Applications (FPL 2001), vol. 2147 of Lecture Notes in Computer Science (LNCS), Belfast, Northern Ireland, United Kingdom, Springer-Verlag, 2001, pp. 275–285.

M. Sima, S. Vassiliadis, S.D. Cotofana, J.T. van Eijndhoven, and K.A. Vissers, “Field-Programmable Custom Computing Machines. A Taxonomy,” in 12th International Conference on Field-Programmable Logic and Applications (FPL 2002), vol. 2438 of Lecture Notes in Computer Science (LNCS), Montpellier, France, Springer-Verlag, 2002, pp. 79–88.

E.-J.D. Pol, B.J.M. Aarts, J.T.J. van Eijndhoven, P. Struik, F.W. Sijstermans, M.J.A. Tromp, J.W. van de Waerdt, and P. van der Wolf, “TriMedia CPU64 Application Development Environment,” in Proceedings of International Conference on Computer Design (ICCD ‘99), Austin, Texas, 1999, pp. 593–598.

A. DeHon, “Reconfigurable Architectures for General-Purpose Computing,” A. I. 1586, Massachusetts Institute of Technology, Cambridge, Massachusetts, 1996.

J. van Eijndhoven, “16-Bit Compliant Software IDCT on TriMedia/CPU64,” Internal Report NL-TN 171, Philips Research Laboratories, Prof. Holstlaan 4, 5656 AA Eindhoven, The Netherlands, 1997.

M. Sima, S. Cotofana, J.T. van Eijndhoven, S. Vassiliadis, and K. Vissers, “8 × 8 IDCT Implementation on an FPGA-Augmented TriMedia,” in 9th Annual IEEE Symposium on Field-Programmable Custom Computing Machines (FCCM 2001), Rohnert Park, California, 2001.

B. Parhami, Computer Arithmetic: Algorithms and Hardware Designs}, New York, New York: Oxford University Press, 2000.

J. Hoogerbrugge and L. Augusteijn, “Instruction Scheduling for TriMedia,” Journal of Instruction-Level Parallelism, vol. 1, no. 1, 1999.

K. Chaudhary, H. Verma, and S. Nag, “An Inverse Discrete Cosine Transform (IDCT) Implementation in Virtex for MPEG Video Application,” Application Note 208, Xilinx Corporation, San Jose, California, 1996.

T. Miyamori and K. Olukotun, “REMARC: Reconfigurable Multimedia Array Coprocessor,” IEEE Transactions on Information and Systems, vol. E82-D, no. 2, 1999, pp. 389–397.

H. Singh, M.-H. Lee, G. Lu, F.J. Kurdahi, N. Bagherzadeh, and E.M.C. Filho, “MorphoSys: An Integrated Reconfigurable System for Data-Parallel and Computation-Intensive Application,” IEEE Transactions on Computers, vol. 49, no. 5, 2000, pp. 465–481.

G.G. Pechanek and S. Vassiliadis, “The ManArray Embedded Processor Architecture,” in Proceedings of the 26th Euromicro Conference, “Informatics: Inventing the Future”, Maastricht, The Netherlands, 2000, pp. 348–355.

G.G. Pechanek, C.W. Kurak, C.J. Glossner, C.H.L. Moller, and S.J. Walsh, “M.F.A.S.T.: A Highly Parallel Single Chip DSP with a 2D IDCT Example,” in Proceeding of the International Conference on Signal Processing Applications and Technology (ICSPAT ’95), Boston, Massachusetts, 1995, pp. 69–72.

Author information

Authors and Affiliations

Corresponding author

Additional information

Mihai Sima was born in Bucharest, Romania. He received the MS degree in Electrical Engineering from ‘Politehnica’ University of Bucharest, and the Ph.D. degree in Electrical Engineering from Delft University of Technology, The Netherlands. He had been with the ‘Microelectronics’ Company in Bucharest for 3 years, where he was involved in instrumentation electronics for integrated circuit testing. Subsequently, he joined the Telecommunications Department of ‘Politehnica’ University of Bucharest, where he had been involved in digital signal processing and speech recognition for 6 years. More recently, he had been with the Faculty of Electrical Engineering, Mathematics, and Computer Science, Delft University of Technology, where he worked on reconfigurable architectures for mediaprocessing domain. He is currently an assistant professor with the Department of Electrical and Computer Engineering, University of Victoria, B.C., Canada. His research interests include computer architecture, reconfigurable computing, embedded systems, digital signal processing, and speech recognition.

Sorin D. Coţofană was born in Mizil, Romania. He received the MS degree in Computer Science from the ‘Politehnica’ University of Bucharest, Romania, and the Ph.D. degree in Electrical Engineering from Delft University of Technology, The Netherlands. He had worked with the Research & Development Institute for Electronic Components (ICCE) in Bucharest for a decade, being involved in structured design of digital systems, design rule checking of IC’s layout, logic and mixed-mode simulation of electronic circuits, testability analysis, and image processing. He is currently an associate professor with the Faculty of Electrical Engineering, Mathematics, and Computer Science, Delft University of Technology, The Netherlands. His research interests include computer arithmetic, parallel architectures, embedded systems, reconfigurable computing, nano-electronics, neural networks, computational geometry, and computer aided design.

Jos T.J. van Eijndhoven was born in Roosendaal, The Netherlands. He studied Electrical Engineering at the Eindhoven University of Technology, The Netherlands, obtaining the M.Sc. and Ph.D. degrees in 1981 and 1984, respectively, for a work on piecewise linear circuit simulation. Then, he became a senior research member in the design automation group of the Eindhoven University of Technology. In 1986 he spent a sabbatical period at the IBM Thomas J. Watson Research Laboratory, Yorktown Heights, New York, for research on high level synthesis. In 1998 he joined Philips Research Laboratories in Eindhoven, The Netherlands, to work on the architectural design of programmable multimedia hardware and the associated mapping of media processing applications.

Stamatis Vassiliadis was born in Manolates, Samos, Greece. He is a professor with the Faculty of Electrical Engineering, Mathematics, and Computer Science, Delft University of Technology, The Netherlands. He has also served in the faculties of Cornell University, Ithaca, NY, and the State University of New York (S.U.N.Y.), Binghamton, NY.He hadworked for a decade with IBM in the AdvancedWorkstations and Systems laboratory in Austin TX, the Mid-Hudson Valley Laboratory in Poughkeepsie, NY, and the Glendale Laboratory in Endicott, NY. In IBM he was involved in a number of projects regarding computer design, organizations, and architectures and the leadership to advanced research projects. A number of his design and implementation proposals have been implemented in commerciallyavailable systems and processors including the IBM 9370 model 60 computer system, the IBM POWER II, the IBM AS/400 Models 400, 500, and 510, Server Models 40S and 50S, the IBM AS/400 Advanced 36, and the IBM S/390 G4 and G5 computer systems. For his work, he received numerous awards including 23 levels of Publication Achievement Awards, 15 levels of Invention Achievement Awards and an Outstanding Innovation Award for Engineering/Scientific Hardware Design in 1989. In 1990 he has been awarded the highest number of USA patents in IBM, six of his 70 USA patents being rated with the highest patent ranking in IBM.

Kees A. Vissers graduated the Delft University of Technology, receiving his M.Sc. in 1980. He started directly with Philips Research Laboratories in Eindhoven where he was involved in highlevel simulation and high-level synthesis. He had been heading the research on hardware/software co-design and system level design for many years, and had a significant contribution to the TriMedia VLIW processor. From 1987 till 1988 he was a visiting researcher at Carnegie Mellon University, Pittsburgh, Pennsylvania, with the group of Don Thomas. He is currently a Research Fellow with University of California at Berkeley, Department of Electrical Engineering and Computer Sciences. His research interests include video processing, embedded media processing systems, and reconfigurable computing.

Rights and permissions

About this article

Cite this article

Sima, M., Cotţofaná, S., Van Eijndhoven, J.T.J. et al. IEEE-Compliant IDCT on FPGA-Augmented TriMedia. J VLSI Sign Process Syst Sign Image Video Technol 39, 195–212 (2005). https://doi.org/10.1007/s11265-005-4840-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-005-4840-y