Abstract

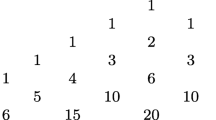

A high-radix digit-recurrence algorithm for the computation of the logarithm, and an analysis of the tradeoffs between area and speed for its implementation, are presented in this paper. Selection by rounding is used in iterations j ≥ 2, and by table look-up in the first iteration. A sequential architecture is proposed, and estimates of the execution time and hardware requirements are obtained for n = 16, 24, 32, 53 and 64 bits of precision and for radix values from r = 8 to r = 1024. These estimates are obtained according to an approximate model for the delay and area of the main logic blocks. We show that the most efficient implementations are obtained for radices ranging from r = 32 to r = 256, reducing the execution time by half with respect to a radix-4 implementation with redundant arithmetic.

Similar content being viewed by others

References

M. Arnold, “Reduced Power Consumption in MPEG Decoding using LNS,” in Proc. IEEE 13th Intl. Conference on Application-specific Systems, Architectures and Processors (ASAPÕ02), 2002, pp. 65–76.

D.M. Lewis, “114 MFLOPS Logarithmic Number System Arithmetic Unit for DSP Applications,” IEEE Journal of Solid-State Circuits, vol. 30, no. 12, 1995, pp. 1547-1553.

E. Antelo, T. Lang, and J.D. Bruguera, “High-Radix CORDIC Rotation Based on Selection by Rounding,” Journal of VLSI Signal Processing, vol. 25, no. 2, 2000, pp. 141–153.

J.-A. Piñeiro and J.D. Bruguera, “High-Speed Double-Precision Computation of Reciprocal, Division, Square Root and Inverse Square Root,” IEEE Transactions on Computers, vol. 51, no. 12, 2002, pp. 1377–1388.

H.C. Shin, J.A. Lee, and L.S. Kim, “A Minimized Hardware Architecture of Fast Phong Shader using Taylor Series Approximation in 3D Graphics,” in Proc. International Conference on Computer Design, VLSI in Computers and Processors, 1998, pp. 286–291.

W. Cody and W. Waite, Software Manual for the Elementary Functions, Prentice-Hall, 1980.

P. Markstein, IA-64 and Elementary Functions, Hewlett-Packard Professional Books, 2000.

P.T.P. Tang, “Table Look-up Algorithms for Elementary Functions and Their Error Analysis,” in Proc. IEEE 10th Int. Symp. Computer Arithmetic (ARITH10), 1991, pp. 232-236.

C.T. Fike, Computer Evaluation of Mathematical Functions, Prentice-Hall, 1968.

J.M. Muller, Elementary Functions, Algorithms and Implementation, Birkhauser, 1997.

M.J. Schulte and J.E. Stine, “Symmetric Bipartite Tables for Accurate Function Approximation,” in Proc. 13th Symp. Computer Arithmetic (ARITH13), 1997, pp. 175–183.

M.J. Flynn, “On Division By Functional Iteration,” IEEE Transactions on Computers, vol. 19, 1970, pp. 702–706.

S.F. Oberman, “Floating Point Division and Square Root Algorithms and Implementation in the AMD-K7 Microprocessor,” in Proc. 14th Symp. Computer Arithmetic (ARITH14), 1999, pp. 106–115.

M.D. Ercegovac, “Radix-16 Evaluation of Certain Elementary Functions,” IEEE Transactions on Computers, vol. 22, no. 6, 1973, pp. 561–566.

M.D. Ercegovac and T. Lang, Division and Square Root: Digit Recurrence Algorithms and Implementations, Kluwer Academic Publishers, 1994.

M.D. Ercegovac, T. Lang, and P. Montuschi, “Very High-Radix Division with Selection by Rounding and Prescaling,” IEEE Transactions on Computers, vol. 43, no. 8, 1994, pp. 909-918.

E. Antelo, T. Lang, and J. D. Bruguera, “Computation of √x/d in a Very-High Radix Combined Division/Square-Root Unit with Scaling and Selection by Rounding,” IEEE Transactions on Computers, vol. 47, no. 2, 1998, pp. 152-161.

E. Antelo, T. Lang, and J.D. Bruguera, “Very-High Radix CORDIC Vectoring with Scalings and Selection by Rounding,” in Proc. 14th Symp. Computer Arithmetic, 1999, pp. 204-213.

T. Lang and P. Montuschi, “Very-High Radix Square Root with Prescaling and Rounding and a Combined Division/Square Root Unit,” IEEE Transactions on Computers, 1999, pp. 827-841.

J.-A. Piñeiro, “Algorithms and Architectures for Elementary Function Computation,” PhD Dissertation, University of Santiago de Compostela, 2003.

J.-A. Piñeiro, M.D. Ercegovac, and J.D. Bruguera, “High-Radix Logarithm with Selection by Rounding,” in Proc. IEEE 13th Intl. Conference on Application-specific Systems, Architectures and Processors (ASAPÕ02), 2002, pp. 101–110.

J.-A. Piñeiro, M.D. Ercegovac, and J.D. Bruguera, “Analysis of the Tradeoffs in the Implementation of a High-Radix Logarithm,” in Proc. 2002 IEEE Intl. Conference on Computer Design (ICCDÕ02), 2002, pp. 132–137.

P.W. Baker, “Parallel Multiplicative Algorithms for Some Elementary Functions,” IEEE Transactions on Computers, 1975, pp. 322–325.

R.W. Bemer, “A Subroutine Method for Calculating Logarithms,” CACM, vol. 1, 1958, pp. 5–7.

J.N. Mitchell, “Computer Multiplication and Division using Binary Logarithms,” IEEE Transactions on Electronic Computers, 1962, pp. 512–517.

W.H. Specker, “A Class of Algorithms for Ln(x), Exp(x), Sin(x), Cos(x), Tan(x) and Cot(x),” IEEE Transactions Electronic Computers, vol. 14, 1965, pp. 85–86.

M.D. Ercegovac and T. Lang, “On-the-fly Conversion of Redundant into Conventional Representations,” IEEE Transactions on Computers, vol. C-36, no. 7, 1987, pp. 895-897.

M.D. Ercegovac and T. Lang, “On-the-fly Rounding,” IEEE Transactions on Computers, vol. 41, no. 12, 1992, pp. 1497–1503.

Waterloo Maple Inc, Maple 8 Programming Guide, 2002.

T.C. Chen, “Automatic Computation of Exponentials, Logarithms, Ratios and Square-Roots,” IBM Journal Research and Development, 1972, pp. 380–388.

P. Kornerup, “Reviewing 4-to-2 Adders for Multi-Operand Addition,” in Proc. IEEE 13th Intl. Conference on Application-specific Systems, Architectures and Processors (ASAPÕ02), 2002, pp. 218–229.

M.D. Ercegovac, T. Lang, J.M. Muller, A. Tisserand, “Reciprocation, Square Root, Inverse Square Root, and Some Elementary Functions Using Small Multipliers,” IEEE Transactions on Computers, vol. 49, no. 7, 2000, pp. 628-637.

W.F. Wong and E. Goto, “Fast Hardware-Based Algorithms for Elementary Function Computations,” IEEE Transactions on Computers, vol. 43, no. 3, 1994, pp. 278-294.

Author information

Authors and Affiliations

Corresponding author

Additional information

Jose-Alejandro Piñeiro was born in Domayo, Spain. He received the Ph.D. degree in Computer Engineering in 2003, and the M.Sc. degree (1999) and B.Sc. degree (1998) in Physics (Electronics), from the University of Santiago de Compostela, Spain. Since 2004, he has been with Intel Barcelona Research Center, Intel Labs-UPC, whose research focuses on new microarchitectural paradigms and code generation techniques for IA-32, EM64T and IPF families. His research interests are also in the area of computer arithmetic, VLSI design, computer graphics and numerical processors.

Miloš D. Ercegovac is a Professor and Chair in the UCLA Computer Science Department. He earned his MS (‘72) and Ph.D. (‘75) in computer science from the University of Illinois, Urbana-Champaign, and BS in electrical engineering (‘65) from the University of Belgrade, Yugoslavia. Dr. Ercegovac specializes in research and teaching in digital arithmetic, digital design, and computer system architecture. His research contributions have been extensively published in journals and conference proceedings. He is a coauthor of two textbooks on digital design and of a monograph in the area of digital arithmetic. Dr. Ercegovac has been involved in organizing the IEEE Symposia on Computer Arithmetic since 1978. He served as an editor of the IEEE Transactions on Computers and as a subject area editor for the Journal of Parallel and Distributed Computing. Dr. Ercegovac is a senior member of the IEEE Computer Society and a member of the ACM.

Javier D. Bruguera received the B.S. degree in Physics and the Ph.D. degree from the University of Santiago de Compostela (Spain) in 1984 and 1989, respectively. Currently, he is a professor in the Department of Electronic and Computer Engineering at the University of Santiago de Compostela. Previously, he was an assistant professor in the Department of Electrical, Electronic and Computer Engineering at the University of Oviedo, Spain, and an assistant professor in the Department of Electronic Engineering at the University of A Coruña, Spain. He was a visiting researcher in the Application Center of Microelectronics at Siemens in Munich, Germany, and in the Department of Electrical Engineering and Computer Science at the University of California, Irvine. Dr. Bruguera’s primary research interests are in the area of computer arithmetic, processor design, digital design for signal and image processing and parallel architectures.

Rights and permissions

About this article

Cite this article

Piñeiro, JA., Ercegovac, M.D. & Bruguera, J.D. High-Radix Logarithm with Selection by Rounding: Algorithm and Implementation. J VLSI Sign Process Syst Sign Image Video Technol 40, 109–123 (2005). https://doi.org/10.1007/s11265-005-4941-7

Received:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/s11265-005-4941-7