Abstract

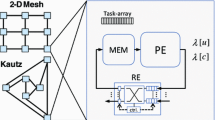

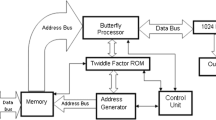

In this paper, we propose a reduced complexity and power efficient System-on-Chip (SoC) architecture for adaptive interference suppression in CDMA systems. The adaptive Parallel-Residue-Compensation architecture leads to significant performance gain over the conventional interference cancellation algorithms. The multi-code commonality is explored to avoid the direct Interference Cancellation (IC), which reduces the IC complexity from \(\mathcal{O}(K^2N)\) to \(\mathcal{O}(KN)\). The physical meaning of the complete versus weighted IC is applied to clip the weights above a certain threshold so as to reduce the VLSI circuit activity rate. Novel scalable SoC architectures based on simple combinational logic are proposed to eliminate dedicated multipliers with at least \(10 \times\)saving in hardware resource. A Catapult C High Level Synthesis methodology is apply to explore the VLSI design space extensively and achieve at least \(4 \times\)speedup. Multi-stage Convergence-Masking-Vector combined with clock gating is proposed to reduce the VLSI dynamic power consumption by up to \(90 \%\)

Similar content being viewed by others

References

M. K. Varanasi and B. Aazhang, “Multistage Detection in Asynchronous Code-Division Multiple-Access Communications,” IEEE Trans. Commun., vol. 38, pp. 509–519, Apr, 1990.

M. K. Varanasi and B. Aazhang, “Near-Optimum Detection in Synchronous Code-Division Multiple-Access Systems,” IEEE. Trans. Commun., vol. 39, pp. 725–736, 1991.

G. Xu and J. R. Cavallaro, “Real-Time Implementation of Multistage Algorithm for Next Generation Wideband CDMA Systems,” Proc. ASPA, IX, SPIE, vol. 3807, Denver, Colorado, pp. 62-73, July, 1999.

Q. Sun and D. C. Cox, “A Pipelined Multi-Stage Parallel Interference Canceller for CDMA with Realistic Channel Estimation,” IEEE Wireless Communications and Networking Conference, no. 1, pp. 294-298, March, 2002.

M. J. Juntti, B. Aazhang, and J. O. Lilleberg, “Iterative Implementation of Linear Multiuser Detection for Dynamic Asynchronous CDMA Systems,” IEEE Trans. Commun., vol. 46, pp. 503–508, Apr, 1998.

D. Divsalar, M. K. Simon, and D. Raphaeli, “Improved Parallel Interference Cancellation for CDMA,” IEEE Trans. Commun., vol. 46, pp. 258–268, Feb, 1998.

N. Correal, R. M. Buehrer, and B. D. Woerner, “A DSP-Based DS-CDMA Multiuser Receiver Employing Partial Parallel Interference Cancellation,” IEEE J. Sel. Areas Commun. (JSAC), vol. 17, pp. 613–630, Apr, 1999.

G. Xue, J. Weng, T. L. Ngoc, and S. Tahar, “Adaptive Multistage Parallel Interference Cancellation for CDMA,” IEEE J. Sel. Areas Commun., vol. 17, pp. 1815–1827, Oct, 1999.

Y. Guo, G. Xu, D. McCain, and J. Cavallaro, “Rapid Scheduling of Efficient VLSI Architectures for Next-Generation HSDPA Wireless System Using Precision-C Synthesizer,” Proc. IEEE Intl. Workshop on Rapid System Prototyping’03, San Diego, California, pp. 179–185, June, 2003.

Y. Guo, J. Zhang, D. McCain, and J. R. Cavallaro, “Scalable FPGA Architectures for LMMSE-Based SIMO Chip Equalizer in HSDPA Downlink,” IEEE Asilomar Conference on Signals, Systems and Computers, vol. 2, pp. 2171–2175, Monterey, California, Nov, 2003.

Y. Lee and V. K. Jain, “VLSI Architecture for an Advanced DS/CDMA Wireless Communication Receiver,” Proc. of IEEE International Conference on Innovative Systems in Silicon, pp. 237–247, Oct, 1997.

S. Das, C. Sengupta, and J. R. Cavallaro, “Hardware Design Issues for a Mobile Unit for Next Generation CDMA Systems,” Proc. SPIE Conf. Advanced Signal Processsing: algorithms, architectures and implementations, vol.3461, San Diego, California, July, 1998.

S. Rajagopal, B. A. Jones, and J. R. Cavallaro, “Task Partitioning Wireless Base-Station Receiver Algorithms on Multiple DSPs and FPGAs,” International Conference on Signal Processing Applications and Technology (ICSPAT), Dallas, Texas, October, 2000.

S. Kim, K. Kum, and W. Sung, “Fixed-Point Optimization Utility for C and C++ Based Digital Signal Processing Programs,” IEEE Trans. Circuits Syst 2: Analog digit signal Process, vol. 45, no.11, pp. 1455-1464, Nov, 1998.

A. Evens, A. Siburt, G. Vrchoknik, T. Brown, M. Dufresne, G. Hall, T. Ho, and Y. Liu, “Functional Verification of Large ASICS,” ACM/IEEE Design Automation Conference, San Francisco, California, pp. 650–655, June, 1998.

Y. Guo, D. McCain, and J. R. Cavalaro, “Low Complexity System-On-Chip VLSI Architectures of Optimal Parallel-Residue-Compensation for MAI Suppression in CDMA Systems,” IEEE Int. Symp. Circuit Syst., vol. 4, pp. 77–80, Vancouver, Canada, May, 2004.

M. S. Srivastava, A. P. Chandrakasan, and R. W. Brodersen, “Predictive System Shutdown and Other Architectural Techniques for Energy Efficient Programmable Computation,” IEEE Trans. Very Large Scale Integration (VLSI) Systems, vol. 4, no. 1, pp. 42–55, Mar, 1996.

L. Nenini and G. De Micheli, “Dynamic Power Management: Design Techniques and CAD Tools,” Kluwer, Norwell, Massachusetts, 1998.

N. Zervas, D. Soudris, S. Theoharis, C. E. Goutis, and A. Thanailakis, “A Methodology for the Behavioral-Level Event-Driven Power Management of Digital Receivers,” IEEE Int. Symp. Circuit Syst., vol. II, pp. 589–592, Geneva, Switzerland, May, 2000.

E. P. Zwyssig, A. T. Erdogan, and T. Arslan, “Low Power System on Chip Implementation Scheme of Digital Filtering Cores,” Low Power IC Design Seminar, London, UK, Jan, 2001.

H. Ohlsson, W. Li, O. Gustafsson, and L. Wanhammar, “A Low Power Architecture for Implementation of Digital Signal Processing Algorithms,” Proceeding of Swedish System-on-Chip Conf., Falkenberg, Sweden, Mar. 18–19, 2002.

G. C. Cardarilli, A. Nannarelli, and M. Re, “Reducing Power Dissipation in FIR Filters Using the Residue Number System,” 43rd IEEE Midwest Symposium on Circuits and Systems, vol. 1, pp. 320–323, Lansing, Michigan, USA, Aug, 2000.

J. Park, W. Jeong, H. Choo, H. M. Meimand, Y. Wang, and K. Roy, “High Performance and Low Power FIR Filter Design Based on Sharing Multiplication,” ISLPED’02, Monterey, California, USA, pp. 295-300, Aug. 12-14, 2002.

Author information

Authors and Affiliations

Corresponding author

Additional information

This paper was presented in part at IEEE ISCAS in Vancouver, Canada, May, 2004.

Rights and permissions

About this article

Cite this article

Guo, Y., Cavallaro, J.R. A Low Complexity and Low Power SoC Design Architecture for Adaptive MAI Suppression in CDMA Systems. J VLSI Sign Process Syst Sign Image Video Technol 44, 195–217 (2006). https://doi.org/10.1007/s11265-006-8535-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-006-8535-9