Abstract

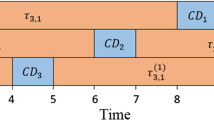

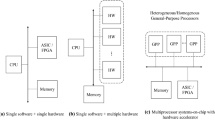

As technology scales, transient faults have emerged as a key challenge for reliable embedded system design. This paper proposes a design methodology that incorporates reliability into hardware–software co-design paradigm for embedded systems. We introduce an allocation and scheduling algorithm that efficiently handles conditional execution in multi-rate embedded systems, and selectively duplicates critical tasks to detect or correct transient errors, such that the reliability of the system is improved. Two methods are proposed to insert duplicated tasks into the schedule. The improved reliability is achieved by utilizing the otherwise idle computation resources and taking advantage of the overlapping schedule for mutually exclusive tasks in the conditional task graph, such that it incurs no resource or performance penalty.

Similar content being viewed by others

Reference

BCC Research, http://www.bccresearch.com/editors/RG-229R.html.

Todd M. Austin, “DIVA: A Reliable Substrate for Deep Submicron Microarchitecture Design,” in 32nd Annual International Symposium on Microarchitecture (MICRO), November 1999.

C. Bolchini, L. Pomante, F. Salice, and D. Sciuto, “Reliability Properties Assessment at System Level: a Co-design Framework,” Online Testing Workshop, 2001.

C. Bolchini, L. Pomante, F. Salice, and D. Sciuto, “A System Level Approach in Design Dual-Duplex Fault Tolerant Embedded Systems,” Online Testing Workshop, 2002.

B. Dave and N. K. Jha, “COFTA: Hardware-Software co-synthesis of Heterogeneous Distributed Embedded Systems for Low Overhead Fault Tolerance,” IEEE Trans. Comput., vol. 48, 1999.

R. P. Dick, D. L. Rhodes, and W. Wolf, “TGFF: Task Graphs for Free,” in Proc. Int. Workshop Hardware/Software Codesign, 1998, pp. 97–101.

A. Orailoglu and R. Karri, “A Design Methodology for the High-level Synthesis of Fault-tolerant Asics,” VLSI Signal Proc. V, 1992, pp. 417–426.

D. Mavis and P. Eaton, “Soft Error Rate Mitigation Techniques for Modern Microcircuits,” in Proc. Reliable Physics Symposium, 2002, pp. 216–225.

K. Mohanram and N. Touba, “Cost-Effective Approach for Reducing Soft Error Failure Rate in Logic Circuits,” ITC, 2003.

Shubhendu S. Mukherjee, Mike Kontz, and Steven K. Reinhardt, “Detailed Design and Implementation of Redundant Multithreading Alternatives,” in Proceedings of the 29th Annual International Symposium on Computer Architecture (ISCA), 2002.

Y. Xie and W. Wolf, “ASICosyn: Co-synthesis of Coditional Task Graphs with Custom ASICs,” in Proceedings of the International Conference on ASICs, 2001. pp. 130–135.

Actel Coroporation, “Effects of Neutrons on Programmable Logic,” White Paper, 2002.

Wayne Wolf and Jorgen Staunstrup, Hardware/Software Co-design Principles and Practice, Kluwer, 1997.

J. F. Ziegler et al. “IBM Experiments in Soft Fails in Computer Electronics (1978–1994),” IBM J. Res. Develop., vol. 40, no. 1, 1996, pp. 3–18.

B. Johnson, Design and Analysis of Fault-tolerant Digital Systems, Addison-Wesley, 1989.

H. Hollander, B. Carlson, and T. Bennett, “Synthesis of SEU-Tolerant ASICs Using Concurrent Error Corretion,” in Proceedings of IEEE Great Lake VLSI Symposium, 1995, pp. 90–93.

R. Karri and A. Orailoglu, “Time-constrained Scheduling during High-level Synthesis of Fault-secure,” VLSI Digital Signal Processors, IEEE Transaction on Reliability, vol. 45, no. 3, 1996, pp. 404–413.

Yanbing L`i, and Jörg Henkel, “A Framework for Estimation and Minimizing Energy Dissipation of Embedded HW/SW Systems,” in Proceedings of DAC, 1998, pp. 188–193.

C. Constantinescu, “Trends and Challenges in VLSI Circuits Reliability,” IEEE Micro, July–August, 2003.

S. Tosun, O. Ozturk, N. Mansouri, E. Arvas, M. Kandemir, and Y. Xie, “An ILP Formulation for Reliability-oriented High-level Synthesis,” in Proceedings of the Sixth International Symposium on Quality Electronic Design (ISQED 2005). San Jose, CA, 22, 2005.

G.Micheli, R. Ernst, and W. Wolf, Readings in Hardware/Software Co-design, Morgan Kaufmann, 2002.

W. Wolf, “A Decade of Hardware/Software Co-design,” IEEE Computer, 2003, pp. 38–43.

R. P.Dick, “Multiobjective Synthesis of Low-power Real-time Distributed Embedded Systems,” Ph.D. thesis, Princeton University, 2002.

D. Coppersmith and P. Raghavan, “Multidimensional Online Bin Packing: Algorithms and Worst Case Analysis,” Oper. Res. Lett., vol. 8, 1989, pp. 17–20.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Xie, Y., Li, L., Kandemir, M. et al. Reliability-aware Co-synthesis for Embedded Systems. J VLSI Sign Process Syst Sign Im 49, 87–99 (2007). https://doi.org/10.1007/s11265-007-0057-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-007-0057-6