Abstract

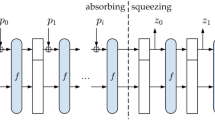

This paper presents a compact hardware architecture of Context-Based Adaptive Binary Arithmetic Coding (CABAC) codec for H.264/AVC. The similarities between encoding algorithm and decoding algorithm are explored to achieve remarkable hardware reuse. System-level hardware/software partition is conducted to improve overall performance. Meanwhile, the characteristics of CABAC algorithm are utilized to implement dynamic pipeline scheme, which increases the processing throughput with very small hardware overhead. Proposed architecture is implemented under 0.18 μm technology. Results show that the core area of proposed design is 0.496 mm2 when the maximum clock frequency is 230 MHz. It is estimated that the proposed architecture can support CABAC encoding or decoding for HD1080i resolution at a speed of 30 frame/s.

Similar content being viewed by others

References

J. Rissanen, “Generalized Kraft Inequality and Arithmetic Coding,” IBM J. Res. Develop., vol. 20, no. 3, May, 1976, pp. 198–203.

J. Rissanen and G.G. Langdon, “Arithmetic Coding,” IBM J. Res. Develop., vol. 23, no. 2, Mar. 1979, pp. 149–162.

F. Rubin, “Arithmetic Stream Coding Using Fixed Precision Registers,” IEEE Trans. Inf. Theory, vol. 20, no. 6, Nov. 1979, pp. 672–675.

G.G. Langdon, “An Introduction To Arithmetic Coding,” IBM J. Res. Develop., vol. 28, no. 2, Mar. 1984, pp. 135–149.

P.G. Pennebaker, J.L. Mitchell, G.G. Langdon and R.B. Arps, “An Overview Of The Basic Principles of the Q-Coder Adaptive Binary Arithmetic Coder,” IBM J. Res. Develop., vol. 32, no. 6, Nov. 1998, pp. 717–726.

J. Rissanen and K.M. Mohiuddin, “A Multiplication-Free Multialphabet Arithmetic Code,” IEEE Trans. Commun., vol. 37, no. 2, Feb. 1989, pp. 93–98.

P.G. Howard and J.S. Vitter, “Practical implementations of arithmetic coding,” in Image and Text Compression, J.A. Storer (Eds.), Kluwer, Boston, MA, 1992, pp. 85–112.

D. Taubman and M.W. Marcellin, JPEG 2000 Image Compression: Fundamentals, Standards and Practice, Kluwer, Boston, MA, 2002.

D. Marpe and T. Wiegand, “A highly efficient multiplication-free binary arithmetic coder and its application in video coding,” in Proceedings of International Conference on Image Processing, vol. 2, Sep. 2003, pp. II–263–266.

T. Wiegand, G.J. Sullivan, G. Bjontegaard and A. Luthra, “Overview of the H.264/AVC Video Coding Standard,” in IEEE Trans. Circuits Syst. Video Technol., vol. 13, no. 7, Jul. 2003, pp. 560–576.

J. Ostermann, J. Bormans, P. List, D. Marpe, M. Narroschke, F. Pereira, T. Stockhammer and T. Wedi, “Video Coding with H.264/AVC: Tools, Performance, And Complexity,” IEEE Mag. Circuits and Syst., vol. 4, First quarter 2004, pp. 7–28.

ITU-T “Draft ITU-T Recommendation H.264 and Draft ISO/IEC 14496-10 AVC,” Joint Video Team of ISO/IEC JTC1/SC29/WG11 & ITU-T SG16/Q.6 Doc. JVT-G050, Mar. 2003.

D. Marpe, H. Schwarz and T. Wiegand, “Context-Based Adaptive Binary Arithmetic Coding in the H.264/AVC Video Compression Standard,” IEEE Trans. Circuits Syst. Video Technol., vol. 13, no. 7, Jul. 2003, pp. 620–636.

W. Yu and Y. He, “A High Performance CABAC Decoding Architecture,” IEEE Trans. Consum. Electron., vol. 51, no. 4, Nov. 2005, pp. 1352–1359.

Y.W. Chang, H.C. Fang and L.G. Chen, “High Performance Two-Symbol Arithmetic Encoder in JPEG 2000,” in Proceedings of IEEE International Symposium on Consumer Electronics, vol. 1, Sep. 2004, pp. 101–104.

M. Dyer, D. Taubman and S. Nooshabadi, “Improved Throughput Arithmetic Coder For Jpeg2000,” in Proceedings of International Conference on Image Processing, vol. 4, Oct. 2004, pp. 2817–2820.

G. Pastuszak, “High-Performance Architecture For Embedded Block Coding in JPEG 2000,” IEEE Trans. Circuits Syst. Video Technol., vol. 15, no. 9, Sep. 2005, pp. 1182–1191.

R.R. Osorio and J.D. Bruguera, “High-Throughput Architecture for H.264/AVC CABAC Compression System,” IEEE Trans. Circuits Syst. Video Technol., vol. 16, no. 11, Nov. 2006, pp. 1376–1384.

Y.C. Yang, C.C. Lin, H.C. Chang, C.L. Su and J.I. Guo, “A High Throughput VLSI Architecture Design for H.264 Context-Based Adaptive Binary Decoding with Look Ahead Parsing,” in Proceeding of IEEE International Conference on Multimedia and Expo, Toronto, July, 2006.

J.L. Nunez and V.A. Chouliaras, “High-performance Arithmetic Coding VLSI Macro for the H264 Video Compression Standard,” IEEE Trans. Consum. Electron., vol. 51, no. 1, Feb. 2005, pp. 144–151.

S.R. Kuang, J.M. Jou, R.D. Chen and Y.H. Shiau, “Dynamic Pipeline Design Of An Adaptive Binary Arithmetic Coder,” IEEE Trans. Circuits Syst., 2 Analog Digit. Signal Process., vol. 48, no. 9, Sep. 2001, pp. 813–825.

H. Shojania and S. Sudharsanan, “A High Performance CABAC Encoder,” in Proceedings of 3rd International IEEE Northeast Workshop on Circuits and Systems, vol. 1, Jun. 2005, pp. 315–318.

J.W. Chen, C.R. Chang and Y.L. Lin, “A Hardware Accelerator For Context-Based Adaptive Binary Arithmetic Decoding in H.264/AVC,” in Proceeding of IEEE Symposium on Circuits and Systems, vol. 5, May 2005, pp. 4525–4528.

V. Bhaskaran and K. Konstantinides, Image and Video Compression Standards: Algorithms and Architectures, 2nd ed., Kluwer, Boston 1999.

Author information

Authors and Affiliations

Corresponding author

Additional information

This work was supported by MEXT via Kitakyushu innovative cluster project and CREST.

Rights and permissions

About this article

Cite this article

Li, L., Song, Y., Li, S. et al. A Hardware Architecture of CABAC Encoding and Decoding with Dynamic Pipeline for H.264/AVC. J Sign Process Syst Sign Image 50, 81–95 (2008). https://doi.org/10.1007/s11265-007-0117-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-007-0117-y