Abstract

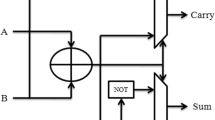

A high speed and low-power 8-bit carry-lookahead adder (CLA) using two-phase all-N-transistor (ANT) blocks which are arranged in a PLA design style with power-aware pipelining is presented. The pull-up charging and pull-down discharging of the transistor arrays of the PLA are accelerated by inserting two feedback MOS transistors between the evaluation NMOS blocks and the outputs. The analysis of the area (transistor count) tradeoff is also provided in this work. The output of the addition of two 8-bit binary numbers is done in two cycles. The proposed power-aware pipelining design methodology using a simple data transition detection circuit takes advantage of shutting down the processing stages with identical inputs in two consecutive cycles. The data transition detection circuit is used to monitor the state switching of input data. Not only is it proved to be also suitable for long adders, the power consumption is drastically reduced by at most 50% at every process corner.

Similar content being viewed by others

References

V.G. Oklobdzija, D. Villeger and T. Soulas, “An Integrated Multiplier for Complex Numbers,” The Journal of VLSI Signal Processing, vol. 7, no. 3, Oct. 1994, pp. 213–222.

R.V.K. Pillai, D. Al-Khalili, A.J. Al-Khalili and S.Y.A. Shah, “A Low Power Approach to Floating Point Adder Design for DSP Applications,” The Journal of VLSI Signal Processing, vol. 27, no. 3, March 2001, pp. 195–213.

M. Afghahi, “A Robust Single Phase Clocking for Low Power, High-Speed VLSI Applications,” IEEE J of Solid-State Circuits, vol. 31, no. 2, Feb. 1996, pp. 247–253.

R.X. Gu and M.I. Elmasry, “All-N-Logic High-Speed True-Single-Phase Dynamic CMOS Logic,” IEEE J Solid-State Circuits, vol. 31, no. 2, Feb. 1996, pp. 221–229.

R. Rogenmoser and Q. Huang, “An 800-MHz 1 mm CMOS Pipelined 8-b Adder Using True Phase Clocked Logic-Flip-Flops,” IEEE J Solid-State Circuits, vol. 31, no. 3, Mar. 1996, pp. 401–409.

K. Sundaresan, K.C. Brouse, K.U-Yen, F. Ayazi and P. E. Allen, “A 7-MHz Process, Temperature And Supply Compensated Clock Oscillator in 0.25 μm CMOS,” 2003 International Symposium on Circuits and Systems (ISCAS’03), vol. 1, May 2003, pp. 693–696.

C.-C. Wang, C.-J. Huang and K.-C. Tsai, “A 1.0 GHz 0.6-μm 8-bit Carry Lookahead Adder Using PLA-Styled All-N-Transistor Logic,” IEEE Trans of Circuits and Systems, Part II : Analog and Digital Signal Processing, vol. 47, no. 2, Feb. 2000, pp. 133–135.

Z. Wang, G.A. Jullien, W.C. Miller, J. Wang and S.S. Bizzan, “Fast Adders Using Enhanced Multiple-Output Domino Logic,” IEEE J Solid-State Circuits, vol. 32, no. 2, Feb. 1997, pp. 206–214.

C.-C. Wang, Y.-L. Tseng, P.-M. Lee, R.-C. Lee and C.-J. Huang, “A 1.25 GHz 32-bit Tree-Structured Carry Lookahead Adder Using Modified ANT Logic,” IEEE Trans on Circuits and Systems—I Fundamental Theory and Applications, vol. 50, no. 9, Sep. 2003, pp. 1208–1216.

C.-C. Wang, C.-F. Wu and K.-C. Tsai, “A 1.0 GHz 64-bit High-Speed Comparator Using ANT Dynamic Logic with Two-Phase Clocking,” IEE Proceedings—Computers and Digital Techniques, vol. 145, no. 6, Nov. 1998, pp. 433–436.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wang, CC., Sung, GN. & Liu, PL. Power-Aware Design of An 8-Bit Pipelining ANT-Based CLA Using Data Transition Detection. J Sign Process Syst Sign Image Video Technol 52, 127–135 (2008). https://doi.org/10.1007/s11265-007-0128-8

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-007-0128-8