# INTERCONNECT DRIVER DESIGN FOR LONG WIRES IN FIELD-PROGRAMMABLE GATE ARRAYS

by

Edmund Lee

B.A.Sc., University of Toronto, 2003

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF APPLIED SCIENCE

in

#### THE FACULTY OF GRADUATE STUDIES

Electrical and Computer Engineering

#### THE UNIVERSITY OF BRITISH COLUMBIA

June 2006

© Edmund Lee, 2006

Designers of field-programmable gate arrays (FPGAs) are always striving to improve the performance of their designs. As they migrate to newer process technologies in search of higher speeds, the challenge of interconnect delay grows larger. For an FPGA, this challenge is crucial since most FPGA implementations use many long wires.

A common technique used to reduce interconnect delay is repeater insertion. Recent work has shown that FPGA interconnect delay can be improved by using unidirectional wires with a single driver at only one end of a wire. With this change, it is now possible to consider interconnect optimization techniques such as repeater insertion.

In this work, a technique to construct switch driver circuit designs is developed. Using this method, it is possible to determine the driver sizing, spacing and the number of stages of the circuit design. A computer-aided design model of the new circuit designs is developed to assess the impact they have on the delay performance of FPGAs. Results indicate that, by using the presented circuit design technique, the critical path can be reduced by 19% for short wires, and up to 40% for longer wires.

## **Table of Contents**

| Abstract       |                                                     | ii       |

|----------------|-----------------------------------------------------|----------|

|                | ontents                                             |          |

| List of Tab    | les                                                 | <b>v</b> |

| List of Figu   | ıres                                                | vi       |

| Acknowled      | gements                                             | ix       |

| Chapter 1 l    | Introduction                                        | 1        |

| 1.1 M          | otivations and Objectives                           | 4        |

| 1.2 Co         | ontributions                                        | 5        |

| 1.3 Ov         | verview                                             | 6        |

| Chapter 2 l    | Background                                          | 7        |

| 2.1 FF         | PGA Overview                                        | 7        |

| 2.1.1          | Routing                                             | 9        |

| 2.1.2          | FPGA CAD Flow                                       |          |

| 2.1.3          | VPRx                                                |          |

|                | terconnect Design Theory                            |          |

| 2.2.1          | Deep-Submicron Interconnect                         |          |

| 2.2.2<br>2.2.3 | Interconnect Delay ModelsInterconnect Driver Design | •        |

|                | emarks                                              |          |

| Chapter 3      | Circuit Design of Unidirectional Interconnect       | 25       |

| 3.1 De         | esign of Unidirectional FPGA Switch Drivers         | 25       |

| 3.1.1          | Components of FPGA Switch Drivers                   |          |

| 3.1.2          | Switch Driver Design Goals                          | 32       |

| 3.1.3          | Switch Driver Design Parameters                     | 34       |

| 3.2 Ra         | apid Design Space Exploration                       | 36       |

| 3.2.1          | Analytical Delay Model                              | 36       |

| 3.2.2          | Design Space Sweeps                                 |          |

| 3.2.3<br>3.2.4 | Results                                             |          |

|                | ccurate Switch Driver Circuit Delay Modeling        |          |

| 3.3 At $3.3.1$ | Delay Modeling through Circuit Characterization     |          |

| 3.3.2          | Circuit Characterization Process                    |          |

| 3.3.3<br>3.3.4<br>3.3.5 | Characterization Results & Analysis  Delay Concatenation | 53         |

|-------------------------|----------------------------------------------------------|------------|

|                         | Verification of Delay Concatenation                      |            |

|                         | esign Parameter Search                                   |            |

| 3.4.1<br>3.4.2          | Circuit ConstructionSegment Length Sweep                 |            |

|                         |                                                          |            |

|                         | rcuit Design Results & Analysis                          |            |

| 3.5.1                   | Multiplexing Intervals                                   |            |

| 3.5.2                   | Distributed Buffering                                    | 04         |

| Chapter 4 (             | CAD Circuit Architecture Modeling and Evaluation         | 67         |

| 4.1 Go                  | oals of the CAD Circuit Evaluation                       | 67         |

| 4.1.1                   | Comments on Area Overhead                                | 68         |

| 4.2 Ex                  | perimental Methodology                                   | 69         |

|                         | rcuit Architecture Modeling                              |            |

| 4.3.1                   | Early Turn Modeling (ETM)                                |            |

| 4.3.2                   | Distributed Buffering.                                   |            |

| 4.3.3                   | Fast Paths                                               |            |

| 4.3.4                   | Multiplexer Delay Modeling                               | 82         |

| 4.3.5                   | Circuit Characterization for VPRx                        | 8 <i>3</i> |

| 4.4 Ex                  | perimental Results                                       | 88         |

| 4.4.1                   | Driver Designs Modeled in VPRx                           |            |

| 4.4.2                   | Benchmark Logic Circuits                                 | 90         |

| 4.4.3                   | Experiments                                              | 92         |

| 4.4.4                   | Critical Path Delay Results                              |            |

| 4.4.5                   | Turn Count Analysis                                      |            |

| <b>4.4.6</b> .          | Runtime                                                  | 104        |

| Chapter 5 (             | Conclusions and Future Work                              | 106        |

| 5.1 Fu                  | ture Work                                                | 107        |

| 5.1.1                   | Circuit Design                                           | 108        |

| 5.1.2                   | Future Work for CAD                                      |            |

| References              |                                                          | 111        |

| Appendix A              | A - Wire Models                                          | 114        |

| A Time T                | VDD- Daarda                                              | 117        |

## **List of Tables**

| Table 3.1 - Comparison of Multiplexer Architectures                    | 29  |

|------------------------------------------------------------------------|-----|

| Table 3.2 - Driver Design Parameters                                   | 35  |

| Table 3.3 - Typical Parasitics in Deep Submicron Process Technology    | 37  |

| Table 3.4 - Delay-Driven Results                                       | 40  |

| Table 3.5 - AreaDelay-Driven Results                                   | 41  |

| Table 3.6 - Characterized Sections                                     | 46  |

| Table 3.7 - Best Delay-per-millimeter for Various Sections             | 51  |

| Table 3.8 - Concatenation Verification Results (180nm)                 |     |

| Table 3.9 - Concatenation Verification Results (90nm)                  | 55  |

| Table 3.10 - Distributed Driver Design Results for 180nm               | 61  |

| Table 3.11 - Lumped Driver Design Results for 180nm                    | 61  |

| Table 3.12 - Driver Design Results for 90nm                            | 62  |

| Table 3.13 - Lumped Driver Design Results for 90nm                     | 62  |

| Table 4.1 - Lumped Driver Designs Used for Experiments                 | 90  |

| Table 4.2 - Distributed Driver Designs Used for Experiments            | 90  |

| Table 4.3 - Benchmark Circuit Array Sizes                              | 92  |

| Table 4.4 - Overview of Experiments                                    | 93  |

| Table 4.5 - Critical Path Results                                      | 94  |

| Table 4.6 - Turn Count Changes Due to Addition of ETM                  | 100 |

| Table 4.7 - Turn Count Changes Due to Addition of Fast Paths           | 101 |

| Table 4.8 - Turn Count Changes Due to Addition of Distributed Features | 104 |

## **List of Figures**

| Figure 1.1 - Routing Example of a Net in an ASIC                                         |

|------------------------------------------------------------------------------------------|

| Figure 1.2 - Routing Example of a Net in an FPGA                                         |

| Figure 1.3 - Example of FPGA Interconnect                                                |

| Figure 1.4 - Example of a Switch Driver Path Delay Profile                               |

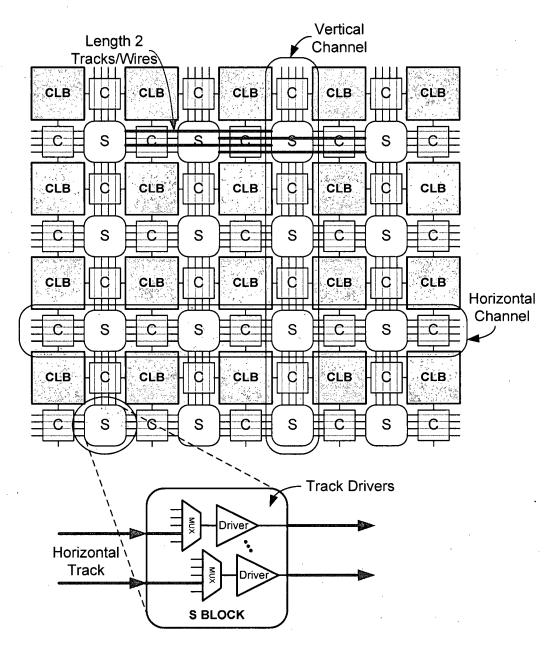

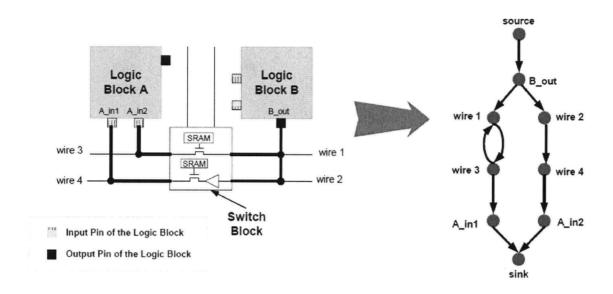

| Figure 2.1 - FPGA Architecture with Switch Block Detail                                  |

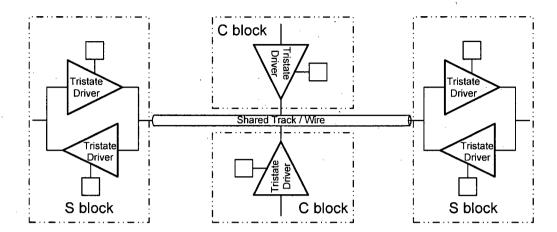

| Figure 2.2 - Representation of a Wire in a Bidirectional Architecture                    |

| Figure 2.3 - Tristate Driver Example 10                                                  |

| Figure 2.4 - Representation of a Wire in a Unidirectional, Single-Driver Architecture 11 |

| Figure 2.5 - Unidirectional Driver Example                                               |

| Figure 2.6 - Example of a Routing Resource Graph [6]                                     |

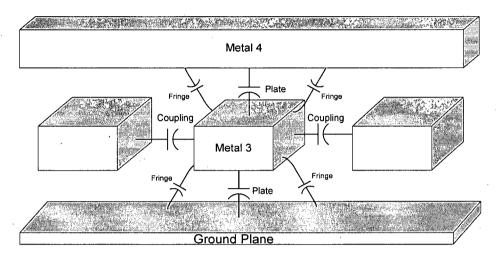

| Figure 2.7 - Deep-submicron Parasitic Capacitances                                       |

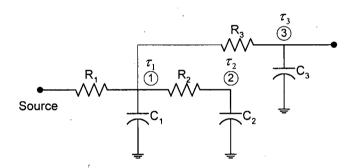

| Figure 2.8 - Elmore Delay Example [12]                                                   |

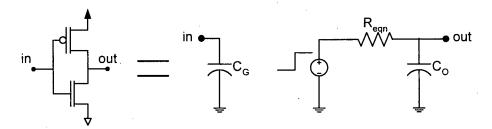

| Figure 2.9 - RC Model of a Buffer                                                        |

| Figure 3.1 - Architectural Location of FPGA Switch Drivers                               |

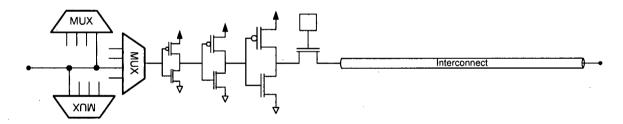

| Figure 3.2 - FPGA Switch Driver Components                                               |

| Figure 3.3 - Level-Restoring Circuit with 2:1 NMOS Pass Transistor Multiplexer 27        |

| Figure 3.4 - Binary Tree Multiplexer                                                     |

| Figure 3.5 - Flat Multiplexer                                                            |

| Figure 3.6 - 2-Level Multiplexer                                                         |

| Figure 3.7 - Multiplexer Fast Path                                                       |

| Figure 3.8 - Ubiquitous CMOS Buffer                                                      |

| Figure 3.9 - Driver Example                                                              |

| Figure 3.10 - Path Delay Profile                                                         |

| Figure 3.11 - Block Diagram Identifying Driver Design Parameters                         |

| Figure 3.12 - Elmore Model of Buffer & Wire Delay                                        |

| Figure 3.13 - Parameters Being Swept                                                     |

| Figure 3.14 - Design Space Sweep Pseudo Code 39                                          |

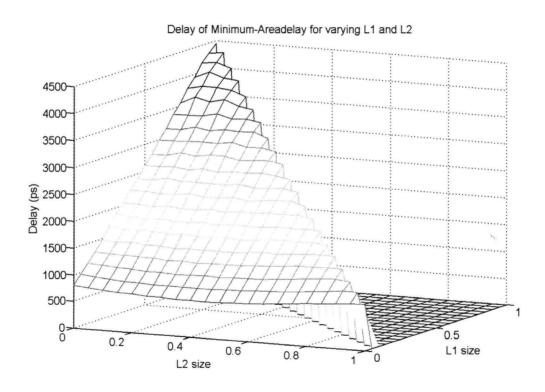

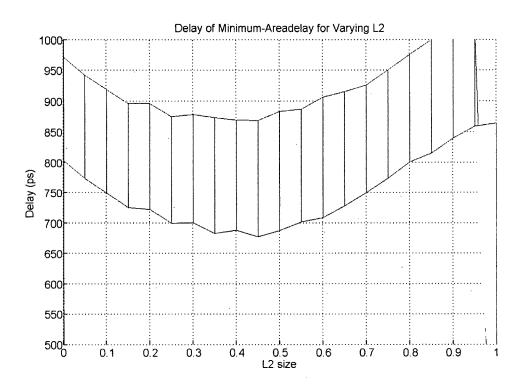

| Figure 3.15 - Areadelay-Driven Minimum-Delay Wire Distribution Plot for a 4mm                      |       |

|----------------------------------------------------------------------------------------------------|-------|

| Figure 3.16 - Areadelay-Driven Minimum-Delay Wire Distribution Plot for a 4mm Zoomed in on L2 Axis | Wire  |

| Figure 3.17 - Programmable Driver Example                                                          |       |

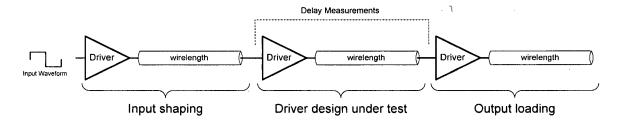

| Figure 3.18 - Testbench Configuration                                                              |       |

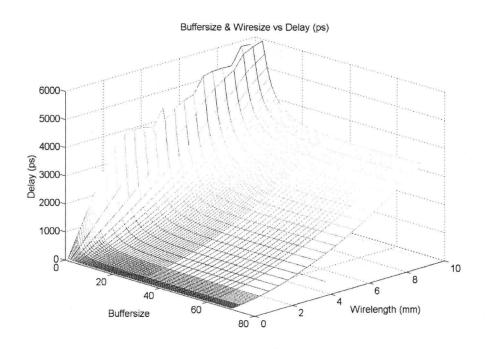

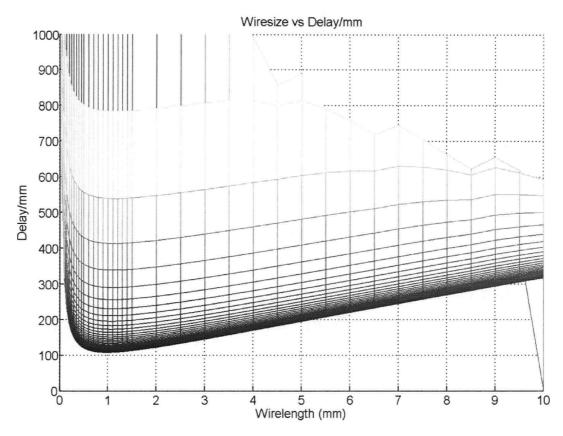

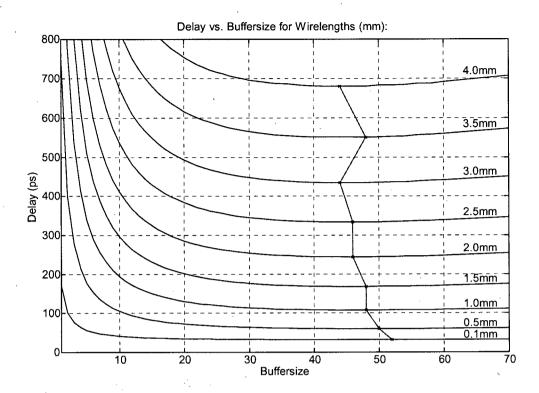

| Figure 3.19 - Delay vs. Buffer size and Wirelength for 180nm 1x1x nomux Design                     |       |

| Figure 3.20 - Delay vs. Wirelength for Different Buffer sizes for 180nm 1x1x no                    |       |

| Design - Wirelength Axis                                                                           |       |

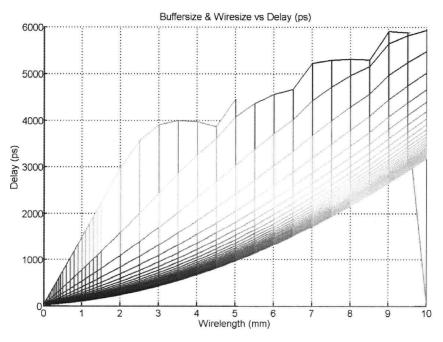

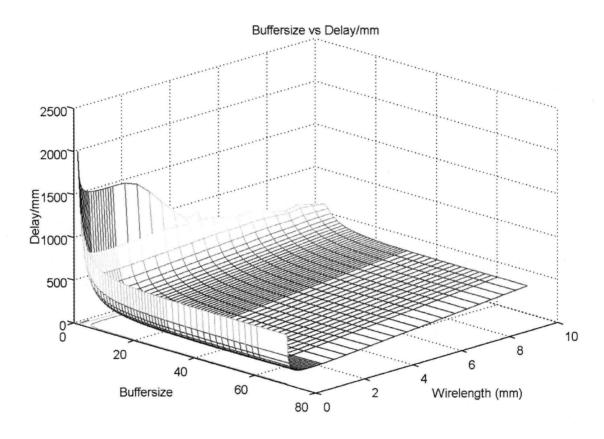

| Figure 3.21 - Delay/mm vs. Buffer size and Wirelength for 180nm 1x1x nomux De                      | esign |

| Figure 3.22 - Delay/mm vs. Wirelength for Different Buffer sizes for 180nm 1x1x no                 |       |

| Design - Wirelength Axis                                                                           | 50    |

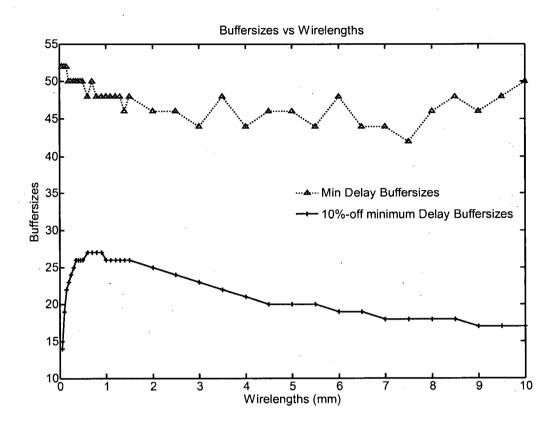

| Figure 3.23 - Buffer size Selection for 180nm 1x1x nomux                                           | 52    |

| Figure 3.24 - Buffer size Selections for 180nm 1x1x nomux Design                                   | 53    |

| Figure 3.25 - Circuit Concatenation Example                                                        | 54    |

| Figure 3.26 - Driver Construction Template                                                         | 56    |

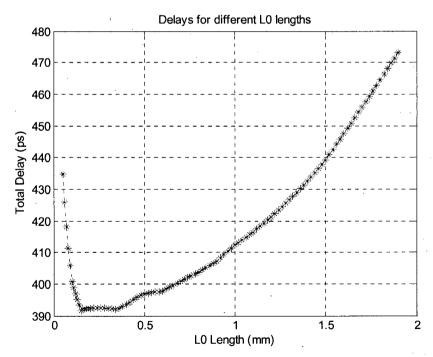

| Figure 3.27 - L0 Sweep for a 2mm Wire in 180nm 1x1x for N=3 Stages                                 | 57    |

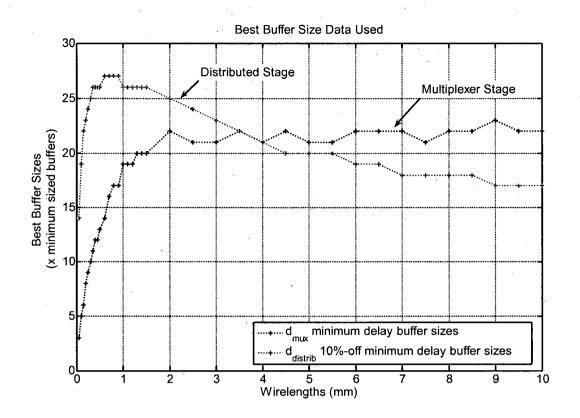

| Figure 3.28 - Buffer sizes Used for L0 Sweep in 180nm 1x1x                                         | 58    |

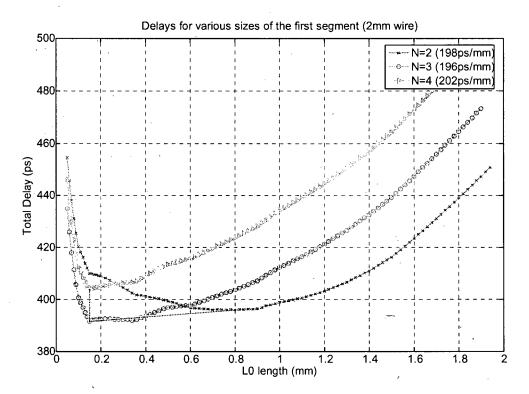

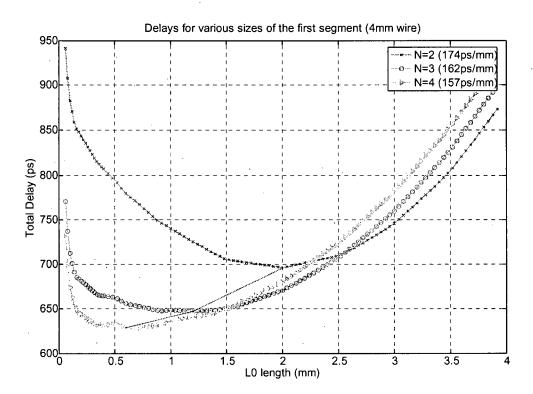

| Figure 3.29 - Multi-N L0 Sweep for a 2mm Wire in 180nm 1x1x                                        | 59    |

| Figure 3.30 - Multi-N L0 Sweep for a 4mm Wire in 180nm 1x1x                                        | 60    |

| Figure 3.31 - Multiplexing Intervals for various Technologies                                      | 63    |

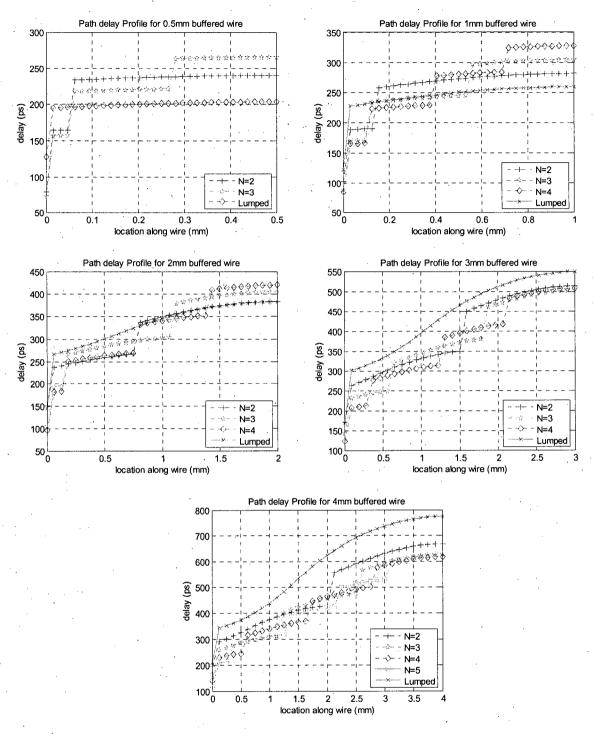

| Figure 3.32 - Path Delay Profile Plots for 180nm 1x1x for 1mm-4mm                                  | 66    |

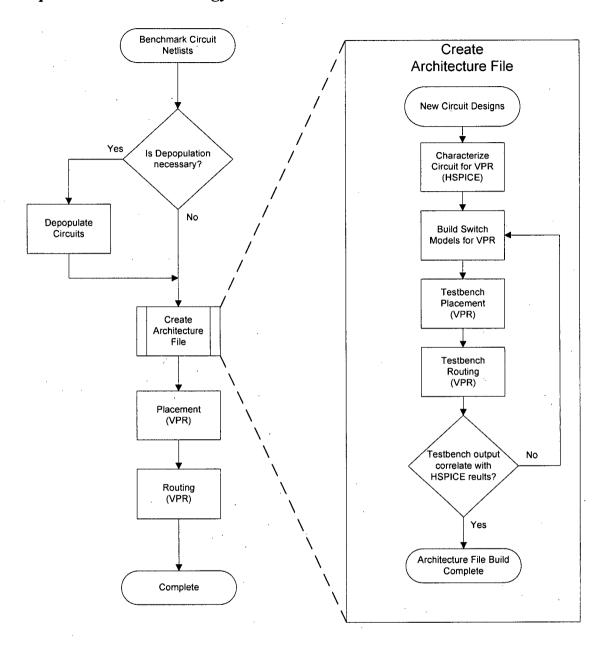

| Figure 4.1 - Experimental Methodology Flow                                                         | 69    |

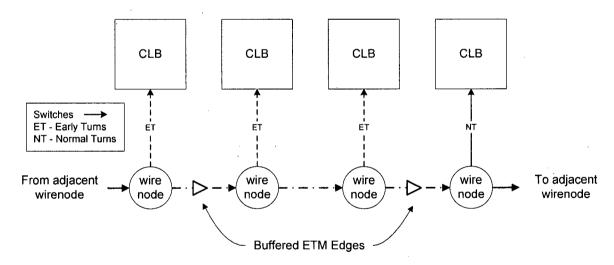

| Figure 4.2 - Early Turns                                                                           | 71    |

| Figure 4.3 - Original Routing Resource Graph of VPRx                                               | 73    |

| Figure 4.4 - Routing Resource Graph for VPRx with ETM Enabled                                      | 73    |

| Figure 4.5 - Wire Delay Calculation Example                                                        | 75    |

| Figure 4.6 - Routing Resource Graph with ETM and Distributed Buffers Shown                         |       |

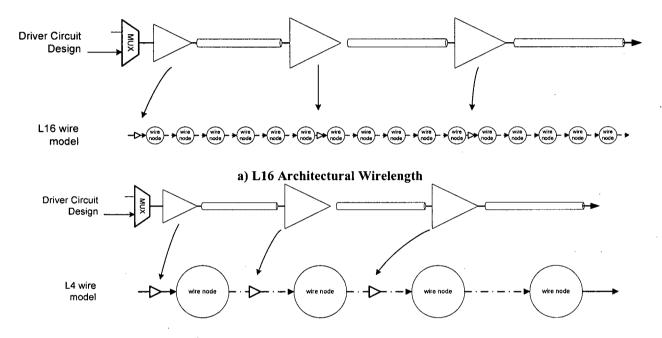

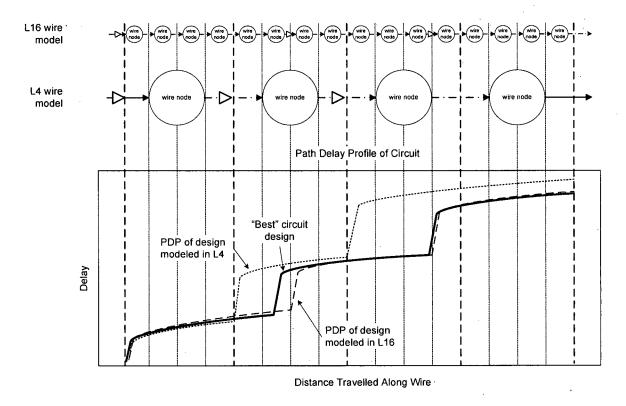

| Figure 4.7 - Modeling a Distributed Driver with Different Architectural Wirelengths                | 79    |

| Figure 4.8 - The Effect on the Path Delay Profile of Modeling Circuits with   | Different |

|-------------------------------------------------------------------------------|-----------|

| Architectural Wirelengths                                                     | 80        |

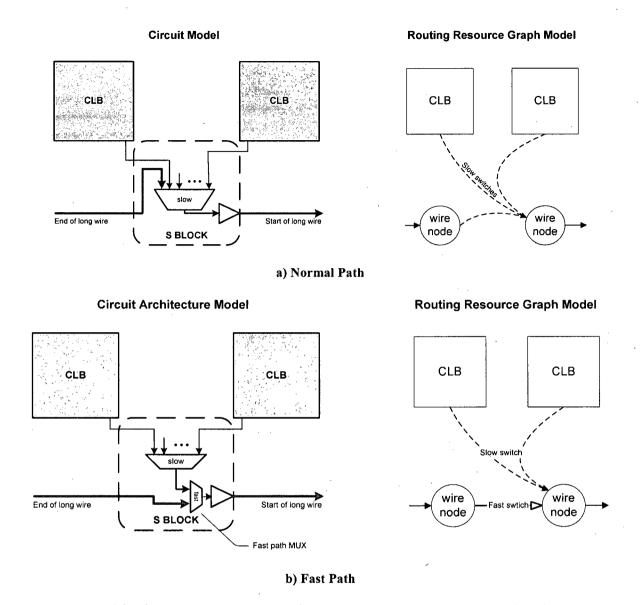

| Figure 4.9 - Signal Path through a Switch Block Using Normal or Fast Paths    | 81        |

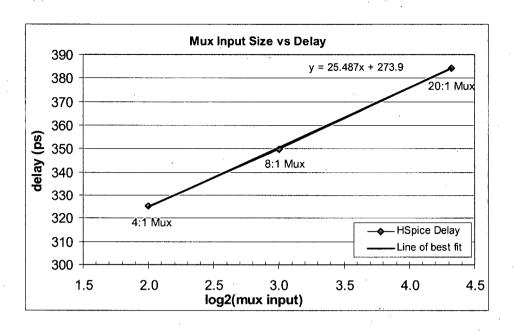

| Figure 4.10 - Multiplexer Fanin Delay with a 2mm Wire 180nm 1x1x              | 83        |

| Figure 4.11 - How Switch Circuit Delay is Modeled in VPRx                     | 83        |

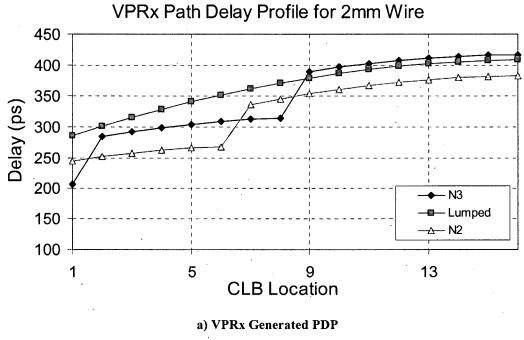

| Figure 4.12 - VPRx Path Delay Profile Extraction                              | 86        |

| Figure 4.13 - Path Delay Profiles for 2mm Wire in 180nm 1x1x                  | 87        |

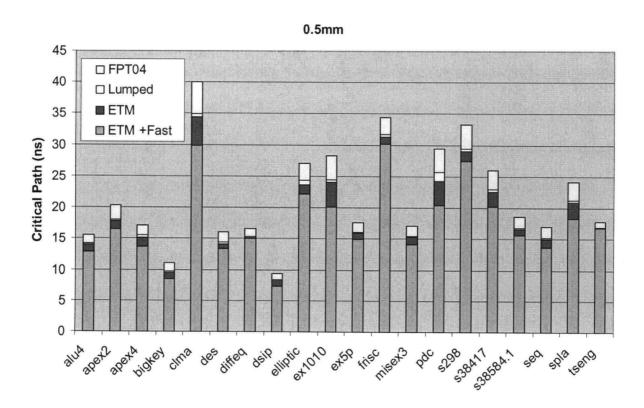

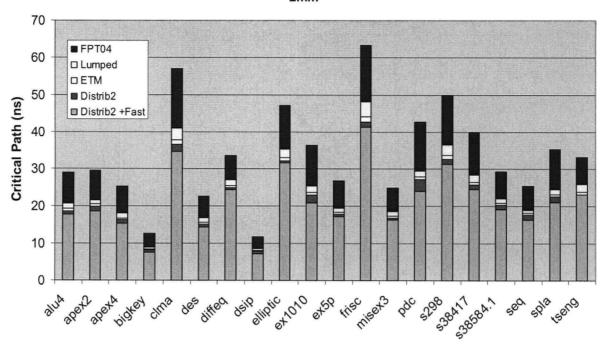

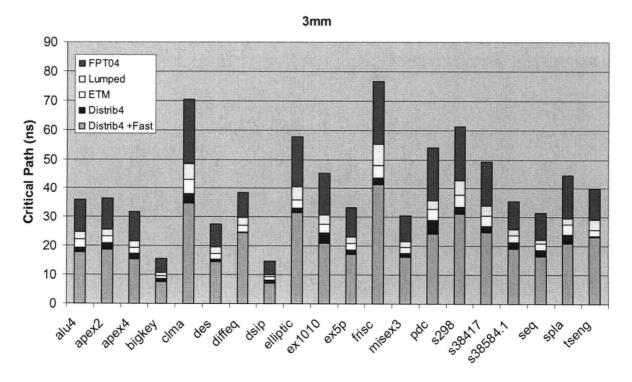

| Figure 4.14 - Delay Breakdown for 0.5mm Wire                                  | 97        |

| Figure 4.15 - Delay Breakdown for 2.0mm Wire                                  | 98        |

| Figure 4.16 - Delay Breakdown for 3.0mm Wire                                  | 98        |

| Figure 4.17 - Early Turn Routing Example for L4 Wires                         | 101       |

| Figure 4.18 - Routing Choices Due to Fast Paths with Early Turns in an L4 Arc | hitecture |

|                                                                               | 103       |

## Acknowledgements

I would to like thank my academic supervisors Dr. Guy Lemieux and Dr. Shahriar Mirabbasi for their advice, teachings and support throughout my graduate degree. I am very fortunate to have two professors who have taught me a great deal about research and the technical aspects of our field.

I would also like to thank the faculty and staff of the SOC lab for making the lab a wonderful academic home. Thanks for making me feel welcome and always offering assistance. My gratitude goes out to all the members of the FPGA and analogue research group for their many helpful insights and of course, excellent company.

I am grateful for the use of the Westgrid computing resources at UBC. Much of the research in this thesis was facilitated through the use of Westgrid.

Finally, I would like to thank my family for their constant support and enthusiasm.

## Chapter 1

## Introduction

Field-programmable gate arrays (FPGAs) are large integrated circuits comprised of blocks of programmable logic interconnected with programmable routing circuits. The demand for increasing their performance has driven FPGA designers in search of the latest process technologies. With each new technology generation, FPGAs have grown larger and increasingly dense, providing more logic with a smaller feature size. As one can expect, the wiring demands of these devices have also increased.

In deep submicron process technologies, interconnect has been identified as one of the most critical challenges facing integrated circuit designers [1]. In an FPGA, this is even more important, as 60-80% of the delay is caused by the interconnect [2]. Although extensive efforts have been made on interconnect optimization by means of repeater insertion for ASIC designs, few studies have investigated the optimization of circuit design for FPGA interconnect.

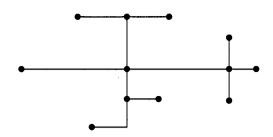

Techniques used in general ASIC interconnect optimization cannot be directly applied because the FPGA interconnect design problem is different in nature. Fortunately, due to its rigid structure and point to point nature, the topology of FPGA interconnect does not possess the complex fanout trees found in ASIC designs as seen in Figure 1.1.

Figure 1.1 - Routing Example of a Net in an ASIC

Instead, routing resources in an FPGA are made up of long straight wires which make up the predetermined paths of the routing resource architecture, as shown in Figure 1.2. This simplification is welcome as it considerably reduces the complexity of the circuit design problem. However, it is not without its own challenges.

Figure 1.2 - Routing Example of a Net in an FPGA

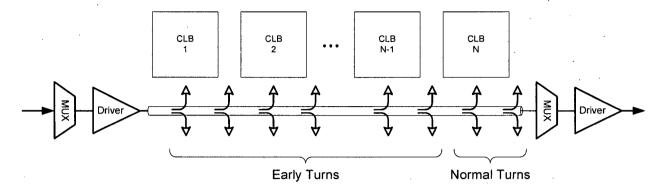

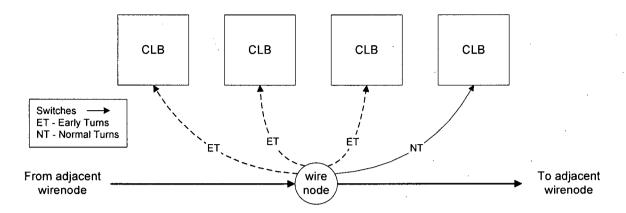

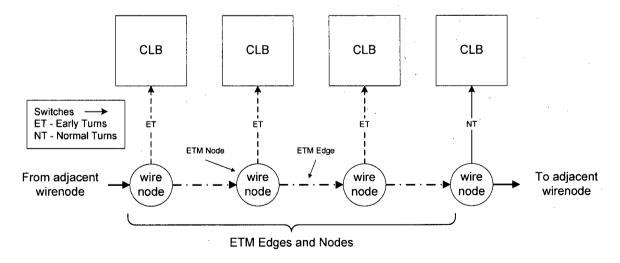

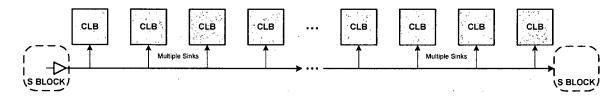

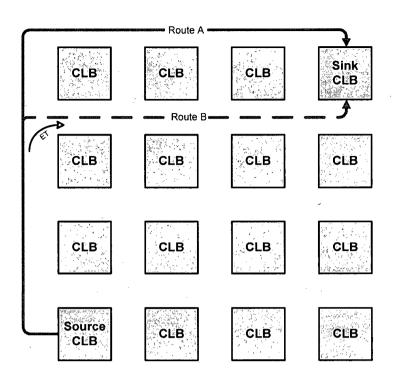

Like an ASIC, wires still fanout to numerous points in FPGAs, but whether or not a fanout is used in an FPGA interconnect is not known until *after* a user circuit is fully implemented. During operation, the path of a signal can occupy either a part or the entire length of a wire. Our experiments have demonstrated that 50% to 87% of signal paths in an FPGA routing solution leave the wire before arriving at the end. Such turns are called **early turns** (Figure 1.3). In order to assess early turn delays, this work will often consider the delay to several points along the interior of a wire. In general, these delays are referred to as the **midpoint delays** of a wire. To the author's knowledge, the concept of early turns and midpoint delay has not been previously examined in FPGA research.

The other major difference between FPGA and ASIC interconnect is that the FPGA interconnect must be programmable. This requirement introduces multiplexer circuits which can

adversely affect delay. The closed form models often used in the development of general interconnect optimization techniques are less accurate at modeling such circuits, making it difficult to apply the techniques from previous work on FPGAs. While closed-form analytical techniques are useful for rough approximations, they are not accurate enough to compare significantly different circuit implementations. This accuracy is vital to obtaining the best possible speed performance from FPGAs.

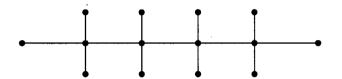

Figure 1.3 presents an example of an FPGA interconnect made up of wires, multiplexers and drivers. This research attempts to address the problem of wire delay in FPGAs by developing an accurate approach to design and evaluate interconnect driver circuits for FPGAs.

Figure 1.3 - Example of FPGA Interconnect

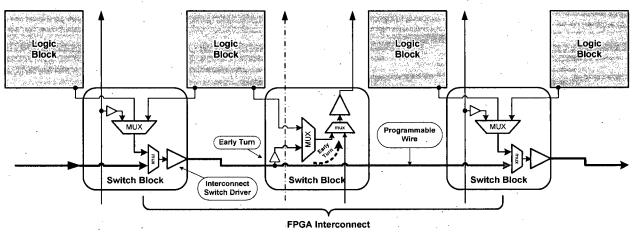

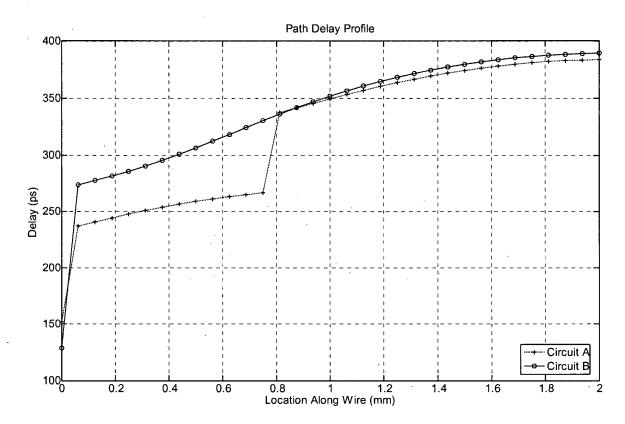

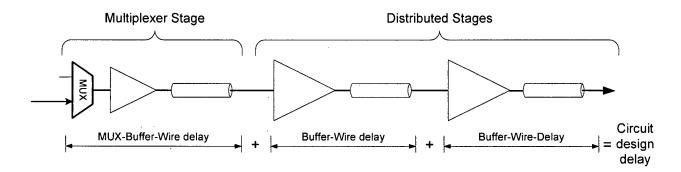

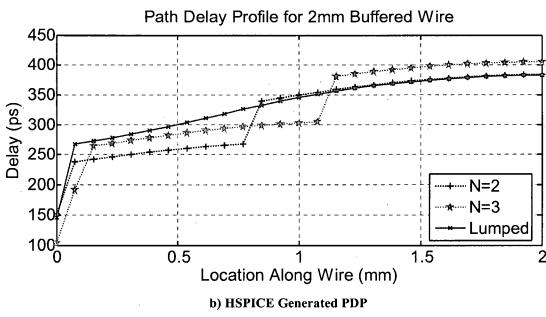

By taking advantage of the recent shift to FPGA architectures with a single driver per wire [3], it is possible to reduce midpoint delays, in addition to end-to-end (or **endpoint**) delay, to speed up performance in FPGAs through the use of distributed driver designs. As an example, Figure 1.4 presents a distributed driver design which could be used to implement the interconnect switch driver and the programmable wire in Figure 1.3. This sample driver circuit is made up of 2 distributed drivers of size B0 and B1. Using a **path delay profile** (PDP), the delay of the signal can be examined from its origin to the end of the wire, or to any point in between PDPs for two

designs, a lumped driver and a distributed driver, are shown in Figure 1.4. It can be seen that the midpoint delays of the first half of the wire are significantly faster than midpoint delays of the lumped-design PDP. This indicates that distributed driver design has the potential to improve the delay of the early turn shown in Figure 1.3.

Figure 1.4 - Example of a Switch Driver Path Delay Profile

Using modified CAD tools, it is possible to model the improvements from these circuit designs. Our results demonstrate that critical path delay due to these improved circuit designs can be reduced by up to 46%.

### 1.1 Motivations and Objectives

In the past, it was not possible to consider interconnect optimization techniques, such as repeater insertion, on FPGA wires because a long wire was shared by multiple tri-state drivers located at different points along the interconnect. In [3], it was shown that implementing directional wires with a single, lumped driver at the beginning of the wire improves both the

delay and area efficiency of an FPGA architecture. One way to take further advantage of directional wires that was not explored in [3] is to uniformly insert additional repeaters in order to reduce the delay of the wire.

The impact on FPGA performance from the use of additional repeaters is, as yet, unclear. Distributed buffering, has potential to improve not only endpoint delay, but midpoint delays as well. This is of particular benefit to FPGA designs as signals often turn off a wire before reaching the end. However, the only way to determine how much of a wire is used is by routing circuits on the FPGA using CAD tools. A large component of this research is to assess circuit design options using a CAD model which accurately considers the impact of early turns on critical path delay.

#### 1.2 Contributions

The contributions of this research are a circuit design methodology and evaluation of interconnect drivers for long wires in FPGAs to improve midpoint delays and end-to-end delay. Key findings of this work can be organized into three categories: circuit design, FPGA architecture and CAD modeling.

#### Circuit Design

- A circuit design methodology for FPGAs was produced which when given a fixed wirelength, can determine the number of buffers, size of buffers and spacing between buffers to achieve near-optimal delay.

- Using the circuit design approach, it is shown that distributed buffering is effective at reducing delay for wires, but only if the wires are of sufficient length (greater than 2mm in a 180nm technology with a minimally spaced and minimally sized wire)

#### FPGA Architecture

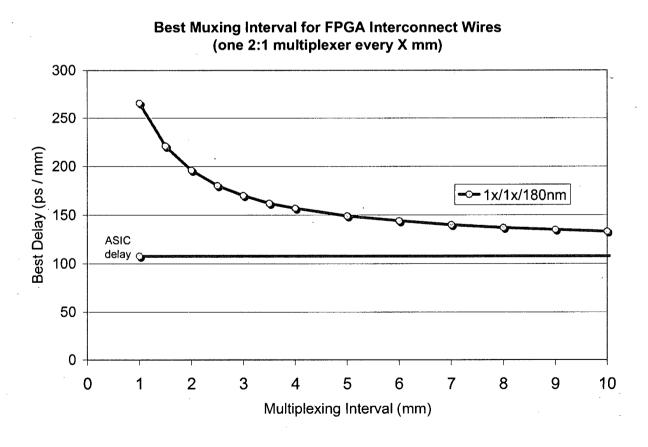

- Increasing the length of the wire between multiplexers (switch boxes) can improve the signal velocity and achieve near-ASIC interconnect speeds.

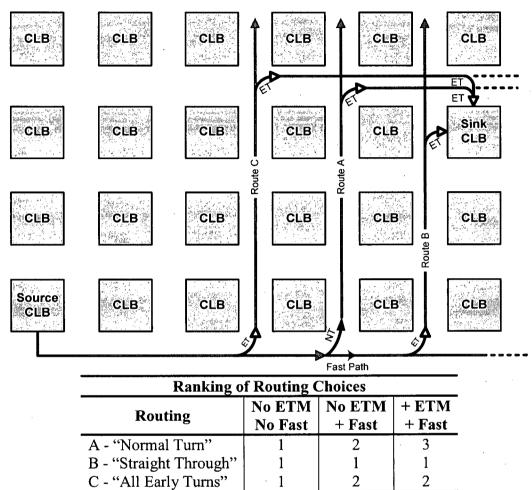

- Turns at the end of a wire (normal turns) are not critical. As fast paths and proper turn

modeling are introduced, the frequency of normal turns decreases. Also, 50-87% of turns

are before the end of the wire. These facts suggest that it maybe possible to remove or

reduce frequency of normal turns in the architecture.

- Fast paths through the switch block multiplexer were verified to improve critical path delay by up to 8% for short architectural wirelengths.

#### **CAD Modeling**

- FPGA CAD tools which are capable of improved modeling were developed and used to

evaluate proposed circuit designs. The improved modeling alone resulted in a 10%

improvement in critical path delay.

- Distributed buffering yields a modest delay improvement of about 3%.

#### 1.3 Overview

This thesis is composed of 5 chapters. Chapter 2 starts with an overview of FPGA architecture and CAD, and presents concepts of interconnect design theory. Chapter 3 presents the circuit design of FPGA interconnect drivers by providing detail on the development of a driver design methodology. Chapter 4 describes the modeling improvements incorporated into FPGA CAD tools which were used to assess the circuit designs produced in the previous chapter. Finally, Chapter 5 summarizes the conclusions drawn throughout the thesis and provides suggestions for future work.

### Chapter 2

## **Background**

In this chapter, the background information for this thesis is presented. The first half presents an overview of FPGA architecture and the supporting CAD flow. Particular emphasis will be placed upon the topics related to routing.

The second half of this chapter is focused on interconnect design theory. This section presents methods used for designing and optimizing interconnects in deep-submicron integrated circuits. Important fundamentals such as device parasitics, wire models and interconnect driver design techniques will be described in detail.

#### 2.1 FPGA Overview

An FPGA is an integrated circuit equipped with programmable logic and programmable routing resources. The reconfigurable elements allow an FPGA to be programmed after fabrication to implement virtually any digital logic function. The majority of FPGAs provide programmable logic using lookup tables (LUTs). An individual k-input lookup table, or k-LUT, is capable of implementing any k-input combinational logic function. In order to support sequential logic, flips flops are placed at the LUT output; this combination is referred to as a basic logic element (BLE). In most modern FPGAs, BLEs are grouped together in larger blocks called configurable logic blocks (CLBs) and are configured using SRAM memory elements.

Connectivity between logic blocks is achieved through the programmable routing resources. These resources are made up of metal tracks arranged in channels running vertically and horizontally across the FPGA. A channel is made up of a number of tracks, typically referred to as the **channel width**. A track is made up of wire segments of fixed length. These wire segments are placed end-to-end to span the length of the channel. The **architectural** or **logical length** of a wire is defined by the number of CLBs it spans. The physical length of a wire is equal to the logical length times the physical width of the CLB layout tile. Wires are connected to each other using **switch blocks**, and to the logic blocks using **connection blocks**.

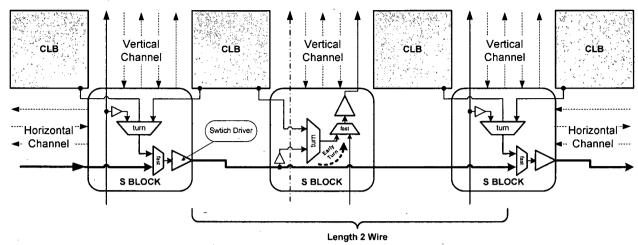

Figure 2.1 presents a typical mesh or island-style FPGA architecture which is assumed in this work. An example of an architectural length 2 wire, also denoted as L2, is indicated. The connection blocks are labeled as C blocks and the switch blocks are labeled as S blocks.

This work is focused on the transistor-level circuits inside the switch blocks which are located at the intersection of horizontal and vertical channels. These blocks contain multiplexers which connect tracks together across the intersection in predefined patterns [4]. The switch block contains large buffers that are used to drive the long metal traces which make up the wire segment. These buffers occupy considerable area in the switch block which represents a significant proportion (roughly 1/3) of overall FPGA area [4].

Figure 2.1 - FPGA Architecture with Switch Block Detail

#### 2.1.1 Routing

The functional design of these interconnect circuits is governed by the routing resource architecture. The routing resource architecture defines the precise connections and turns a signal may follow in the routing resource network. There are two main routing resource architectures: bidirectional and unidirectional.

#### **Bidirectional Architecture**

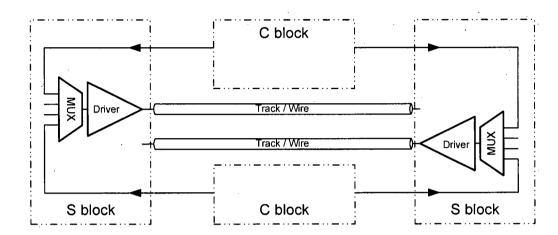

Figure 2.2 - Representation of a Wire in a Bidirectional Architecture

In a bidirectional routing network (Figure 2.2), a wire can transmit a signal in either direction. This approach provides a more flexible routing network which allows efficient use of available metal tracks. This means that the drivers of these wires must be tristate drivers so they can be disabled when not in use.

Figure 2.3 - Tristate Driver Example

A common approach to building tristate buffers in FPGAs is to use an NMOS passgate placed at the output of the regular driver (Figure 2.3) [5]. The use of this design confines the layout of the driver near to the point where the driver is connected to the wire. This means the driver design cannot be distributed along the wire. The output passgate affects both speed and area negatively by adding resistance to the output drive, producing a V<sub>T</sub> drop in the signal swing, and adding area to the circuit layout. Furthermore, since only one of the tristate drivers connected to

each wire can be enabled after programming, this approach causes a significant waste of active area.

#### **Unidirectional Architecture**

Figure 2.4 - Representation of a Wire in a Unidirectional, Single-Driver Architecture

In a unidirectional routing network (Figure 2.4), each track can only transmit data in one direction. This topology reduces the flexibility of the routing resources and suggests that the channels contain pairs of wires. Despite this restriction, work done in [3] demonstrates that this approach is more efficient in terms of area and provides improved delay over the bidirectional architecture.

Figure 2.5 - Unidirectional Driver Example

An additional restriction known as **single-driver** wiring ensures each wire is only driven by one driver, as opposed to multiple drivers as in the bidirectional architecture (Figure 2.5). This simplifies the routing network, eliminating the ability to connect at arbitrary points in the middle

of the wire. Instead, CLB outputs can only connect to the starting-points of nearby wires. A key benefit of this is that tristate operation is no longer required. Note, however, that the buffers which make up the driver no longer have to be in the physical vicinity of the source. Instead, they can be located at various positions along the length of the wire. In this research, it is shown that the relaxation of this constraint can produce an improvement in the delay of the wire segment, particularly when the wire is of sufficient length.

#### 2.1.2 FPGA CAD Flow

Before a user's logic circuit can be implemented on an FPGA it must under go certain processing steps known as the FPGA design flow to map the circuit onto an FPGA device. The FPGA CAD flow is comprised of 5 main steps: synthesis, technology mapping, clustering, placement and routing.

The first two steps in the CAD flow are synthesis and technology mapping. In these steps, the circuit is converted from a hardware description language into a network of FPGA-specific logic blocks which implement the functionality of the original circuit. After this point, logic blocks in the network are grouped together into clusters during the clustering step. This step controls the number of BLEs which are packed into a CLB and can be used as a rough method to manipulate the overall size of the circuit implementation on an FPGA. The following steps are placement and routing. Placement determines the locations for each CLB on an FPGA device. Routing uses detailed information of the FPGA routing resources to efficiently connect all the clusters together and implement the connections between logic blocks. In this work, particular emphasis is placed on developing the model of the routing resources used in the routing step.

#### FPGA CAD Experimental Methodology

The standard FPGA CAD experimental methodology involves running a suite of user circuits as benchmarks through the CAD flow multiple times, each time modifying the CAD step under study. In this work, the first 4 CAD flow steps are applied once on each benchmark circuit. The final step, routing, is applied multiple times. The first time the router runs, it searches for the lowest channel width which can successfully route the circuit design. Once this value is determined, it is increased by one complete set of directional tracks to produce a new larger channel width. The router is run again, but this time it only routes the design once using the new calculated channel width. This gives some flexibility to the router, which tends to improve the quality (delay performance) of the routing results.

#### 2.1.3 VPRx

For the place and route steps in the CAD flow, the academic tool VPR [6] is used. A heavily modified version, known as VPRx [3, 4], is used because it supports unidirectional wiring. Both VPR and VPRx use the same core routing and delay calculation algorithms. In the following two subsections, details on the routing resource graph and the VPRx delay model is provided.

#### **Routing Resource Graph**

VPRx models all routing paths in the FPGA using a routing resource graph. This data structure represents all possible connections which can occur in the FPGA routing network. In essence, the routing resource graph is a directed graph of wires, switches and pins at different locations on the FPGA. In the graph, wires and pins are represented as nodes while switches

<sup>&</sup>lt;sup>1</sup> The number of tracks in a set is equal to twice the architectural length. Further details can be found in [3].

between wires are represented as directed edges connecting nodes. Figure 2.6 presents the routing resource graph for a set of logic blocks connected by two wires. In this example, the bidirectional switch on wire 1 is modeled as a pair of directed edges, where the directional switch on wire 2 has only one edge.

Figure 2.6 - Example of a Routing Resource Graph [6]

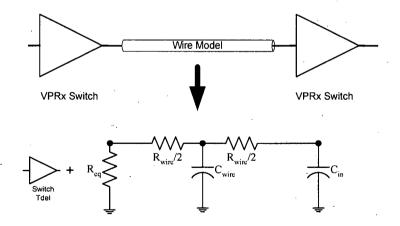

#### **Delay Calculation**

The routing algorithm used in VPRx is a modified version of the Pathfinder routing algorithm [6, 7]. This algorithm uses the Elmore delay calculation [8] as the primary metric to optimize the delay of routing paths. For this reason, it is important to ensure that the delay calculation is accurate. Fortunately, the routing resource graph is designed to facilitate the calculation of the delay of a signal path through the graph. Each node in the graph contains the capacitance and resistance of the wire being modeled. Similarly, each switch edge contains the delay of the switch, its input capacitance, output capacitance and its ability to drive an RC load in the form of an equivalent resistance. VPRx uses an incremental Elmore approach to calculate the delay [6].

The Elmore delay to a given node in an RC tree can be calculated by iterating over all the capacitances in the tree. For a signal path with no branches, this computation is straightforward. As the router expands along the routing resource graph, the delay of the next node is computed incrementally by adding the contribution of its parasitics to a running delay value. The equation used at each node is  $t_{del} = t_{del} + R_{upstream} \times C_{node}$ . The value of  $R_{upstream}$  is increased as the nodes are added to the routing solution. This approach works well for calculating the approach to the end of an RC tree where there are no fanouts to add extra capacitive loading. Greater detail on Elmore delay calculations will be described shortly in Section 2.2.2

### 2.2 Interconnect Design Theory

Interconnect design is an increasingly important consideration for integrated circuits built on deep-submicron process technologies. In this section, background on interconnect design is presented to provide the reader with an understanding of tools and techniques used to design circuits which drive interconnects. Topics such as interconnect models and interconnect driver design techniques are provided to ensure that the reader is familiar with the concepts in the subsequent chapters.

#### 2.2.1 Deep-Submicron Interconnect

Interconnect in deep-submicron process technologies has several important issues that affect the performance and design of high speed circuits. Problems such as signal integrity, inductive coupling, IR drop and electromigration are among the many growing challenges which face IC designers. However, the most prevalent challenge for interconnect design in deep-submicron design is signal delay.

The primary factors controlling interconnect delay are wire parasitics. The parasitics of interest, resistance (R) and capacitance (C), are physical properties of the wire. The resistance and capacitance of an interconnect act like an RC load in the signal path which causes propagation delay. The amount of resistance and capacitance is determined by the physical dimensions of the interconnect and the materials used.

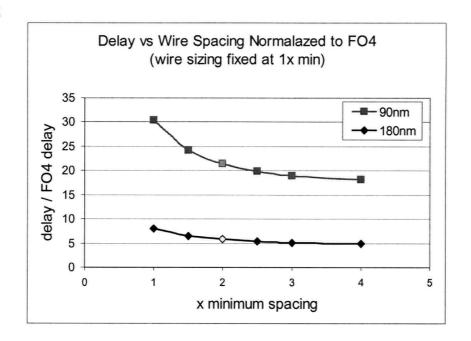

#### Parasitic Resistance

The resistance is determined from the cross-sectional area of the interconnect. A larger area implies a lower resistance. However, as technology shrinks, wires in nanometer technologies tend to be thinner than before. The overall effect is an increase in parasitic resistance for a minimum width wire. For example, the resistance of a minimum sized wire in 90nm is roughly twice the resistance of a minimum sized wire in 180nm.

Improved materials such as copper interconnect have been introduced in order to reduce interconnect resistance. At most, this provides a one-time improvement; the resistance continues to increase as wire geometries continue to shrink. In the meantime, the most straightforward solution is to increase the wire width in order to reduce resistance. Unfortunately, this is not always possible because an increase in wiring density is needed to keep up with the increase in logic density as transistors are scaled.

#### Parasitic Capacitance

Parasitic capacitance of an interconnect is caused by coupling with neighboring conductors. The amount of capacitance is related to the ratio of the conductive areas facing each other to the distance separating the two conductors. Figure 2.7 shows a typical construction of a deep-submicron interconnect with the most dominant parasitic capacitances labeled. Plate capacitance

is caused by the area at the top and bottom of the wire. In earlier technologies, this value was the dominant factor. However, with the narrower wires in nanometer technologies, the coupling capacitance has grown to be the major capacitance contribution.

Figure 2.7 - Deep-submicron Parasitic Capacitances

As with resistance, advanced materials such as low-k dielectric insulators are being introduced to lower the parasitic capacitances. However, in cases where a designer requires even lower capacitance, the easiest solution is to increase the distances between wires. With the increase in importance of coupling capacitance, wire spacing has become an even more effective tool at reducing delay. However, the benefits of increasing the wire spacing are limited by diminishing returns and can only be used at the cost of losing interconnect density.

#### **Inductance**

One important parasitic effect which is omitted in this research is that of inductive effects. Severe inductive effects include overshoots and undershoots in signal waveforms. These signal integrity faults can potentially manifest themselves as glitches or worse, as false transitions at the end of wires. Inductance is caused by electrical loops formed on integrated circuits that generate

corresponding magnetic fields. The interaction of magnetic fields on large integrated circuits can cause inductive interference which is very difficult to locate and solve.

In the past, inductance was not a serious concern since the resistive component of a wire dominated the impedance. However, now that the frequencies are increasing, the effect of the inductive component is growing.

In this work, inductance was ignored for several reasons. The first reason is that it is very difficult to predict the effective interconnect inductance because it depends strongly on the overall construction of the integrated circuit. Unlike capacitance, which is based strongly on neighboring features, inductive effects have a much larger spatial range. The second reason is that inductive effects do not severely affect the signal or propagation delay of interconnects. As shown in [9], the worst case inductance would cause an 8% reduction in the delay.

#### 2.2.2 Interconnect Delay Models

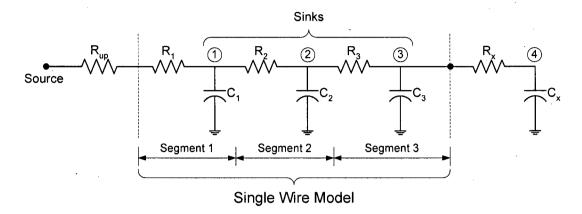

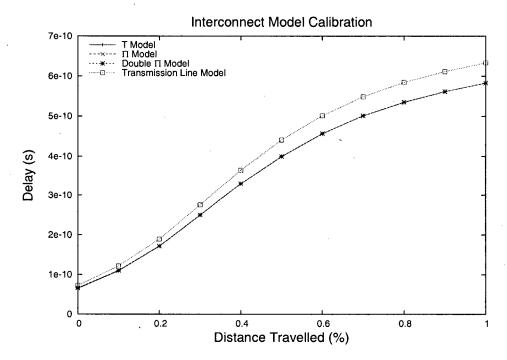

In order to design interconnect circuits one must be able to model the delay of a signal traveling along the wire. Interconnect delay models range from a simple lumped capacitance model to complex transmission line representations which are good at modeling high-order effects but are computationally intensive [10]. For the purposes of this research, a **distributed RC circuit model** is used with two computational models: Elmore delay and HSPICE delay.

#### **Elmore Delay**

There are many approaches used to compute the signal delay of a wire. Different methods trade off accuracy with computation speed. The fastest and most common approach is the Elmore delay [8]. This method offers high fidelity with a very fast runtime. Despite this, it is important to understand that the Elmore delay is only a first order approximation of the true

delay of an RC network. Other methods based on the Elmore delay offer improved accuracy with similar runtime [11]. However, these techniques do not have the ability to accurately model complex circuits such as pass transistors, level-restorers, or other active elements.

Elmore delay can be computed using a straightforward algorithm described in [12]. For any RC tree, the delay to node i can be computed using

$$\tau_i = \sum_k (C_k \times R_{ik})$$

$C_k$  is the capacitance at node k and  $R_{ik}$  is the sum of all the resistances from the source to node k that are **in common** with the path from the source to node i.

Figure 2.8 - Elmore Delay Example [12]

Figure 2.8 shows an example of a circuit from [12]. The Elmore delay to each node is calculated as follows.

$$\tau_{1} = R_{1}C_{1} + R_{1}C_{2} + R_{1}C_{3}$$

$$\tau_{2} = R_{1}C_{1} + (R_{1} + R_{2})C_{2} + R_{1}C_{3}$$

$$\tau_{3} = R_{1}C_{1} + R_{1}C_{2} + (R_{1} + R_{3})C_{3}$$

Using this method, the Elmore delay for a distributed RC model of a wire made up of N stages is expressed as  $RC\frac{N+1}{2N}$ , where R is the total resistance and C is the total capacitance. For large

values of N, this expression becomes  $\frac{RC}{2}$ . This can also be written as  $\frac{rcl^2}{2}$ , where r and c are values of resistance and capacitance per unit length and l is the length of the wire (R = rl, C = cl). This demonstrates that the delay of the wire is a quadratic function of its length.

#### **SPICE-Level Simulation**

In order to achieve high accuracy when modeling more complex driver circuits, it is necessary to use the HSPICE circuit simulator [13]. A SPICE simulator is capable of modeling a larger range of electrical effects while providing a higher level of confidence in the quantitative results in comparison to first-order approaches such as Elmore delay.

HSPICE is capable of modeling interconnects as transmission lines using a 2D filed solver. However, these approaches have lengthy runtimes. Instead, wires are modeled in HSPICE using numerous distributed RC stages which produce an error of less than 3% if proper care is taken [10]. The value of resistance and capacitance can be extracted from process technology documents and/or first characterizing the RC manually using the 2D field solver in HSPICE. Further details on interconnect parasitics are provided in Appendix A.

#### 2.2.3 Interconnect Driver Design

The delay of a wire is a quadratic function of its length. This delay can be reduced to a linear one by inserting additional buffers along the wire. Careful sizing and positioning of the buffers can further improve the delay. In this section, several approaches used to design buffers to improve interconnect delay are described.

#### **Driver Modeling**

In addition to modeling interconnect, it is important to be able to model delay of a driver circuit in order to determine the overall delay of the driver and interconnect. One common approach is to model a buffer using a resistance and capacitance. This method of using an RC time constant to represent a buffer, allows the delay of the buffer to be easily included in an Elmore delay computation.

Figure 2.9 - RC Model of a Buffer

In this approach, a buffer is modeled by an effective resistance or on-resistance, a gate capacitance and an output capacitance as shown in Figure 2.9. The gate capacitance is seen as a load on the previous stage, while the output stage is modeled as a step input driven through a resistance. This buffer model can be combined with an interconnect model to form an RC network which can be evaluated using the Elmore delay.

Using this simplistic method has some drawbacks, the most notable being that it cannot accurately model the effects of reduced signal swing or smaller input slew. Also, the accuracy of this model is strongly dependant on the value of the effective resistance. Since the on-resistance of a transistor in operation is not constant, deriving an accurate effective resistance can be tricky.

Although this approach is often used, there are other methods to model the delay of a buffer.

[14, 15] uses an alpha-law model [16, 17] which is based on the I-V curve of the transistor model.

Although this approach yields more accurate results, it involves complicated Laplace domain

calculations. For first-order calculations, use of the RC model was continued due to its simplicity and existing implementation in FPGA CAD tools.

#### **Repeater Insertion**

A common technique for improving delay performance on long wires is to use repeater insertion [10, 12, 18-20]. Conventionally, this involves placing single stage repeaters, at uniformly spaced intervals along the wire. One derivation of this approach is based on a careful application of the Elmore delay model as shown in [12]. Results show that the number of stages required to drive a wire of length l is

$$N = \sqrt{\frac{rcl^2/2}{R_{eqn}(C_J + C_O)(1+\beta)}}$$

The size of each buffer (relative to a minimum sized buffer) is

$$M = \sqrt{\frac{R_{eqn}}{C_G \left(1 + \beta\right)} \frac{c}{r}}$$

where r and c are the resistance and capacitance per unit length, respectively.  $R_{eqn}$  is the effective resistance of the driving transistor.  $C_G$  and  $C_O$  are the input and output capacitance of a minimum size buffer. Finally,  $\beta$  is the ratio of PMOS to NMOS sizes used in the buffer.

This repeater insertion technique is a simple solution to the interconnect problem. Unfortunately, the approach has some drawbacks. The resulting equations compute the optimum spacing and sizing of the repeaters based solely on the process characteristics. In practice, it should also depend upon the circuit preceding the interconnect. Furthermore, the optimum repeater size is usually quite large and unrealistic. Also, start driving this large load, a chain of cascaded inverters is typically used to drive the first stage [21]. However, the delay of this initial cascaded buffer arrangement can represent a significant fraction of the overall delay [22] and this

is ignored in the equations above. Previous work in [22] has shown that it is possible to integrate this cascaded buffer with the preceding logic, however, this approach does not apply well to FPGA switches due to the limited amount of active logic in the switch block.

An alternative design approach is non-uniformly inserted repeaters [22]. This technique uses buffers of increasing size to drive progressively longer wire segments. This particular work uses a geometric relationship for the sizes and wirelengths of successive segments. Although [22] offers a change from the classical uniformly-spaced buffer insertion approach, it still relies on a constrained solution space. In one component of this research, a more general design space will be considered to determine if further improvements can be gained from a fully non-uniform design.

#### Other Buffer Insertion Optimization Approaches

A substantial amount of work has been done on the development of interconnect circuit design optimization techniques. Many recent studies are focused on delay minimization using closed-form expressions [1, 9, 14, 18, 23-25], but there also exists some work which uses SPICE level analysis [22, 26]. In addition to delay, other important metrics such as power and area reduction are considered in [14, 18, 24, 27].

Although much of the previous work assumes CMOS buffers, there are other more exotic circuit architectures which can reduce interconnect delay [28-30]. Regardless of what circuit topology is used, it is clear that interconnect delay is a significant problem that will continue to be studied.

#### 2.3 Remarks

In this work, FPGA architecture and interconnect circuit optimization are combined. FPGA architecture introduces both constraints and simplifications to the general interconnect problem. The requirement of programmability places constraints on the circuit design and, in particular, it introduces complications with the delay model used in most closed-form expressions. However, the rigid and programmable structure of an FPGA allows the designer to avoid the more general problem of inserting buffers into interconnect trees. To this day, there has been an enormous amount of work done in both interconnect circuit optimization and FPGA circuit design. But to the best of our knowledge, no previous work has been attempted to combine the two concepts to produce optimized interconnects for FPGAs.

## Chapter 3

## **Circuit Design of Unidirectional Interconnect**

This chapter develops a circuit design technique for an FPGA switch driver. The first step is to revisit the problem of FPGA switch circuit design with a particular focus on designing for single-driver routing. From this discussion, design objectives and parameters are obtained. The next step is a rapid exploration of the design space which provides insights that facilitate the development of an accurate circuit delay modeling technique. Finally, this technique is used to determine the values of the design parameters which make up a complete FPGA switch driver design.

## 3.1 Design of Unidirectional FPGA Switch Drivers

In this section the problem of FPGA switch driver design is defined for use in a single-driver routing architecture. In the FPGA architecture shown in Figure 3.1, the switch driver for an architectural length 2 wire is represented as a part of the switch block. Although this is logically valid, the switch driver can be physically distributed along the entire wire. But before that can be discussed, it is important to investigate the design of the components which make up an FPGA switch driver.

Figure 3.1 - Architectural Location of FPGA Switch Drivers

#### 3.1.1 Components of FPGA Switch Drivers

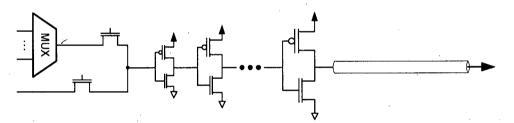

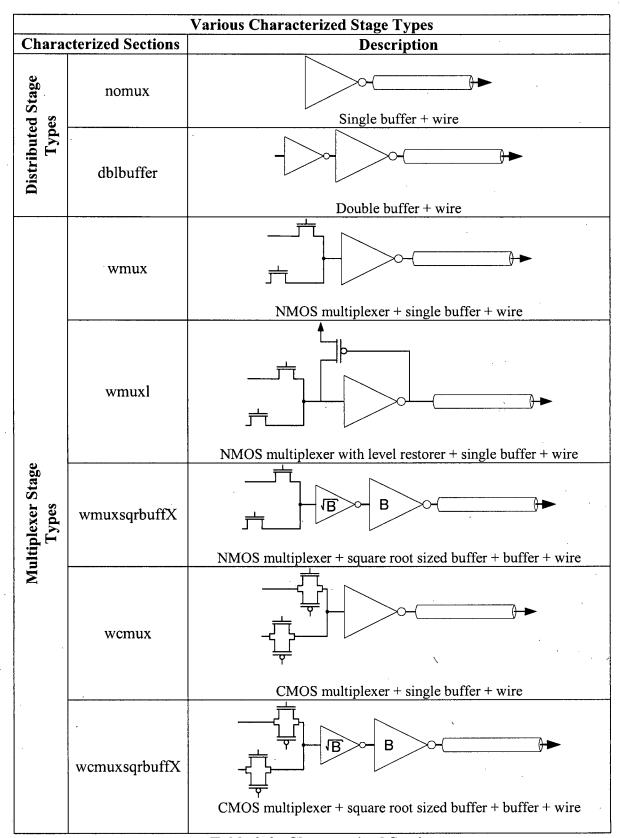

Figure 3.2 - FPGA Switch Driver Components

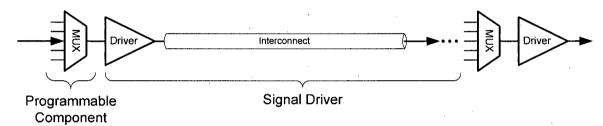

A block diagram of the switch driver is shown in Figure 3.2. A switch driver consists of a programmable component and a signal driving component. The programmable component allows a variety of sources to access the driver and is typically implemented using a multiplexer. The driver circuit transmits the signal down the wire to surrounding logic blocks and I/O pads. What follows is a description of some of the possible implementations of the multiplexer and the driver.

#### **Multiplexer Design**

The use of a multiplexer allows the device to select the signal to be driven from a variety of inputs of the switch block. Since multiplexers are prevalent throughout an FPGA, it is important

to appreciate that their circuits contribute to a large portion of the chip area. For this reason, area-efficient multiplexer designs are preferred in FPGA devices.

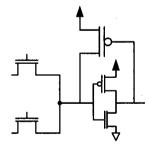

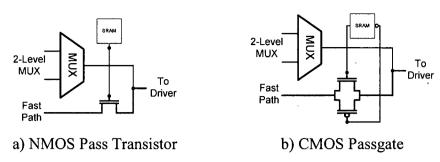

A multiplexer can be built using either active CMOS gates or passgates. The former uses CMOS logic gates to achieve full rail-to-rail signals. Although this approach is convenient, it is inefficient in terms of area and delay, especially as the fanin of the multiplexer increases. The latter design uses pass transistors or transmission gates to select the desired signal. This approach is commonly used because it provides good area and delay performance. Multiplexers using NMOS pass transistors have the smallest area, but suffer from reduced signal swing which causes downstream gates to operate slowly and leak at steady state. One solution to this problem is to use a level-restoring circuit, shown in Figure 3.3, integrated with the driver circuit. Unfortunately, this technique introduces non linear models into the circuit, making it difficult to use an analytical approach to compare with other circuits.

One compromise between area and delay is to use the CMOS transmission gate. This design is fast and provides a full swing signal to drive downstream gates. However, CMOS transmission gates require more than twice the area of an NMOS passgate due to the use of PMOS transistors.

Figure 3.3 - Level-Restoring Circuit with 2:1 NMOS Pass Transistor Multiplexer

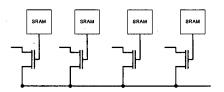

Once the passgate implementation is determined, the next step is to consider the multiplexer architecture. For multiplexers built using pass transistors, there are two common architectural choices.

Figure 3.4 - Binary Tree Multiplexer

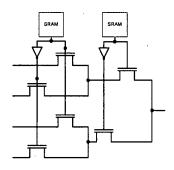

The first option is the fully-encoded binary tree structure. This design fully encodes the control signal input to make efficient use of the configuration RAM and reduce the area overhead. The signals are selected using a binary tree structure as shown in Figure 3.4. For an N-input multiplexer of this architecture, the number of configuration RAM bits used is equivalent to the number of levels in the tree, hence  $\lceil \log_2 N \rceil$ . The signal delay in this design is proportional to the number of levels squared, or  $\lceil \log_2 N \rceil^2$ .

Figure 3.5 - Flat Multiplexer

An alternative approach is the flat, decoded multiplexer as in Figure 3.5. This architecture uses one configuration RAM bit and one passgate for each signal input. This design requires the largest SRAM area overhead, but limits the delay for any signal to that of one passgate plus the loading effect of additional junction capacitance from neighboring transistors. The number of transistors used in this design is equal to the number of signal inputs.

| Comparison of Multiplexer Architectures (N = fanin of MUX) |                                        |                             |                        |  |  |  |

|------------------------------------------------------------|----------------------------------------|-----------------------------|------------------------|--|--|--|

| Parameter                                                  | Fully Encoded<br>Multiplexer           | Flat Decoded<br>Multiplexer | 2-Level<br>Multiplexer |  |  |  |

| Delay Levels                                               | $\lceil \log_2 N \rceil$               | 1                           | 2                      |  |  |  |

| Loading (junction capacitance)                             | $\lceil \log_2 N \rceil$ (distributed) | N-1<br>(lumped)             | $\sqrt{N} \times 2$    |  |  |  |

| Configuration RAM                                          | $\log_2 N$                             | N                           | $2\sqrt{N}$            |  |  |  |

| Passgates Required                                         | 2N-2                                   | N                           | $(N+\sqrt{N})$         |  |  |  |

Table 3.1 - Comparison of Multiplexer Architectures

Figure 3.6 - 2-Level Multiplexer

A combination of the aforementioned designs can be seen in the Stratix II architectural paper [31]. This approach uses a combination of encoded and decoded designs to produce a tree with multiple branches. This design attempts to reduce the delay by limiting the number of levels a signal must pass to two levels. For a 16:1 multiplexer, this design requires about half the amount of configuration RAM cells as the flat decoded multiplexer but 25% more passgates. Since configuration RAM is usually quite large in comparison to a passgate, this design can still result in area savings. Table 3.1 compares the characteristics of the three multiplexer designs.

For this work, the two-level passgate architecture was selected because it reduced delay without incurring a large increase in area. Also, the delay of this design remains fairly linear with increasing fanin due to its constant depth. This linearity simplifies modeling of the multiplexer delay during FPGA architectural explorations where the fanin depends on the channel width.

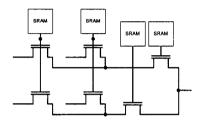

Figure 3.7 - Multiplexer Fast Path

# Multiplexer "Fast Path"

Regardless of which multiplexer design is used, it will always be a significant source of delay in the circuit. To further exacerbate this problem, directional routing architectures require multiplexers which are larger than those found in bi-directional routing architectures. The multiplexers used have large fan-in (e.g., 20:1, 40:1) resulting in large propagation delays. In order to avoid this, an isolated path called the "fast path" was created. Also referred to as the "fast input" in [31], this path allows one signal to bypass the majority of the multiplexer inputs and arrive at the driver input after going through one passgate as shown in Figure 3.7. When the fast path is taken, the remainder of the multiplexer design can be ignored since it is shielded by the disabled passgates. Since it is expected that this is the common case for high-speed signals that must cross the chip, the buffer design will be optimized for this fast path by reducing the multiplexer structure to a simple 2:1 multiplexer.

# **Multiplexer Design Results**

The delay of three multiplexer implementations (NMOS pass transistor, NMOS pass transistor, with level restorer, and the CMOS transmission gate) were compared using HSPICE. Circuit simulations of the fast path were performed using a 2-1 multiplexer driving a single buffer of various sizes. Sweeping the size of the passgate transistors yielded minimal

improvements for the end-to-end delay of the multiplexer-buffer-wire path, as a result minimumsized transistors were used in order to conserve area.

Simulation results also confirmed that the CMOS transmission gate yielded the fastest delay. In addition, this option offers full signal swing, eliminating the need for any level restoring circuitry. Because of this, a CMOS transmission gate was used with the 2-level multiplexer and fast path. The final design is shown in Figure 3.7b.

# **Driver Designs**

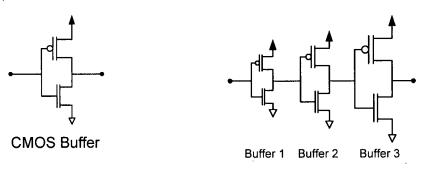

The component following the multiplexer is the driver circuit. The purpose of this circuit is to "drive" the multiplexed signal down the wire. Although there are many ways to implement a signal driver, our focus is restricted to designs using CMOS inverters, also referred to as a buffer or a repeater. The standard CMOS inverter is built with one NMOS and one PMOS transistor (Figure 3.8). The PMOS to NMOS transistor size ratio is dependant on the input signal and therefore related to the multiplexer design. For example, a buffer following an NMOS pass transistor multiplexer will require a much larger NMOS transistor to sense the weak '1' input signal [4]. In this work, a 2:1 PMOS to NMOS sizing ratio is assumed for simplicity and because weak input signals do not occur with the CMOS transmission gate.

Figure 3.8 - Ubiquitous CMOS

Figure 3.9 - Driver Example

#### **Buffer**

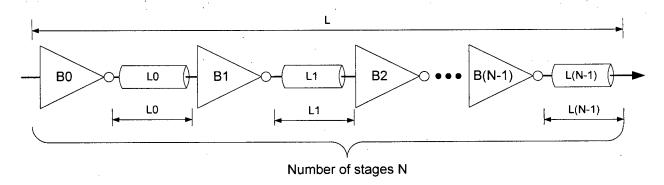

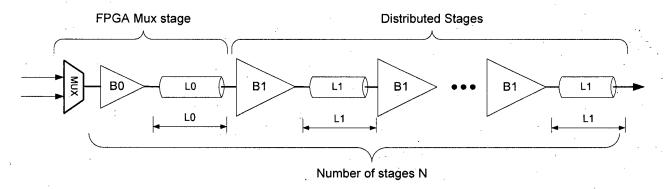

A driver is made up of one or more buffers connected in series as shown in Figure 3.9. The buffers in this design are progressively larger in size. Since physical distance between the buffers is very small, it is referred to as a "lumped" driver design. An alternative approach is to space the buffers apart along the length of wire they must drive. This is referred to as a "distributed" driver design. The key unknowns regarding driver design are the transistor sizes of the buffers, the number of buffers, and the distance between buffers. Within a driver, the combination of a buffer and a wire is referred to as a "stage". Often, the length of a wire following a buffer is used to indicate the spacing between buffers, and it is also referred to as the wirelength of the stage.

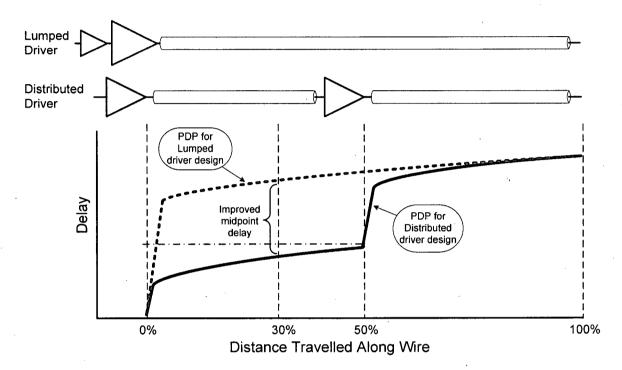

#### 3.1.2 Switch Driver Design Goals

As mentioned in the background, the elimination of tristates allows single-driver interconnect architectures to use distributed buffering and subsequently, to consider midpoint delay as well as endpoint delay.

#### **Distributed Buffering**

Conventional VLSI practices suggest that distributed drivers are the best design for minimizing end-to-end delay of an interconnect [10]. However, in order for a distributed driver to become beneficial, the wire must be long enough and resistive enough to take advantage of

the additional repeaters. One of the goals of this work is to determine how long must a programmable interconnect be, before distributed buffering can benefit an FPGA.

#### **Modeling Early Turns**

Another benefit of distributed drivers for FPGAs is the improvement of early turn delays. As mentioned in the introduction and shown in the following Chapter, place and route results demonstrate that early turns occur very often in directional FPGAs with long wires. Intuitively, distributed driver designs can offer improved early turn delay since all the inverters are not lumped at the front of the wire. However, in order to guarantee this, an ideal design would have to improve delay to all points along the wire, in addition to the endpoint delay.

The delay to all points along a wire is shown in a "path delay profile" (PDP). This metric will be used as a qualitative tool to determine if a circuit design can offer improved early turn delay. For example, two PDPs are shown in Figure 3.10. Both circuits have similar delay to the end of the wire. However, the signal of circuit A arrives before the signal of circuit B for the majority of locations along the length of the interconnect, particularly at points between 0 and 0.75mm. This suggests that circuit A would yield better performance in an FPGA architecture if there are turns before 0.75mm.

Figure 3.10 - Path Delay Profile

In summary, the circuit design goals of the switch driver are to take advantage of unidirectional interconnect architectures to optimize for midpoint and end-to-end delay. In particular, this work will attempt to determine if distributed driver designs are beneficial for use in FPGA interconnect. It will identify what wirelengths benefit in end-to-end delay from a distributed driver approach and using the PDP, identify designs that improve early turn delays.

# 3.1.3 Switch Driver Design Parameters

This section summarizes the key design parameters of the circuit design problem. The design parameters are listed in Table 3.2. Figure 3.11 presents a block diagram indicating the various design parameters.

| Driver Design Parameters   |             |                                                                                                                            |  |  |

|----------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                  | Description |                                                                                                                            |  |  |

| Total Wirelength           | L           | Length of interconnect. Architecturally, this is the distance between multiplexers (typically in mm)                       |  |  |

| Number of Driver<br>Stages | N           | Number of buffer-wire stages which make up the total interconnect, including the programmable component as the first stage |  |  |

| Buffer Sizing              | Bi          | Size of the buffer <i>i</i> , normalized to a minimum sized buffer                                                         |  |  |

| Buffer Spacing             | Li          | Length of wire following buffer <i>i</i> (typically in mm or in % of L)                                                    |  |  |

**Table 3.2 - Driver Design Parameters**

Figure 3.11 - Block Diagram Identifying Driver Design Parameters

#### **Interconnect Characteristics**

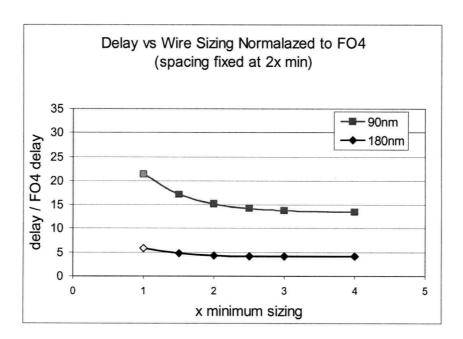

Thus far, the geometry issues of interconnect have not been discussed. In most FPGAs, long interconnects are manufactured on mid-level layers (e.g., metal 3 in a 6 metal process). Therefore this work assumes that metal layer 3 is used to build the wires. Two combinations of wire widths and spacings were considered for 180nm and 90nm process technologies: 1x minimum width/1x minimum spacing (denoted as 1x1x) and 2x minimum width/2x minimum spacing (2x2x). Results are presented for designs built using 180nm 1x1x and 90nm 2x2x interconnects. These combinations are chosen because they represent the range of delays achievable, as 180nm 1x1x is the slowest and 90nm 2x2x is the fastest.

# 3.2 Rapid Design Space Exploration

By developing a model based on the design parameters from the previous section, the general problem of sizing and placing buffers on a wire can be explored. A quick-to-compute Elmore model is created and used to rapidly explore the design space of a system with three buffers. The results from this exploration suggest that distributed buffering can improve results at certain wirelengths. Furthermore, the results indicate that the design space is fairly insensitive to small changes in buffer size and wirelength, which allows for some flexibility in choosing an optimal design.

## 3.2.1 Analytical Delay Model

In this study, the design parameters will be exhaustively swept using a simple Elmore delay model. The difference between this exploration and previous work [14, 22, 23, 32] is that the search here does not impose relationships between subsequent inverters. Most approaches constraint the size of successive inverters to be equal or related to one another based on a geometric series. Unfortunately, by not introducing any constraints, the design space becomes very large and unwieldy. To reduce the dimensionality of the design space, the number of stages is restricted to 3 stages as in previous FPGA switch driver designs [3, 33]. Another constraint is that the size of the first inverter is fixed to minimum. This is done because the Elmore model approach does not take into account the input capacitance of the first gate. Also, using a smaller sized buffer will minimize the impact of loading on the preceding circuitry.

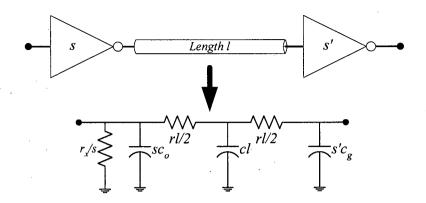

The delay model uses standard VLSI techniques [12] presented in the background. Figure 3.12 shows a buffer of size *s* driving a wireload of length *l* and a downstream buffer of size *s* '.

Figure 3.12 - Elmore Model of Buffer & Wire Delay

The Elmore delay equation for the wire has the time constant:

$$\tau = \frac{r_x}{s} \left( c_o s + c l + c_g s' \right) + \frac{r c l^2}{2} + \left( r l \times c_g s' \right) \tag{1}$$

where r and c are the resistance and capacitance per unit length of a wire,  $c_o$  and  $c_g$  are the output and input capacitance of a minimum sized buffer and  $r_x$  is the equivalent resistance of a minimum-sized transistor. Although the value of  $r_x$  depends on the type of transistor used, most approaches do not distinguish the value. In this work, the Elmore-delay computation code distinguishes between a rising and falling scenario and takes the average of the delays. Table 3.3 lists typical values of the parasitics in a 180nm process technology.

| Parasitics in 180nm Process Technology |                                                        |                     |  |  |  |  |

|----------------------------------------|--------------------------------------------------------|---------------------|--|--|--|--|

| Parameter                              | Description                                            | Typical Values [12] |  |  |  |  |

| $c_o$                                  | Output capacitance                                     | 1 fF/μm             |  |  |  |  |

| $c_{g}$                                | Gate Capacitance                                       | 2 fF/ μm            |  |  |  |  |

| c                                      | Wire capacitance per unit length (min width & spacing) | 0.1-0.25 fF/μm      |  |  |  |  |

| r                                      | Wire resistance per unit length (min width)            | 125-300 mΩ/μm       |  |  |  |  |

| $r_p$                                  | Equivalent resistance of a PMOS transistor             | 30 kΩ/μm            |  |  |  |  |

| $r_n$                                  | Equivalent resistance of an NMOS transistor            | 12.5 kΩ/μm          |  |  |  |  |

Table 3.3 - Typical Parasitics in Deep Submicron Process Technology

The total delay through the chain of inverters is calculated by summing up the delay through all three stages. Typical Elmore delay modeling applies a  $ln(2) \cong 0.69$  factor to  $\tau$  to calculate 50% propagation delay, however, it was found that a 1.0x factor was more accurate due to the

non-ideal (ramp) inputs used to drive the circuits [12]. With this model, the delay of a three-stage driver for any given combination of inverter sizes, inverter spacings and total wirelength can be calculated.

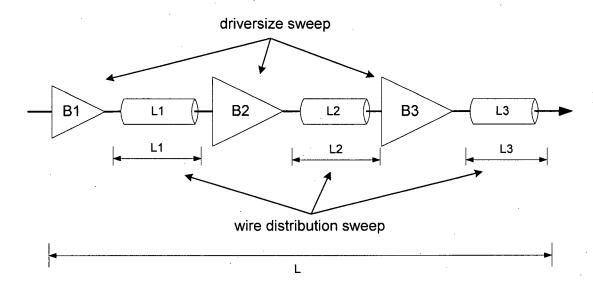

Figure 3.13 - Parameters Being Swept

## 3.2.2 Design Space Sweeps

Using the general delay model, a set of nested sweeps was used to search the design space for a variety of wirelengths. The inner sweep is a driver-size sweep and the outer sweep is a wire-distribution sweep. The driver-size sweep calculates the delay for all possible combinations of a set of predetermined buffer sizes. From the sweep, the buffer sizes which produce the smallest delay and the smallest area-delay product can be determined. Similarly, the wire-distribution sweep generates the best buffer spacing configuration for each wirelength setting. The pseudocode for this exhaustive search is shown in Figure 3.14. This pseudo-code was implemented in Matlab. The calculate\_delay\_of\_() function computes the Elmore delay as described in the previous section (3.2.1).

```

driver_sizes_weep(wirelengths_array [w1 w2 w3]) {

/* mindelaymetric can represent delay or areadelay */

mindelaymetric = largenumber;

for all b1sizes [b1] {

for all b2sizes [b2]

for all b3sizes [b3]

/*build circuit with buffersizes [b1 b2 b3]

and wiredistributions [w1 w2 w3] */

circuit = build_circuit( [b1, b2, b3], [w1 w2 w3] );

delaymetric (b1,b2,b3) = calculate_delay_of( circuit );

/* Grab the best design */

if (delaymetric (b1,b2,b3) < mindelaymetric) {

mindelaymetric = delaymetric (b1,b2,b3);

bestcircuit = circuit;

return bestcircuit;

wire_distribution_sweep(wirelength) {

/* mindelaymetric can represent delay or areadelay */

mindelaymetric = largenumber;

for all L1lengths [L1] {

for all L2lengths [L2] {

L3 = wirelength - L1 - L2;

circuit = driver_sizesweep([L1 L2 L3])

delaymetric (L1,L2) = calculate_delay_of( circuit );

/* Grab the best design */

if (delaymetric (L1,L2) < mindelaymetric)

delaymetric = delay (L1,L2);

bestcircuit = circuit;

return bestcircuit;

```

Figure 3.14 - Design Space Sweep Pseudo Code

#### 3.2.3 Results

Table 3.4 presents the best wire distribution, buffer sizes and resulting delays for wirelengths ranging from 1mm to 16mm in a 180nm process using wires with 1x minimum spacing and 1x minimum width. The best wire distribution is shown as three values which represent the length of wire following buffer 1, 2 and 3, respectively, these values are normalized to the total wirelength and sum to 1.0. Similarly, best buffer sizes are listed as the size of buffer 1, 2 and 3, respectively. The delay for the best design is shown in column 4 and the delay for the corresponding lumped design is shown in column 5. The final column indicates the performance

difference between the two designs. For example, the 2.5mm design is made up of 1x, 7x and 38x buffers followed by wirelengths which make up 0%, 15% and 85% of the total wirelength, respectively. This design has a delay of 379.8ps. In comparison, the best 3 stage lumped design for a 2.5mm design would have a delay of 382.3ps, approximately 1% slower.

With only three stages in this design, it is unlikely that any wires as longer than 4-5mm will even be considered. Data for wirelengths up to the 16mm long are shown because that is when the design becomes fully uniform. The most interesting region is around 2-3mm, where the best designs begin to shift from lumped designs to distributed designs.

| Delay-Driven Results |                           |                |          |                                 |                           |  |  |

|----------------------|---------------------------|----------------|----------|---------------------------------|---------------------------|--|--|

| Wirelengths          | Best wire<br>distribution | Rutter   Delay |          | Best delay for<br>Lumped Design | Performance<br>Difference |  |  |

| 1mm                  | 0.00 0.00 1.00            | 1 4 21         | 185.4ps  | 185.4ps                         | 0%                        |  |  |

| 2mm                  | 0.00 0.00 1.00            | 1 5 36         | 305.8ps  | 305.8ps                         | 0%                        |  |  |

| 2.5mm                | 0.00 0.15 0.85            | 1 7 38         | 379.8ps  | 382.3ps                         | 1%                        |  |  |

| 2.8mm                | 0.00 0.25 0.75            | 1 8 37         | 423.5ps  | 434.3ps                         | 2%                        |  |  |

| 3mm                  | 0.00 0.25 0.75            | 1 8 39         | 453.2ps  | 471.5ps                         | 4%                        |  |  |

| 4mm                  | 0.00 0.35 0.65            | 1 10 39        | 613.5ps  | 687.4ps                         | 11%                       |  |  |

| 5mm                  | 0.00 0.40 0.60            | 1 12 39        | 796.6ps  | 956.6ps                         | 17%                       |  |  |

| 6mm                  | 0.00 0.40 0.60            | 1 12 39        | 1004ps   | 1281ps                          | 22%                       |  |  |

| 7mm                  | 0.00 0.45 0.55            | 1 14 36        | 1237ps   | 1662ps                          | 26%                       |  |  |

| 8mm                  | 0.00 0.45 0.55            | 1 14 36        | 1496ps   | 2098ps                          | 29%                       |  |  |

| 9mm                  | 0.00 0.45 0.55            | 1 16 39        | . 1781ps | 2590ps                          | 31%                       |  |  |

| 10mm                 | 0.00 0.45 0.55            | 1 16 39        | 2094ps   | 3138ps                          | 33%                       |  |  |

| 12mm                 | 0.00 0.45 0.55            | 1 18 39        | 2802ps   | 4401ps                          | 36%                       |  |  |

| 16mm                 | 0.00 0.50 0.50            | 1 22 36        | 4539ps   | 7596ps                          | 40%                       |  |  |

**Table 3.4 - Delay-Driven Results**

One concern with the delay driven analysis based on Elmore delay calculations is that buffer sizes tend to increase rapidly. A commonly used method to reducing the area usage is to use the area-delay product metric to improve the tradeoff between area and delay. The results in Table 3.5 are determined using the area-delay metric.

| AreaDelay-Driven Results |                           |                                                    |         |                                                        |                           |  |  |

|--------------------------|---------------------------|----------------------------------------------------|---------|--------------------------------------------------------|---------------------------|--|--|

| Wirelengths              | Best wire<br>distribution | Best AreaDelay Buffer Sizes AreaDelay driven Delay |         | Best AreaDelay<br>driven delay<br>For Lumped<br>Design | Performance<br>Difference |  |  |