Abstract

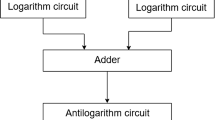

The Logarithmic Number System (LNS) can be considered a simplification of the Floating Point (FP) Number System that assumes the mantissa is always equal to one, and has a binary fixed-point exponent. LNS converts multiplication/division to a single addition/subtraction, which make LNS a very attractive choice for applications where these operations predominate, such as in some signal-processing algorithms. However, for wordlengths greater than 20 bits LNS becomes expensive because of the hardware-demanding LNS operations of addition and subtraction, which are typically important for most signal-processing algorithms. This paper gives an overview of the family of LNS subtraction algorithms called “Cotransformations,” and proposes a “Novel Cotransformation Combination” that offers improvements in terms of area and speed without sacrificing accuracy compared to previous methods. The hardware requirements of the proposed method are analyzed mathematically, and the results are verified by using synthesis and simulations.

Similar content being viewed by others

References

ANSI/IEEE (1985). Standard 754-1985 for Binary Floating-Point Arithmetic.

Swartzlander, E. E., & Alexopoulos, A. G. (1975). The sign/logarithm number system. IEEE Transactions on Computers, 24, 1238–1242, Dec.

Swartzlander, E. E., Chandra, D., Nagle, T., & Starks, S. A. (1983). Sign/logarithm arithmetic for FFT implementation. IEEE Transactions on Computers, C-32, 526–534.

Chester, E. I., & Coleman, J. N. (2002). Matrix engine for signal processing applications using the logarithmic number system. In Proceedings of the 13 th IEEE international conference on application-specific systems, architectures and processors (pp. 315–324). San Jose, CA, 17–19 July.

Jullien, G. A. (2006). Array processing using alternate arithmetic - A 20 year legacy. In Proceedings of the IEEE international conference on application-specific systems, architectures, and processors (pp. 199–204). Steamboat Springs, CO. 11–13 Sept.

Bleris, L. G., Garcia, J. G., Kothare, M. V., & Arnold, M. G. (2006). Towards embedded model predictive control for system-on-a-chip applications. Journal of Process Control, 16, 255–264, March.

Wrigley, A. (1993). Real-time ray tracing on a novel HDTV framestore. PhD thesis, University of Cambridge, England.

Makino, J., & Taiji, M. (1998). Scientific simulations with special-purpose computers: The GRAPE systems. John Wiley & Son Ltd., Feb.

Young, S., Kershaw, D., Odell, J., Ollason, D., Valtchev, V., & Woodland, P. (2006). The HTK book (Version 3.4). Cambridge University Engineering Department, Dec.

Hughey, R., & Blas, A. D. (2006). The UCSC Kestrel application-unspecific processor. In Proceedings of the IEEE international conference on application-specific systems, architectures, and processors (pp. 163–168). Steamboat Springs, CO, 11–13 Sept.

Haselman, M., Beauchamp, M., Wood, A., Hauck, S., Underwood, K., & Hemmert, K. S. (2005). A comparison of floating point and logarithmic number systems for FPGAs. In Proceedings of the 13 th annual IEEE symposium on field-programmable custom computing machines (FCCM’05) (pp. 181–190). Washington, DC: IEEE Computer Society, 17–20 April.

Collange, C., de Dinechin, F., & Detrey, J. (2006). Floating point or LNS: Choosing the right arithmetic on an application basis. In Proceedings of the 9 th EuroMicro digital system design (DSD 2006) (pp. 197–203). Dubrovnik: Croatia, 30 Aug.–1 Sept.

Detrey, J., & de Dinechin, F. (2007). A tool for unbiased comparison between logarithmic and floating-point arithmetic. The Journal of VLSI Signal Processing, 49, 161–167, October.

Fu, H., Mencer, O., & Luk, W. (2007). Optimizing logarithmic arithmetic on FPGAs. In Proceedings of the IEEE symposium on field-programmable custom computing machines (pp. 163–172). Palo Alto, CA, 14–15 April.

Coleman, J. N., Softley, C. I., Kadlec, J., Matousek, R., Tichy, M., Pohl, Z., et al. (2008). The European logarithmic microprocessor. IEEE Transactions on Computers, 57, 532–546, April.

Coleman, J. N. (1995). Simplification of table structure in logarithmic arithmetic. IEE Electronic Letters, 31, 1905–1906, 26 Oct.

Vouzis, P., Collange, C., & Arnold, M. (2007). LNS subtraction using novel cotransformation and/or interpolation. In Proceedings of the 18 th IEEE international conference on application-specific systems, architectures, and processors (pp. 107–114). Montreal, Canada, 9–11 July.

Vouzis, P., Collange, C., & Arnold, M. (2007). Cotransformation provides area and accuracy improvement in an HDL Library for LNS subtraction. In Proceedings of the 10 th EuroMicro conference on digital systems and design (pp. 85–93). Lübeck, Germany, 27–31 August.

Detrey, J., & de Dinechin, F. (2003). A VHDL library of LNS operations. In Proceedings of the 37 th asilomar conference on signals, systems, and computers (Vol. 2, pp. 2227–2231). Pacific Grove, CA, 9–12 Nov.

Arnold, M., & Winkel, M. (2001). Reconfiguring an FPGA-based RISC for LNS arithmetic. In Reconfigureable technology: FPGAs and reconfigurable processors for computing and communications III, proceedings of SPIE (Vol. 4525, pp. 88–98). Denver, CO, 21–22 Aug.

Arnold, M. G., Bailey, T. A., Cowles, J. R., & Winkel, M. D. (1998). Arithmetic co-transformations in the real and complex logarithmic number systems. IEEE Transactions on Computers, 47, 777–786, July.

Lewis, D. M. (1995). 114 MFLOPS logarithmic number system arithmetic unit for DSP applications. IEEE Journal of Solid-State Circuits, 30, 1547–1553, Dec.

de Dinechin, F., & Tisserand, A. (2005). Multipartite table methods. IEEE Transactions on Computers, 54, 319–330, March.

Arnold, M. G. (2002). An improved cotransformation for logarithmic subtraction. In Proceedings of the international symposium on circuits and systems (ISCAS’02) (pp. 752–755). Scottsdale, Arizona, 26–29 May.

Hassler, H., & Takagi, N. (1995). Function evaluation by table look-up and addition. In Proceedings of the 12 th symposium on computer arithmetics (pp. 10–16). Bath, England, 19–21 July.

Detrey, J., & de Dinechin, F. (2005). Table-based polynomials for fast hardware function evaluation. In Proceedings of the 16 th international conference on application-specific systems, architectures and processors (ASAP’05) (pp. 328–333). Samos, Greece, 23–25 July.

Lee, D., Luk, W., Villasenor, J., & Cheung, P. (2003). Non-uniform segmentation for hardware function evaluation. In Proceedings of the international conference on field programmable logic and its applications LNCS 2778 (pp. 796–807). Lisbon, Portugal 1–3 Sept.

Lewis, D. M. (1990). An architecture for addition and subtraction of long word length numbers in the logarithmic number system. IEEE Transactions on Computers, 39, 1325–1336, Nov.

Arnold, M. G. (2001). Design of a faithful LNS interpolator. In Proceedings of the 4 th EuroMicro digital system design (DSD’01) (pp. 336–345). Warsaw, Poland, 4–6 Sept.

Arnold, M. G. (2001). A pipelined LNS ALU. In Proceedings of the IEEE workshop on VLSI (pp. 155–161). Orlando, Florida, 19–20 April.

Arnold, M. G. (2004). LPVIP: A low-power ROM-less ALU for low-precision LNS. In Proceedings of the 14 th international workshop on power and timing modeling, optimization and simulation LNCS 3254, (pp. 675–684). Santorini, Greece, 15–17 Sept.

Arnold, M. G. (2004). Redundant logarithmic arithmetic for MPEG decoding. In Proceedings of the international symposium on optical science SPIE annual meeting 2004 (Vol. 5559, pp. 112–122). Denver, CO, 2–6 Aug.

Acknowledgements

The authors would like to thank Nicolas Frantzen and Jesus Garcia for their contributions in the early stages of this work.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Vouzis, P.D., Collange, C. & Arnold, M.G. A Novel Cotransformation for LNS Subtraction. J Sign Process Syst 58, 29–40 (2010). https://doi.org/10.1007/s11265-008-0282-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-008-0282-7