Abstract

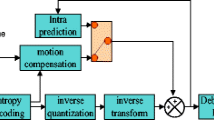

In H.264/AVC, a deblocking filter improves visual quality by reducing the presence of blocking artifacts in decoded video frames. The deblocking filter accounts for one third of the computational complexity of the decoder. This paper exploits the scalability on the hardware and the algorithmic level to synergize the performance and to reduce the computational complexity. First, we propose a modular deblocking filter architecture which can be scaled to adapt to the required computing capability for various bit-rates, resolutions, and frame rate of video sequences. The scalable architecture is based on FPGA using dynamic partial reconfiguration. This desirable feature of FPGAs makes it possible for different hardware configurations to be implemented during run-time. The proposed design can be scaled to filter up to four different edges simultaneously, resulting in significant reduction of total processing time. Secondly, our experiments show that significant reduction in computational complexity can be achieved by the increased presence of skipped macroblocks at lower bit-rates, thus, avoiding redundant filtering operations. The implemented architecture is evaluated using the Xilinx Virtex-4 ML410 FPGA board. The design operates at a maximum frequency of 103 MHz. The reconfiguration is done through Internal Configuration Access Port (ICAP) to achieve maximum performance needed by real time applications.

Similar content being viewed by others

References

Joint Video Team (JVT) of ITU-T VCEG and ISO/IEC MPEG, Draft ITU-T Recommendation and Final Draft International Standard of JointVideo Specification, ITU-T Rec. H.264 and ISO/IEC 14496–10 AVC, May 2003.

Wiegand, T., Sullivan, G. J., Bjøntegaard, G., & Luthra, A. (2003). Overview of the H.264/AVC Video Coding Standard. IEEE Tranactions on Circuits and Systems for Video Technology, 13(7), 560–576.

Peter List, Anthony Joch, Jani Lainema, Gisle Bjøntegaard, and Marta Karczewicz, “Adaptive Deblocking Filter”, IEEE Transactions on Circuits and Systems for Video Technology, pp. 614–619, July 2003.

C. Arbelo, A. Kanstein, S. Lopez, J.F. Lopez, M. Berekovic, R. Sarmiento, and J.-Y. Mignolet, “Mapping Control-Intensive Video Kernels onto a Coarse-Grain Reconfigurable Architecture: the H.264/AVC Deblocking Filter”, Design, Automation & Test in Europe Conference & Exhibition, pp.1–6, 2007.

Warrington, S., Shojania, H., and Sudharsanan, S., “Performance Improvement of the H.264/AVC Deblocking Filter Using SIMD Instructions”, International Symposium on Circuits And Systems, pp.2697–2700, 2006.

C. C. Cheng and T. S. Chang, “An Hardware Efficient Deblocking Filter for H.264/AVC”, IEEE International Conference on Consumer Electronics, pp.235–236, Jan. 2005.

G. Khurana, A. A. Kassim, T. P. Chua, and M. B. Mi., “A pipelined hardware implementation of In-loop Deblocking Filter in H.264/AVC”, IEEE Transactions on Consumer Electronics, pp.536–540, 2006.

B. Sheng, W. Gao, and D. Wu. “An Implemented Architecture of Deblocking Filter for H.264/AVC”, Proceedings - International Conference on Image Processing, pp.665–668, 2004.

Hao, W.N. and Radetzki, M., “A Data Traffic Efficient H.264 Deblocking IP”, IEEE Int. Symp. on Circuits and Systems, pp.3430–3433, 2008.

Min, K.Y. and Chong, J.W., “A Memory and Performance Optimized Architecture of Deblocking Filter in H.264/AVC”, IEEE Conf. on Multimedia and Ubiquitous Engineering, pp.220–225, 2007.

Lingfeng Li, Satoshi Goto, and Takeshi Ikenaga, “A Highly Parallel Architecture for Deblocking Filter in H.264/AVC”, IEICE Transactions on Information and Systems, Vol.E88-D, no.7, pp.1623–1629, July 2005.

Li, S. Goto, and T. Ikenaga. “An efficient deblocking filter architecture with 2-dimensional parallel memory for H.264/AVC”. Proceedings of the 2005 conference on Asia South Pacific design automation, pages 623–626, 2005.

S. Shih, C. Chang, and Y. Lin. “A near optimal deblocking filter for H.264 advanced video coding”, Proceedings of the Asia and South Pacific Design Automation Conference, pp.170–175, 2006.

Parlak, M., & Hamzaoglu, I. (2008). Low Power H.264 Deblocking Filter Hardware Implementations. IEEE Transactions on Consumer Electronics, 54(2), 808–816.

Yoshinori Hayashi, Tian Song, Eiji Koeta, and Takashi Shimamoto, “Fast Deblocking Filter Implementation Method and It’s Architecture for H.264/AVC”, International Conferencein Electrical Engineering/Electronics, Computer, Telecommunications, and Information Technology, pp.I-465–468, May 2008.

R. Khraisha and J. Lee, “A Scalable H.264/AVC Deblocking Filter Architecture Using Dynamic Partial Reconfiguration”, IEEE International Conference on Acoustics, Speech, and Signal Processing,pp.1566–1569, March 14–19, 2010.

Xilinx Inc., PlanAhead 10.1 User guide, http://www.xilinx.com/support/documentation/sw_manuals/PlanAhead_UserGuide.pdf .

Lysaght, P., Blodget, B., Mason, J., Young, J., & Bridgford, B. (2006). Invited Paper: Enhanced Architectures, Design Methodologies and CAD Tools for Dynamic Reconfiguration of Xilinx FPGAs. Internatonal Conference on Field Programmable Logic and Applications, 30, 1–6.

XILINX, Virtx-4 FPGA Configuration User Guide, June 2009.

Ke, Xu, Liu, T. M., Guo, J. I., & Choy, C. S. (2009). “Methods for Power/throughput/area Optimization of H.264/AVC Decoding”. Journal of Signal Processing Systems. doi:10.1007/s11265-009-0408-6.

XILINX, Virtex-4 FPGA User Guide, August 2007.

Liu, T. M., Lee, W. P., Lin, T. A., & Lee, C.-Y. (2005). “A memory efficient deblocking filter for H.264/AVC video coding”. IEEE International Conference Symposium on Circuit and Systems, 3, 2140–2143.

Cheng, C.-C., Chang, T.-S., & Lee, K.-B. (2006). An in-place architecture for deblocking filter in H.264/AVC. IEEE Transactions on Circuits and Systems II, 53(7), 530–534.

XILINX 2006. Early Access Partial Reconfiguration. User Guide 208

XILINX 2007a. Difference-Based Partial Reconfiguration. Application Note 290.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Khraisha, R., Lee, J. A Bit-Rate Aware Scalable H.264/AVC Deblocking Filter Using Dynamic Partial Reconfiguration. J Sign Process Syst 66, 225–234 (2012). https://doi.org/10.1007/s11265-011-0584-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-011-0584-z