Abstract

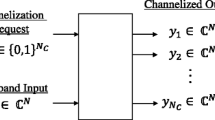

The channelization function in the digital front-end is one of the most computationally intensive kernels in the software defined radio baseband. The channelization tasks of filtering and decimation can be efficiently performed by a multistage decimation filter structure. The individual filter stages within the decimation filter may operate at different clock rates which may be incommensurate. The multiplicity of clock signals required to support multiple standards necessitates that the clock generation circuitry be parameterizable. In addition to the clock rates of the filter stages, some of the filter stages themselves may need to be fully or partially parameterizable. The current work has two major contributions. Firstly we propose an architecture for generating the multiplicity of clock signals required in a each mode of a multistandard channelization accelerator using a single reference clock. Secondly we propose a mechanism for loading and locally storing the configuration data for the clock generation circuitry as well as the accelerator datapath while switching between standards.

Similar content being viewed by others

References

Reed, J. H. (2002). Software radio: A modern approach to radio engineering (pp. 2–4). New Jersey: Prentice Hall.

Berkel, K. V., et al. (2005). Vector processing as an enabler for software-defined radio in handheld devices. EURASIP Journal on Applied Signal Processing, 2005(1), 2613–2625.

Nilsson, A., Tell, E., & Liu, D. (2004). An accelerator architecture for programmable multistandard baseband processors, in Proc. of WNET2004

Hentschel, T., Henker, M., & Fettweis, G. P. (1999). The digital front-end of software radio terminals. IEEE Personal Communications, 6(4), 40–46.

Ghazel, A., Naviner, L., & Grati, K. (2002). On design and implementation of a decimation filter for multistandard wireless transceivers. IEEE Transactions on Wireless Communications, 1(4), 558–562.

Tao, Z., & Signell, S. (2006). Multi-standard delta-sigma decimation filter design, in Proc. of IEEE Asia Pacific Conference on Circuits and Systems. (pp. 1212–1215)

Michael, N., Vinod, A. P., Moy, C., & Palicot, J. (2011). Design of multistandard channelization accelerators for software defined radio handsets. IEEE Transactions on Signal Processing, 59(10), 4767–4780.

Gao, Y., Jia, L., Isoaho, J., & Tenhunen, H. (1999). A comparison design of comb decimators for sigma-delta analog-to-digital converters. Analog Integrated Circuits and Signal Processing, 22, 51–60.

Vaidyanathan, P. P. (1993). Multirate systems and filter banks, Prentice Hall, PTR

Rusu, A., Dong, B., & Ismail, M. (2006). Putting the “FLEX” in flexible mobile wireless radios—A wideband bandpass sigma-delta ADC for software radios. IEEE Circuits and Devices Magazine, 22(6), 24–30.

Vankka, J. (2005). Digital synthesizers and transmitters for software radio (pp. 239–257). NewYork: Springer-Verlag.

Achenbach, R., et al. (2000). A digitally temperature-compensated crystal oscillator. IEEE Journal of Solid-State Circuits, 35(10), 1502–1506.

Barret, C. (Ed.) (1999). Fractional/integer-N PLL basics, Texas instruments wireless communication business unit, technical brief SWRA029

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Michael, N., Vinod, A.P., Moy, C. et al. Design Strategy for Clocking and Runtime Parametrization in the Channelization Accelerator of Multistandard Radios. J Sign Process Syst 78, 171–177 (2015). https://doi.org/10.1007/s11265-013-0849-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11265-013-0849-9