Abstract

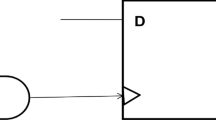

In present scenario, the portable wireless devices like mobile phones are used by almost every human being for communication purpose. Mobile devices are equipped with a processing element that is responsible for performing all the controlling and computational tasks. Most of the computational tasks inside the processing element are performed by ALU circuit. ALU is considered as the computational engine and responsible for high power consumption. Previously, microprocessors and microcontrollers were the choice of designers but nowadays the horizon has been shifted to FPGAs and SOCs as a processing element in mobile devices. Obviously, FPGAs have numerous advantages over processors and the growing need of applications compels the designers to use FPGAs for fast processing. Although FPGAs fulfils the requirement of designers but they suffer from the disadvantage of high power consumption due to their complex circuitry. The demand of high performance and low power devices creates a bottleneck in front of designers specifically for battery operated portable wireless devices. So, this paper presents some power minimization techniques that can be applied on communication centric designs targeted to FPGAs. There are different techniques given in the literature but most of them are applied at device level only. This paper gives an insight to minimize the power at architectural level of design hierarchy using XPower Analyzer as a CAD tool. The proposed techniques are applied on arithmetic and logical unit circuit for analysis purpose, as ALU is the heart of processing elements used in portable wireless devices. The circuit has been verified and realized on XILINX ISE directed to Spartan 3E XC3S250E FPGA. The analysis illustrates significant improvement in the power consumption.

Similar content being viewed by others

References

Anderson, J. H. (2005). Power optimization and prediction techniques for FPGAs. Ph.D Thesis, Electrical and Computer Engineering Department, Toronto University, Toronto, Ontario.

Lamoureux, J., & Luk, W. (2008). An overview of low-power techniques for FPGAs. In Conference on adaptive hardware and systems (pp. 338–345). Imperial College London.

Jevtic, R., & Carreras, C. (2010). Power estimation of embedded multiplier blocks in FPGAs. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 18(5), 835–839.

Mishra, S., & Verma, G. (2013). Low power and area efficient implementation of BCD adder on FPGA. In Proceedings of IEEE international conference on signal processing and communication (pp. 461–465).

Kumar, T., Pandey, B., Das, T., & Chowdhry, B. S. (2014). Mobile DDR IO standard based high performance energy efficient portable ALU design on FPGA. Wireless Personal Communications, 76(3), 569–578.

Kumar, T., Pandey, B., Musavi, S. H. A., & Zaman, N. (2015). CTHS based energy efficient thermal aware image ALU design on FPGA. Wireless Personal Communications, 83(1), 671–696.

Verma, G., Kumar, M., & Khare, V. (2015). Low power techniques for digital system design. Indian Journal of Science and Technology, 8(17), IPL063.

Verma, G., Mishra, S., Aggarwal, S., Singh, S., Shekhar, S., & Virdi, S. K. (2015). Power consumption analysis of BCD adder using Xpower Analyzer on VIRTEX FPGA. Indian Journal of Science and Technology, 8(17), IPL160.

Musavi, S. H. A., Chowdhry, B. S., Kumar, T., Pandey, B., & Kumar, W. (2015). IoTs enable active contour modelling based energy efficient and thermal aware object tracking on FPGA. Wireless Personal Communications, 85(2), 529–543.

Abdullah, M. F. L., Das, B., Shahida, M. S. N., & Pandey, B. (2015). Energy-efficient pseudo noise generator based optical transmitter for ethernet (IEEE 802.3az). In Proceedings of IEEE international conference on computer communication and control technology (pp. 142–146).

Pandey, B., Yadav, J., Rajoria, N., & Pattanaik, M. (2013). Clock gating based energy efficient ALU design and implementation on FPGA. In Proceedings of IEEE international conference on energy efficient technologies for sustainability (pp. 93–97).

Cisneros, S., Panduro, J. J., Muro, J., & Boemo, E. (2012). Rapid prototyping of a self-timed ALU with FPGAs. In Proceedings of IEEE international conference on reconfigurable computing and FPGAs (pp. 26–33).

Khorasani, V., Vahdat, B. V., & Mortazavi, M. (2012). Design and implementation of floating point ALU on a FPGA processor. In IEEE international conference on computing, electronics and electrical technologies (pp. 772–776).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Verma, G., Kumar, M., Khare, V. et al. Analysis of Low Power Consumption Techniques on FPGA for Wireless Devices. Wireless Pers Commun 95, 353–364 (2017). https://doi.org/10.1007/s11277-016-3896-2

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-016-3896-2