Abstract

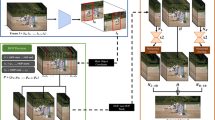

High-efficiency video coding (HEVC) is a latest video coding standard and the motion estimation unit is the most important block. The work presents the different types of Matching Criteria for Block-Based Motion Estimation technique in HEVC standard. HEVC requires fast motion estimation algorithms to have better real time performance. The hardware implementation of motion estimation helps to achieve high speed though parallel processing. An improved block matching technique is designed with reduced blocks for HEVC. The proposed method has less execution time where only blocks having motion are compared for prediction computation. The searching time complexity is dependent on the number of blocks that are having motion. The searching time of frame having small motion can be reduced to 80–85% as compared to the traditional full search algorithm. In the paper, sum of absolute difference, mean square error and mean absolute difference are computed to find the best matching algorithm for HEVC. However, SAD has less computational complexity with compare to other matching criteria. The results suggest that proposed motion estimation algorithm has better performance with compare to similar previous work.

Similar content being viewed by others

References

Bossen, F., Bross, B., Suhring, K., & Flynn, D. (2012). HEVC complexity and implementation analysis. IEEE Transactions on Circuits and Systems for Video Technology,22(12), 1685–1696.

Wang, S., Zhou, D., Zhou, J., Yoshimura, T., & Goto, S. (2017). VLSI implementation of HEVC motion compensation with distance biased direct cache mapping for 8 K UHDTV applications. IEEE Transactions on Circuits and Systems for Video Technology,27(2), 380–393.

Nalluri, P, Alves, L. N., & Navarro, A. (2013). A novel SAD architecture for variable block size motion estimation in HEVC video coding. In 2013 international symposium on system on chip (SoC) (pp. 1–4). IEEE, 2013.

Joshi, A, Mishra, V., & Patrikar, R. M. (2012) Real time implementation of digital watermarking algorithm for image and video application. In Watermarking (Vol. 2). InTech, 2012.

Zuo, S., Wang, M., & Xiao, L. (2014). Motion estimation algorithm for HEVC suitable for hardware implementation. In WSEAS transactions on signal processing (Vol. 10).

Sze, V., Madhukar B., & Sullivan G. J. (2014). High efficiency video coding (HEVC). In Integrated circuit and systems, algorithms and architectures (Vol. 39, p. 40). Springer.

Joshi, A. M., Ansari, M. S., & Sahu, C. (2018). VLSI architecture of high speed SAD for high efficiency video coding (HEVC) encoder. In 2018 IEEE international symposium on circuits and systems (ISCAS) (pp. 1–4). IEEE, 2018.

Liu, H., Lei, H., & Rao, Y. (2017). Optimization algorithm based on texture feature and frame correlation in HEVC. Multimedia Tools and Applications,76(2), 1959–1981.

Chen, M., Zhang, Y., & Lu, C. (2017). Efficient architecture of variable size HEVC 2D-DCT for FPGA platforms. AEU-International Journal of Electronics and Communications,73, 1–8.

Brandenburg, J., & Stabernack, B. (2016). Simulation-based HW/SW co-exploration of the concurrent execution of HEVC intra encoding algorithms for heterogeneous multi-core architectures. Journal of Systems Architecture,77, 26–42.

Sullivan, G. J., Ohm, J.-R., Han, W.-J., & Wiegand, T. (2012). Overview of the high efficiency video coding (HEVC) standard. IEEE Transactions on Circuits and Systems for Video Technology,22(12), 1649–1668.

Joshi, A. M., Mishra, V., & Patrikar, R. M. (2016). FPGA prototyping of video watermarking for ownership verification based on H. 264/AVC. Multimedia Tools and Applications,75(6), 3121–3144.

Lin, J.-L., Chen, Y.-W., Huang, Y.-W., & Lei, S.-M. (2013). Motion vector coding in the HEVC standard. IEEE Journal of Selected Topics in Signal Processing,7(6), 957–968.

Medhat, A., Shalaby, A., Sayed, M. S., Elsabrouty, M., & Mehdipour, F. (2014). A highly parallel SAD architecture for motion estimation in HEVC encoder. In 2014 IEEE Asia Pacific conference on circuits and systems (APCCAS) (pp. 280–283). IEEE 2014.

Leon, J. S., Cardenas, C. S., & Castillo, E. C. V. (2016). A highly parallel 4 K real-time HEVC fractional motion estimation architecture for FPGA implementation. In 2016 IEEE international conference on electronics, circuits and systems (ICECS) (pp. 708–711). IEEE, 2016.

Kim, I.-K., Min, J., Lee, T., Han, W.-J., & Park, J. (2012). Block partitioning structure in the HEVC standard. IEEE Transactions on Circuits and Systems for Video Technology,22(12), 1697–1706.

Davis, P., & Marikkannan, S. (2014). Implementation of motion estimation algorithm for H.265/HEVC’. In International conference on signal processing, embedded system and communication technologies and their applications for sustainable and renewable energy (ICSECSRE’2014).

Khemiri, R., Kibeya, H., Loukil, H., Sayadi, F. E., Atri, M., & Masmoudi, N. (2018). Real-time motion estimation diamond search algorithm for the new high efficiency video coding on FPGA. Analog Integrated Circuits and Signal Processing,94(2), 259–276.

Aguilar-González, A., Arias-Estrada, M., & Berry, F. (2019). Depth from a motion algorithm and a hardware architecture for smart cameras. Sensors,19(1), 53.

Wong, S., Vassiliadis, S., & Cotofana, S. (2002). A sum of absolute differences implementation in FPGA hardware. In Proceedings 28th Euromicro Conference (pp. 183–188). IEEE, 2002.

Luo, L., Zou, C., Gao, X., & He, Z. (1997). A new prediction search algorithm for Block motion estimation in video coding. IEEE Transactions on Consumer Electronics,43(1), 56–61.

Hosur, P. I., & Ma, K.-K. (2003). Motion vector field adaptive fast motion estimation. In Second international conference on information, communications and signal processing (ICICS), 2003.

Nalluri, P. Alves, L. N., & Navarro, A. (2014). High speed SAD architectures for variable block size motion estimation in HEVC video coding. In 2014 IEEE international conference on image processing (ICIP) (pp. 1233–1237). IEEE, 2014.

Alcocer, E., Gutierrez, R., Lopez-Granado, O., & Malumbres, M. P. (2019). Design and implementation of an efficient hardware integer motion estimator for an HEVC video encoder. Journal of Real-Time Image Processing,16(2), 547–557.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Joshi, A.M., Bramha, A. VLSI Architecture of Block Matching Algorithms for Motion Estimation in High Efficiency Video Coding. Wireless Pers Commun 112, 907–922 (2020). https://doi.org/10.1007/s11277-020-07081-z

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-020-07081-z