Abstract

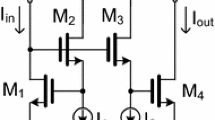

In this paper a novel structure is introduced for programming current gain amplifier that works in near subthreshold regime. The flipped voltage follower is utilized to achieve different gain and the subthreshold MOS is using in order to decrease power consumption. Class AB structure is used to attain a wide dynamic range. These techniques are led to achieving low complexity and low area and ultra-low power compare to previous PGA. Moreover, by using the resistor the current is converted to voltage in output node, hence, the voltage gain is achieved simply by using this structure. The post-layout simulation result shows the proposed structure could provide current gain from 0 to 25 dB, while constant bandwidth of 10 MHz. However, the power consumption of the proposed PCGA is only 120 nW with ± 0.6 V supply. These results are verified by the post-simulations of the proposed PCGA that performed by 65 nm standard CMOS technology.

Similar content being viewed by others

References

Ghorbani, A., & Safari, L. (2011). High CMRR low-voltage low power current output stage with a novel CMFB. In 2011 3rd international conference on computer research and development (ICCRD) (pp. 382–386).

Azhari, S. J., Ghorbani, A., & Safari, L. (2011). A novel fully differential current buffer with ultra low input impedance, high CMRR, low power and low voltage. In 2011 3rd international conference on electronics computer technology (ICECT) (pp. 229–233).

Ghorbani, A., & Ghanaatian, A. (2012). A novel high CMRR, low power and low voltage COS with QFG. Circuits and Systems, 3(3), 6.

Ara, M. B., & Azhari, S. J. (2016). A low-voltage fully differential pure current mode current operational amplifier. Circuits, Systems, and Signal Processing, 35, 2626–2639.

Da Toh, W., Zheng, Y., & Heng, C.-H. (2012). Low power digital baseband for impulse radio ultra-wideband transceiver. Circuits, Systems, and Signal Processing, 31, 223–235.

Andreev, S., Galinina, O., Pyattaev, A., Gerasimenko, M., Tirronen, T., Torsner, J., et al. (2015). Understanding the IoT connectivity landscape: A contemporary M2M radio technology roadmap. IEEE Communications Magazine, 53, 32–40.

Treurniet, J. J., Sarkar, C., Prasad, R. V., & De Boer, W. (2015). Energy consumption and latency in BLE devices under mutual interference: An experimental study. In 2015 3rd international conference on future Internet of Things and cloud (FiCloud) (pp. 333–340).

Vucinic, M., Tourancheau, B., Rousseau, F., Duda, A., Damon, L., & Guizzetti, R. (2014). Energy cost of security in an energy-harvested IEEE 802.15. 4 Wireless Sensor Network. In 2014 3rd Mediterranean conference on embedded computing (MECO) (pp. 198–201).

Balicki, J., Beringer, M., Korlub, W., Przybylek, P., Tyszka, M., & Zadroga, M. (2015). Collective citizens’ behavior modelling with support of the Internet of Things and Big Data. In 2015 8th international conference on human system interactions (HSI) (pp. 61–67).

Ghorbani, A., & Ghaznavi-Ghoushchi, M. (2017). A novel transceiver structure including power and audio amplifiers for Internet of Things applications. Computers & Electrical Engineering, 62, 29–43.

De Matteis, M., De Blasi, M., Cocciolo, G., Baschirotto, A., & Sabatini, M. (2011). A 1 V 115 μW 20nV/√ Hz 15–50 dB-range PGA with 5 MHz bandwidth for UWB personal area network. In 2011 18th IEEE international conference on electronics, circuits and systems (ICECS) (pp. 77–80).

Ratametha, C., Tepwimonpetkun, S., & Wattanapanitch, W. (2019). A 2.64-μW 71-dB SNDR discrete-time signal-folding amplifier for reducing ADC’s resolution requirement in wearable ECG acquisition systems. IEEE Transactions on Biomedical Circuits and Systems, 14, 48–64.

Petraglia, A., & Mitra, S. (1991). Switched-capacitor equalizers with digitally programmable tuning characteristics. IEEE Transactions on Circuits and Systems, 38, 1322–1331.

Mazurek, A., & Wawryn, K. (2001). Programmable current mode circuits. In The 8th IEEE international conference on electronics, circuits and systems, 2001. ICECS 2001 (pp. 553–556).

Paulino, N., Franca, J., & Martins, F. (1995). Programmable CMOS switched-capacitor biquad using quasi-passive algorithmic DAC’s. IEEE Journal of Solid-State Circuits, 30, 715–719.

Islam, M. S., Singh, S. K., Xereas, G., Chodavarapu, V. P., & Mandal, S. (2019). A digitally programmable CMOS feedback ASIC for highly stable MEMS-referenced oscillators. IEEE Transactions on Circuits and Systems I: Regular Papers, 66, 4158–4171.

El-Adawy, A. A., Soliman, A. M., & Elwan, H. O. (2002). Low voltage digitally controlled CMOS current conveyor. AEU-International Journal of Electronics and Communications, 56, 137–144.

Hsu, C.-C., & Wu, J.-T. (2003). A highly linear 125-MHz CMOS switched-resistor programmable-gain amplifier. IEEE Journal of Solid-State Circuits, 38, 1663–1670.

Calvo, B., Celma, S., & Sanz, M. (2003). High-frequency digitally programmable gain amplifier. Electronics Letters, 39, 1.

Rijns, J. (1996). CMOS low-distortion high-frequency variable-gain amplifier. IEEE Journal of Solid-State Circuits, 31, 1029–1034.

Elwan, H. O., & Ismail, M. (2000). Digitally programmable decibel-linear CMOS VGA for low-power mixed-signal applications. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 47, 388–398.

El-Adawy, A., Soliman, A., & Elwan, H. (2000). Low voltage fully differential CMOS voltage mode digitally controlled variable gain amplifier. Microelectronics Journal, 31, 139–146.

Rahmatian, B., & Mirabbasi, S. (2007). A low-power 75 dB digitally programmable variable-gain amplifier in 0.18 μm CMOS. Canadian Journal of Electrical and Computer Engineering, 32, 181–186.

Calvo, B., Celma, S., & Sanz, M. (2006). Low-voltage low-power 100 MHz programmable gain amplifier in 0.35 μm CMOS. Analog Integrated Circuits and Signal Processing, 48, 263–266.

Angkeaw, K., & Prommee, P. (2011). Two digitally programmable gain amplifiers based on current conveyors. Analog Integrated Circuits and Signal Processing, 67, 253–260.

Kahng, D., & Sze, S. M. (1967). A floating gate and its application to memory devices. Bell System Technical Journal, 46, 1288–1295.

Vittoz, E., & Fellrath, J. (1977). CMOS analog integrated circuits based on weak inversion operations. IEEE Journal of Solid-State Circuits, 12, 224–231.

Blalock, B. J., Allen, P. E., & Rincon-Mora, G. A. (1998). Designing 1-V op amps using standard digital CMOS technology. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 45, 769–780.

Comer, D. J., & Comer, D. T. (2004). Using the weak inversion region to optimize input stage design of CMOS op amps. IEEE Transactions on Circuits and Systems II: Express Briefs, 51, 8–14.

Tajalli, A., Brauer, E. J., Leblebici, Y., & Vittoz, E. (2008). Subthreshold source-coupled logic circuits for ultra-low-power applications. IEEE Journal of Solid-State Circuits, 43, 1699–1710.

Annema, A. (1994). Hardware realisation of a neuron transfer function and its derivative. Electronics Letters, 30, 576–577.

Casson, A. J., & Rodriguez-Villegas, E. (2011). A 60 pW g C continuous wavelet transform circuit for portable EEG systems. IEEE Journal of Solid-State Circuits, 46, 1406–1415.

Al-Ashmouny, K., Chang, S.-I., & Yoon, E. (2011). A 8.6 μW 3-bit programmable gain amplifier for multiplexed-input neural recording systems. In 2011 annual international conference of the IEEE engineering in medicine and biology society (pp. 2945–2948).

Harjani, R. (1995). A low-power CMOS VGA for 50 Mb/s disk drive read channels. IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, 42, 370–376.

Garcia-Alberdi, C., Aguado-Ruiz, J., Lopez-Martin, A. J., & Ramirez-Angulo, J. (2013). Micropower class-AB VGA with gain-independent bandwidth. IEEE Transactions on Circuits and Systems II: Express Briefs, 60, 397–401.

Koolivand, Y., Rezaeiyan, Y., Shoaei, O., Jafarabadi-Ashtiani, S., Moftakharzadeh, A., & Ahmadvand, M. (2019). Modified linear in dB, sub 0.2 dB gain-step CMOS programmable gain amplifier for ultrasound applications. Analog Integrated Circuits and Signal Processing, 99, 497–508.

Liu, H., Zhu, X., Lu, M., Sun, Y., & Yeo, K. S. (2019). Design of reconfigurable dB-linear variable-gain amplifier and switchable-order gm-C filter in 65-nm CMOS technology. IEEE Transactions on Microwave Theory and Techniques, 67, 5148–5158.

Mazza, G., Cirio, R., Donetti, M., La Rosa, A., Luparia, A., Marchetto, F., et al. (2005). A 64-channel wide dynamic range charge measurement ASIC for strip and pixel ionization detectors. IEEE Transactions on Nuclear Science, 52, 847–853.

Ghorbani, A., & Ghaznavi-Ghoushchi, M. (2017). A novel fully differential CMOS Class-E power amplifier with higher output power and efficiency for IoT application. Wireless Personal Communications, 97, 3203–3213.

Kumngern, M., Khateb, F., & Kulej, T. (2015). A digitally programmable gain amplifier for ultra-low-power applications. Analog Integrated Circuits and Signal Processing, 85, 433–443.

Carvajal, R. G., Ramírez-Angulo, J., López-Martín, A. J., Torralba, A., Galán, J. A. G., Carlosena, A., et al. (2005). The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Transactions on Circuits and Systems I: Regular Papers, 52, 1276–1291.

Yamaji, T., Kanou, N., & Itakura, T. (2002). A temperature-stable CMOS variable-gain amplifier with 80-dB linearly controlled gain range. IEEE Journal of Solid-State Circuits, 37, 553–558.

Mostafa, M., Embabi, S., & Elmala, M. (2001). A 60 dB, 246 MHz CMOS variable gain amplifier for subsampling GSM receivers. In Proceedings of the 2001 international symposium on Low power electronics and design (pp. 117–122).

Zheng, Y., Yan, J., & Xu, Y. P. (2009). A CMOS VGA with DC offset cancellation for direct-conversion receivers. IEEE Transactions on Circuits and Systems I: Regular Papers, 56, 103–113.

Tadjpour, S., Behbahani, F., & Abidi, A. (1998). A CMOS variable gain amplifier for a wideband wireless receiver. In 1998 symposium on VLSI circuits, 1998. Digest of technical papers (pp. 86–89).

Gatta, F., Manstretta, D., Rossi, P., & Svelto, F. (2004). A fully integrated 0.18-μm CMOS direct conversion receiver front-end with on-chip LO for UMTS. IEEE Journal of Solid-State Circuits, 39, 15–23.

M. Elmala, B. Carlton, R. Bishop, & K. Soumyanath, “A 1.4 V, 13.5 mW, 10/100 MHz 6 th order elliptic filter/VGA with DC-offset correction in 90 nm CMOS [WLAN applications]. In 2005 IEEE radio frequency integrated circuits (RFIC) symposium-digest of papers, 2005 (pp. 189–192).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Ghorbani, A.R., Ghaznavi-Ghoushchi, M.B. An Ultra-Low Power Programmable Current Gain Amplifier with a Novel Current Gain Controller Structure for IoT Applications. Wireless Pers Commun 114, 3577–3593 (2020). https://doi.org/10.1007/s11277-020-07547-0

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-020-07547-0