Abstract

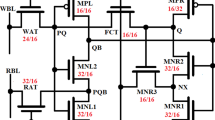

Satellite communication plays a vital role in extending 5G cellular networks to hard-to-reach areas, including airplanes, railways, shipments, other transport mechanisms, and especially in rural regions of the country that are traditionally beyond the reach of cellular service providers. The devices, specifically those incorporating static memories, being employed for satellite communication, face the challenge of getting prone to cosmic radiations or alpha particle strikes. These strikes cause multi-bit errors in static-memory cells that lead to loss of total output yield. This work proposes a low power twelve transistor (12T) SRAM cell that confirms a reduction in multi-bit errors for the Internet of things based devices supporting fifth-generation (5G) communication system. The proposed SRAM ensures improved read and write ability by utilizing a read decoupled access path and loop cutting mechanism, respectively. The proposed design improves read/write stability by 2.02 \(\times\)/1.05\(\,\times\) in comparison to conventional 6T cell with 2.52 \(\times\) silicon space overhead. The area overhead is neutralized by 3.17\(\times\) improvement in \(I_{on}\)/\(I_{off}\) ratio that improves cell density of SRAM cell. The improved critical charge of the proposed 12T SRAM cell is compared with four other considered cells to ensure the reduction in multi-bit soft errors, and thereby confirming its suitability for devices supporting satellite communications. The proposed design successfully eliminates the half-select issue that enables the implementation of the bit-interleaved architecture. The leakage power of the proposed 12T cell is improved by 2.65\(\times\) in comparison to conventional 6T attributed to series-connected devices used as loop cutting pair. This reduction of leakage power remains sustained till 110\(^{\circ }\) temperature. The simulation of this work has been conducted with cadence virtuoso tool using GPDK 45 nm technology file.

Similar content being viewed by others

Availability of Data and Materials

Data sharing not applicable to this article as no data sets were generated or analyzed during the current study.

References

Ilderem, V. (2019) 1.4 5g wireless communication: an inflection point. In 2019 IEEE international solid-state circuits conference-(ISSCC) (IEEE) (pp. 35–39).

Akpakwu, G. A., Silva, B. J., Hancke, G. P., & Abu-Mahfouz, A. M. (2017). A survey on 5g networks for the internet of things: Communication technologies and challenges. IEEE Access, 6, 3619.

Sutardja, S. (2014). Slowing of Moore’s law signals the beginning of smart everything. In 2014 44th European solid state device research conference (ESSDERC) (IEEE) (pp. 7–8).

Huo, Y., Dong, X., & Xu, W. (2017). 5g cellular user equipment: From theory to practical hardware design. IEEE Access, 5, 13992.

Jain, S., Khare, S., Yada, S., Ambili, V., Salihundam, P., Ramani, S., et al. (2012). A 280mv-to-1.2 v wide-operating-range ia-32 processor in 32nm cmos. In 2012 IEEE international solid-state circuits conference (IEEE) (pp. 66–68).

Khellah, M., Somasekhar, D., Ye, Y., Kim, N. S., Howard, J., Ruhl, G., et al. (2006). A 256-kb dual-vcc sram building block in 65-nm cmos process with actively clamped sleep transistor. IEEE Journal of Solid-State Circuits, 42(1), 233.

Sachdeva, A., & Tomar, V. K. (2020). A Schmitt-trigger based low read power 12T SRAM cell. Analog Integrated Circuits and Signal Processing, 105(2), 275–295.

Duan, C., Gotterba, A. J., Sinangil, M. E., & Chandrakasan, A. P. (2017). Energy-efficient reconfigurable sram: Reducing read power through data statistics. IEEE Journal of Solid-State Circuits, 52(10), 2703.

Shin, K., Choi, W., & Park, J. (2017). Half-select free and bit-line sharing 9t sram for reliable supply voltage scaling. IEEE Transactions on Circuits and Systems I: Regular Papers, 64(8), 2036.

Pal, S., & Islam, A. (2016). 9-t sram cell for reliable ultralow-power applications and solving multibit soft-error issue. IEEE Transactions on Device and Materials Reliability, 16(2), 172.

Frustaci, F., Khayatzadeh, M., Blaauw, D., Sylvester, D., & Alioto, M. (2015). Sram for error-tolerant applications with dynamic energy-quality management in 28 nm cmos. IEEE Journal of Solid-state circuits, 50(5), 1310.

Chiu, Y. W., Hu, Y. H., Tu, M. H., Zhao, J. K., Chu, Y. H., Jou, S. J., & Chuang, C. T. (2014). 40 nm bit-interleaving 12t subthreshold sram with data-aware write-assist. IEEE Transactions on Circuits and Systems I: Regular Papers, 61(9), 2578.

Ibe, E., Taniguchi, H., Yahagi, Y., Shimbo, K., & Toba, T. (2010). Impact of scaling on neutron-induced soft error in srams from a 250 nm to a 22 nm design rule. IEEE Transactions on Electron Devices, 57(7), 1527.

Artola, L., Gaillardin, M., Hubert, G., Raine, M., & Paillet, P. (2015). Modeling single event transients in advanced devices and ics. IEEE Transactions on Nuclear Science, 62(4), 1528.

Li, J., Reviriego, P., Xiao, L., Argyrides, C., & Li, J. (2017). Extending 3-bit burst error-correction codes with quadruple adjacent error correction. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 26(2), 221.

Bentoutou, Y. (2012). A real time edac system for applications onboard earth observation small satellites. IEEE Transactions on Aerospace and Electronic Systems, 48(1), 648.

Black, J. D., Dodd, P. E., & Warren, K. M. (2013). Physics of multiple-node charge collection and impacts on single-event characterization and soft error rate prediction. IEEE Transactions on Nuclear Science, 60(3), 1836.

Amusan, O. A., Witulski, A. F., Massengill, L. W., Bhuva, B. L., Fleming, P. R., Alles, M. L., et al. (2006). Charge collection and charge sharing in a 130 nm cmos technology. IEEE Transactions on nuclear science, 53(6), 3253.

Tu, M. H., Lin, J. Y., Tsai, M. C., Lu, C. Y., Lin, Y. J., Wang, M. H., et al. (2012). A single-ended disturb-free 9t subthreshold sram with cross-point data-aware write word-line structure, negative bit-line, and adaptive read operation timing tracing. IEEE Journal of Solid-State Circuits, 47(6), 1469.

Chang, I. J., Kim, J. J., Park, S. P., & Roy, K. (2009). A 32 kb 10t sub-threshold sram array with bit-interleaving and differential read scheme in 90 nm cmos. IEEE Journal of Solid-State Circuits, 44(2), 650.

Lo, C. H., & Huang, S. Y. (2011). Ppn based 10t sram cell for low-leakage and resilient subthreshold operation. IEEE Journal of Solid-State Circuits, 46(3), 695.

Sanvale, P., Gupta, N., Neema, V., Shah, A. P., & Vishvakarma, S. K. (2019). An improved read-assist energy efficient single ended ppn based 10t sram cell for wireless sensor network. Microelectronics Journal, 92, 104611.

Sachdeva, A., & Tomar, V. K. (2021). Design of low power half select free 10t static random-access memory cell. Journal of Circuits, Systems and Computers, 30(04), 2150073. https://doi.org/10.1142/S0218126621500730.

Kushwah, C., & Vishvakarma, S. K. (2015). A single-ended with dynamic feedback control 8t subthreshold sram cell. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 24(1), 373.

Sachdeva, A., & Tomar, V. K. (2020). Design of a stable low power 11-t static random access memory cell. Journal of Circuits, Systems and Computers, 29(13), 2050206. https://doi.org/10.1142/S0218126620502060.

Wen, L., Li, Z., & Li, Y. (2012). Differential-read 8t sram cell with tunable access and pull-down transistors. Electronics Letters, 48(20), 1260.

Chang, M. F., Chang, S. W., Chou, P. W., & Wu, W. C. (2010). A 130 mv sram with expanded write and read margins for subthreshold applications. IEEE Journal of Solid-State Circuits, 46(2), 520.

Sachdeva, A., & Tomar, V. (2021). Design of 10t sram cell with improved read performance and expanded write margin. IET Circuits, Devices and Systems, 15(1), 42.

Pal, S., Bose, S., Ki, W. H., & Islam, A. (2019). Half-select-free low-power dynamic loop-cutting write assist sram cell for space applications. IEEE Transactions on Electron Devices, 67(1), 80.

Islam, A., & Hasan, M. (2012). A technique to mitigate impact of process, voltage and temperature variations on design metrics of sram cell. Microelectronics Reliability, 52(2), 405.

Alioto, M. (2010). Understanding dc behavior of subthreshold cmos logic through closed-form analysis. IEEE Transactions on Circuits and Systems I: Regular Papers, 57(7), 1597.

Verma, N., & Chandrakasan, A. P. (2008). A 256 kb 65 nm 8t subthreshold sram employing sense-amplifier redundancy. IEEE Journal of Solid-State Circuits, 43(1), 141.

Pasandi, G., & Fakhraie, S. M. (2014). A 256-kb 9t near-threshold sram with 1k cells per bitline and enhanced write and read operations. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 23(11), 2438.

Shah, A. P., Vishvakarma, S. K., & Hübner, M. (2020). Soft error hardened asymmetric 10t sram cell for aerospace applications. Journal of Electronic Testing, 36, 1–15

Jahinuzzaman, S. M., Sharifkhani, M., & Sachdev, M. (2009). An analytical model for soft error critical charge of nanometric srams. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 17(9), 1187.

Sachdeva, A., & Tomar, V. (2021). Design of multi-cell upset immune single-end sram for low power applications. AEU-International Journal of Electronics and Communications, 128, 153516.

Ahmad, S., Alam, N., & Hasan, M. (2018). Pseudo differential multi-cell upset immune robust sram cell for ultra-low power applications. AEU-International Journal of Electronics and Communications, 83, 366.

Alouani, I., Elsharkasy, W. M., Eltawil, A. M., Kurdahi, F. J., & Niar, S. (2017). As8-static random access memory (sram): Asymmetric sram architecture for soft error hardening enhancement. IET Circuits, Devices and Systems, 11(1), 89.

Anh-Tuan, D., Low, J. Y. S., Low, J. Y. L., Kong, Z. H., Tan, X., & Yeo, K. S. (2011). An 8t differential sram with improved noise margin for bit-interleaving in 65 nm cmos. IEEE Transactions on Circuits and Systems I: Regular Papers, 58(6), 1252.

Chang, M. F., Wu, J. J., Chen, K. T., Chen, Y. C., Chen, Y. H., Lee, R., et al. (2010). A differential data-aware power-supplied (d2ps) 8t sram cell with expanded write/read stabilities for lower vddmin applications. IEEE Journal of Solid-State Circuits, 45(6), 1234.

Zheng, N., & Mazumder, P. (2017). Modeling and mitigation of static noise margin variation in subthreshold sram cells. IEEE Transactions on Circuits and Systems I: Regular Papers, 64(10), 2726.

Sachdeva, A., & Tomar, V. (2020) Statistical stability characterization of schmitt trigger based 10-t sram cell design. In 2020 7th international conference on signal processing and integrated networks (SPIN) (IEEE) (pp. 1000–1005).

Qiu, H., Mizutani, T., Saraya, T., & Hiramoto, T. (2015). Comparison and statistical analysis of four write stability metrics in bulk cmos static random access memory cells. Japanese Journal of Applied Physics, 54(4S), 04DC09.

Dasgupta, S., et al. (2017). Compact analytical model to extract write static noise margin (wsnm) for sram cell at 45-nm and 65-nm nodes. IEEE Transactions on Semiconductor Manufacturing, 31(1), 136.

Kulkarni, J. P., Kim, K., & Roy, K. (2007). A 160 mv robust schmitt trigger based subthreshold sram. IEEE Journal of Solid-State Circuits, 42(10), 2303.

Kumar, H. & Tomar, V. (2020). Design of low power with expanded noise margin subthreshold 12t sram cell for ultra low power devices. Journal of Circuits, Systems and Computers, 30(6), 2150106.

Jiao, H., Qiu, Y., & Kursun, V. (2016). Low power and robust memory circuits with asymmetrical ground gating. Microelectronics Journal, 48, 109.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work reported in this paper.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sachdeva, A., Tomar, V.K. A Multi-bit Error Upset Immune 12T SRAM Cell for 5G Satellite Communications. Wireless Pers Commun 120, 2201–2225 (2021). https://doi.org/10.1007/s11277-021-08462-8

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11277-021-08462-8