Abstract

A new gridless router to improve the yield of IC layout is presented. The improvement of yield is achieved by reducing the critical areas where the circuit failures are likely to happen. This gridless area router benefits from a novel cost function to compute critical areas during routing process, and heuristically lays the patterns on the chip area where it is less possible to induce critical area. The router also takes other objectives into consideration, such as routing completion rate and nets length. It takes advantage of gridless routing to gain more flexibility and a higher completion rate. The experimental results show that critical areas are effectively decreased by 21% on average while maintaining the routing completion rate over 99%.

Similar content being viewed by others

References

Chiluvuri V, Koren I. Layout synthesis techniques for yield enhancement. IEEE Trans. Semiconductor Manufacturing, 1995, 8(2): 178–187.

Kahng A B. Design for yield needed for further scaling. Electronics Systems and Software, 2004, 2(2): 48.

Koren I. Should yield be a design objective? In Proc. IEEE 2000 First International Symposium on Quality Electronic Design, San Jose, CA, March, 2000, pp.115–120.

Edenfeld D, Kahng A, Rodgers M, Zorian Y. 2003 Technology Roadmap for Semiconductors. Computer, 2004, 37(1): 47–56.

Raghvendra S, Hurat P. DFM: Linking design and manufacturing. In Proc. International Conference on VLSI Design, Kolkata, India, Jan. 2005, pp.705–708.

Bourai Y, Shi C J R. Layout compaction for yield optimization via critical area minimization. In Proc. Design, Automation and Test in Europe Conference and Exhibition, Paris, France, March 2000, pp.122–125.

Allan G A. Targeted layout modifications for semiconductor yield-reliability enhancement. IEEE Trans. Semiconductor Manufacturing, Nov. 2004, 17(4): 573–581.

Kuo S Y. YOR: A yield-optimizing routing algorithm by minimizing critical areas and vias. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, Sept. 1993, 12(9): 1303–1311.

Minghorng Lai, Wong D F. Maze routing with buffer insertion and wiresizing. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, Oct. 2002, 21(10): 1205–1209.

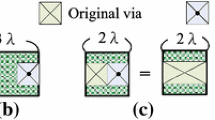

Gang Xu, Li-Da Huang, Pan D Z, Wong M D F. Redundant-via enhanced maze routing for yield improvement. In Proc. Asia and South Pacific Design Automation Conference, Shanghai, China, Jan. 18–21, 2005, pp.1148–1151.

Hailong Yao, Yici Cai, Qiang Zhou, Xianlong Hong. Multilevel routing with redundant via insertion. IEEE Trans. Circuits and Systems-II: Express Briefs, 2006, 53(10): 1148–1152.

Li-Da Huang, Wong M D F. Optical proximity correction (OPC) — Friendly maze routing. In Proc. Design Automation Conference, San Diego, CA, Jun. 2004, pp.186–191.

Stapper C H. Modeling of integrated circuit defect sensitivities. IBM J. Res. Develop., Nov. 1983, 27: 549–557.

Xue H, Di C, Jess J A G. Fast multi-layer critical area computation. In Proc. IEEE Int. Workshop on Defect and Fault Tolerance in VLSI Systems, Venice, Italy, Oct. 1993, pp.117–124.

Ousterhout J K. Corner stitching: A data-structuring technique for VLSI layout tools. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, 1984, 3(1): 87–100.

Nilsson N. Problem-Solving Methods in Artificial Intelligence. New York: McGraw-Hill, 1971.

Zhang Y, Wang B, Cai Y, Hong X. Area routing oriented hierarchical corner stitching with partial bin. In Proc. Asia and South Pacific Design Automation Conference, Yokohama, Japa, Jan. 25–28, 2000, pp.105–110.

Tsai C C, Chen S J, Feng W S. An H-V alternating router. IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, 1992, 11(8): 976–991.

Author information

Authors and Affiliations

Corresponding author

Additional information

Supported by the National Natural Science Foundation of China (NSFC) under Grant No. 60476014.

Electronic supplementary material

Rights and permissions

About this article

Cite this article

Zhou, Q., Cai, YC., Li, D. et al. A Yield-Driven Gridless Router. J Comput Sci Technol 22, 653–660 (2007). https://doi.org/10.1007/s11390-007-9092-9

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11390-007-9092-9