Abstract

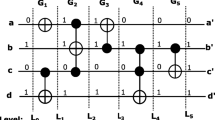

Integrated circuit (IC) camouflaging technique has been applied as a countermeasure against reverse engineering (RE). However, its effectiveness is threatened by a boolean satisfiability (SAT) based de-camouflaging attack, which is able to restore the camouflaged circuit within only minutes. As a defense to the SAT-based de-camouflaging attack, a brand new camouflaging strategy (called CamoPerturb) has been proposed recently, which perturbs one minterm by changing one gate’s functionality and then restores the perturbed circuit with a separated camouflaged block, achieving good resistance against the SAT-based attack. In this paper, we analyze the security vulnerabilities of CamoPerturb by illustrating the mechanism of minterm perturbation induced by gate replacement, then propose an attack to restore the changed gate’s functionality, and recover the camouflaged circuit. The attack algorithm is facilitated by sensitization and implication principles in automatic test pattern generation (ATPG) techniques. Experimental results demonstrate that our method is able to restore the camouflaged circuits with very little time consumption.

Similar content being viewed by others

References

Rajendran J, Sinanoglu O, Karri R. VLSI testing based security metric for IC camouflaging. In Proc. the 44th IEEE International Test Conference, September 2013.

Torrance R, James D. The state-of-the-art in semiconductor reverse engineering. In Proc. the 48th Design Automation Conference, June 2011, pp.333-338.

Yasin M, Mazumdar B, Sinanoglu O, Rajendran J. CamoPerturb: Secure IC camouflaging for minterm protection. In Proc. the 35th International Conference on Computer-Aided Design, November 2016, Article No. 29.

Chow L W, Baukus J P, Wang B J et al. Camouflaging a standard cell based integrated circuit. US Patent 8151235, April 3, 2012. http://www.freepatentsonline.com/8151235.html, Dec. 2017.

Cocchi R P, Baukus J P, Wang B J et al. Building block for a secure CMOS logic cell library. US Patent 8111089, Feb. 7, 2012. http://www.freepatentsonline.com/8111089.html, Dec. 2017.

Shiozaki M, Hori R, Fujino T. Diffusion programmable device: The device to prevent reverse engineering. American Journal of Surgery, 2014, 12(3): 428-429.

Cocchi R P, Baukus J P, Chow L W et al. Circuit camouflage integration for hardware IP protection. In Proc. the 51th Annual Design Automation Conference. June 2014.

Chow L W, Clark M W, Harbison G J, Baukus J P. Conductive channel pseudo block process and circuit to inhibit reverse engineering. US Patent 7049667, May 23, 2006. http://www.freepatentsonline.com/7049667.html, Dec. 2017.

Massad M E, Garg S, Tripunitara M V. Integrated circuit (IC) decamouflaging: Reverse engineering camouflaged ICs within minutes. In Proc. the 22nd Annual Network and Distributed System Security Symposium, February 2015.

Liu D, Yu C X, Zhang X Y, Holcomb D. Oracle-guided incremental SAT solving to reverse engineer camouflaged logic circuits. In Proc. Design, Automation & Test in Europe Conference & Exhibition, March 2016, pp.433-438.

Li M, Shamsi K, Meade T, Zhao Z, Yu B, Jin Y E, Pan D Z. Provably secure camouflaging strategy for IC protection. In Proc. the 35th International Conference on Computer-Aided Design, November 2016, Article No. 28.

Rajendran J, Sam M, Sinanoglu O, Karri R. Security analysis of integrated circuit camouflaging. In Proc. the 2013 ACM SIGSAC Conf. Computer & Communications Security, November 2013, pp.709-720.

Larrabee T. Test pattern generation using Boolean satisfiability. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 1992, 11(1): 4-15.

Eén N, Sörensson N. Temporal induction by incremental SAT solving. Electronic Notes in Theoretical Computer Science, 2003, 89(4): 543-560.

Eén N, Sörensson N. An extensible SAT-solver. In Proc. International Conference on Theory and Applications of Satisfiability Testing, May 2003, pp.502-518.

Bushnell M, Agrawal V. Essentials of Electronic Testing for Digital, Memory and Mixed-Signal VLSI Circuits. Springer, 2014.

Brglez F, Bryan D, Kozminski K. Combinational profiles of sequential benchmark circuits. In Proc. IEEE International Symposium on Circuits and Systems, May 1989, pp.1929-1934.

Brayton R, Mishchenko A. ABC: An academic industrial-strength verification tool. In Proc. the 22nd International Conference on Computer Aided Verification. July 2010, pp.24-40.

Lee H K, Ha D S. Atalanta: An efficient ATPG for combinational circuits. Technical Report, Department of Electrical Engineering, Virginia Polytechnic Institute and State University, 1993.

Author information

Authors and Affiliations

Corresponding author

Electronic supplementary material

Below is the link to the electronic supplementary material.

ESM 1

(PDF 276 kb)

Rights and permissions

About this article

Cite this article

Jiang, S., Xu, N., Wang, XY. et al. An Efficient Technique to Reverse Engineer Minterm Protection Based Camouflaged Circuit. J. Comput. Sci. Technol. 33, 998–1006 (2018). https://doi.org/10.1007/s11390-018-1870-z

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11390-018-1870-z