Abstract

The nanoelectronics industry is facing historical challenges to scale down CMOS devices to meet demands for low voltage, low power, high performance and increased functionality. Using new materials and devices architectures is necessary. HiK gate dielectrics and metal gates have been introduced and have shown their ability to reduce power consumption. Fully depleted ultra-thin SOI devices are a good alternative to bulk for low power applications. Multigate devices are the current goal in device architecture to increase MOSFET drivability, reduce power, and allow new opportunities for future applications. Thin film based solutions will be necessary in the future because of fundamental limitations on gate capacitance scaling and system integration requirements. Exploiting 3D device stacking via wafer bonding could be a good way to introduce new materials (HiK, strained Si, hybrid orientations, Ge, III-Vs, Carbon-based materials, graphene and CNTs, and functional molecules) and continue increasing integration density. Si based CMOS will be scaled beyond the ITRS as the System-on-Chip/Wafer Platform.

Similar content being viewed by others

References

ITRS. International Technology Roadmap of Semiconductors, 2009 ed. http://www.Itrs.net

Iwai H. Future semiconductor manufacturing: challenges and Opportunities. In: IEDM, San Francisco, 2004. 11–14

Deleonibus S, Caillat C, Guegan G, et al. A 20-nm physical gate length NMOSFET featuring 1.2 nm gate oxide, shallow implanted source and drain and bf2 pockets. IEEE Electron Dev Lett, 2000, 21: 173–175

Bertrand G, Deleonibus S, Previtali B. et al. Towards the limits of conventional MOSFETs: case of sub 30 nm NMOS devices. Solid State Electron, 2004, 48: 505–509

Natori K. Ballistic metal-oxide-semiconductor field effect transistor. J Appl Phys, 1994, 76: 4879–4890

Assad F, Ren Z, Vasileska D, et al. On the performance limits for Si MOSFET’s:A theoretical study. IEEE Trans Electron Dev, 2000, 47: 232–240

Barral V, Poiroux T, Andrieu F, et al. Strained FDSOI CMOS technology scalability down to 2.5 nm film thickness and 18nm gate length with a TiN/HfO2 gate stack. In: IEDM, Washington, 2007. 61–64

Barral V, Poiroux T, Munteanu D, et al. Experimental investigation on the quasi-ballistic transport: part II-backscattering coefficient extraction and link with the mobility. IEEE Trans Electron Dev, 2009, 56: 420–430

Barral V, Poiroux T, Saint-Martin J, et al. Experimental investigation on the quasi-ballistic transport: part I-determination of a new backscattering coefficient extraction methodology. IEEE Trans Electron Dev, 2009, 56: 408–419

Schockley W. Problems related to p − n junctions in silicon. Solid-State Electron, 1961, 2: 35–60; IN9–IN10, 61–67

Deleonibus S. Electronic Devices Architectures for the NANO-CMOS Era. Singapore: PanStanford Publish, 2008. http://www.ioffe.ru/SVA/NSM/Semicond/

Ohguro T, Sugiyama N, Imai S, et al. High performance SOI DTMOS using a retrograde base with a low impurity surface channel. IEEE Trans Electron Dev, 1998, 4: 710–716

Emst T, Ducroquet F, Hartmann J M, et al. A new Si:C epitaxial channel nMOSFET architecture with improved drivability and short-channel characteristics. In: VLSI Tech Symp, Kyoto, 2003. 51–52

Weber O, Andrieu F, Cassé M, et al. Experimental determination of mobility scattering mechanisms in Si/HfO2/TiN and SiGe:C/HfO2/TiN surface channel n- and p-MOSFETs. In: IEDM, San Francisco, 2004. 687–670

Weber O, Ducroquet F, Emst T, et al. 55 nm high mobility SiGe(:C) pMOSFETs with HfOz gate dielectric and TiN metal gate for advanced CMOS. In: VLSI Tech Symp, Honolulu, 2004, 42–43

Lee M L, Fitzgerald E A. Optimized strained Si/strained Ge dual-channel heterostructures for high mobility P- and N-MOSFETs. In: IEDM, Washington, 2003. 429–432

Weber O, Bogumilowicz Y, Ernst T, et al. Strained Si and Ge MOSFETs with high-k/metal gate stack for high mobility dual channel CMOS. In: IEDM, Washington, 2005. 137–140

Pelloie J L, Auberton-Hervé A J, Raynaud C, et al. SOI technology performance and modeling. In: ISSCC, San Francisco, 1999. 428

Lolivier J, Deleonibus S, Balestra F. Threshold voltage quantum simulations for ultra-thin silicon-on-insulator transistors. In: ECS Spring 2003 Proc, Paris, 2003. 379

Suk S D, Li M, Yeoh Y Y. Characteristics of sub 5nm Tri-gate nanowire MOSFETs with single and poly Si channels in SOI structure. In: VLSI Tech Symp, Kyoto, 2009. 142

Doris B, Ieong M, Kanarsky T, et al. Extreme Scaling with Ultra-Thin Si Channel MOSFETs. In: IEDM 2002 Tech Digest, San Francisco, 2002. 267–270

Hutin L, Vinet M, Poiroux T, et al. Dual metallic source and drain integration on planar single and double gate SOI CMOS down to 20 nm: performance and scalability assessment. In: IEDM, 2009. 45–48

Fenouillet-Beranger C, Denorme S, Icard B, et al. Fully-depleted SOI technology using high-k and single-metal gate for 32nm node LSTP applications featuring 0.179 μm2 6T-SRAM Bitcell. In: IEDM, Washington, 2007. 267–230

Weber O, Faynot O, Andrieu F, et al. High immunity to threshold voltage variability in undoped ultra-thin FDSOI MOSFETs and its physical understanding. In: IEDM, San Francisco, 2008. 176–179

Fenouillet-Beranger C, Thomas O, Perreau P, et al. Efficient multi-VT FDSOI technology with UTBOX for low power circuit Design. In: VLSI Tech Symp, 2010. 65–66

Weber O, Andrieu F, Mazurier J, et al. Work-function engineering in gate first technology for multi-VT dual-gate FDSOI CMOS on UTBOX. In: Electron Devices Meeting 2010, San Francisco, 2010. 59–61

Faynot O, Andrieu F, Weber O, et al. Planar fully depleted SOI technology: a powerful architecture for the 20nm node and beyond. In: Electron Devices Meeting 2010, San Francisco, 2010. 50–53

Andrieu F, Weber O, Mazurier J, et al. Low leakage and low variability ultra-thin body and buried oxide (UT2B) SOI technology for 20 nm low power CMOS and beyond. In: VLSI Tech Symp2010, Honolulu, 2010. 57–58

Andrieu F, Ernst T, Faynot O, et al. Co-integrated dual strained channels on fully depleted sSDOI CMOSFETs with HfO2/TiN gate stack down to 15 nm gate length. In: IEEE Intern SOI Conf, Honolulu, 2005. 223–225

Andrieu F, Ernst T, Lime F, et al. Experimental and comparative investigation of low and high field transport in substrate- and process-induced strained nanoscaled MOSFETs. In: VLSI Tech Symp 2005, Kyoto, 2005. 176–177

Andrieu F, Dupré C, Rochette F, et al. 25 nm short and narrow strained FDSOI with TiN/HfO2 gate stack. In: VLSI Tech. Symp., Honolulu, 2006. 168–169

Andrieu F, Faynot O, Rochette F, et al. Impact of mobility boosters (XsSOI, CESL, TiN gate) on the performance of the 〈100〉 and 〈110〉 oriented cMOSFETs for the 32 nm node. In: VLSI Tech. Symp. 2007, Kyoto, 2007. 50–51

Andrieu F, Allain F, Buj-Dufournet C, et al. Additivity between sSOI- and CESL-induced nMOSFETs performance boosts. In: SSDM 2007, Tokyo, 2007. 888–889

Barral V, Poiroux T, Rochette F, et al. Will strain be useful for the 10 nm quasi-ballistic FDSOI nMOSFET? An experimental study. In: VLSI Tech Symp. 2007, Kyoto, 2007. 128–129

Barral V, Poiroux T, Andrieu F, et al. Strained FDSOI CMOS technology scalability down to 2.5nm film thickness and 18nm gate length with a TiN/HfO2 gate stack. In: IEDM 2007, Washington, 2007. 61–64

Wong H S P, Chan K K, Taur Y. Self-aligned (top and bottom) double-gate MOSFET with a 25 nm thick silicon channel. In: IEDM 1997, Washington, 1997. 427–430

Yang F L, Chen H Y, Chen F C, et al. 25 nm CMOS omega FETs. In: IEDM 2002, San Francisco, 2002. 255–258

Poiroux T, Vinet M, Faynot O, et al. Multigate devices: advantages and challenges. Microelect Eng, 2005, 80: 378–385

Guarini K W, Solomon P M, Zhang Y, et al. Triple-self-aligned, planar double-gate MOSFETs: devices and Circuits. In: IEDM 2001, Washington, 2001. 425–428

Vinet M, Poiroux T, Widiez J, et al. Bonded planar double-metal-gate NMOS transistors down to 10 nm. IEEE Electron Dev Lett, 2005, 26: 317

Vinet M, Poiroux T, Widiez J, et al. Planar double gate CMOS transistors with 40nm metal gate for multipurpose applications. In: SSDM 2004, Tokyo, 2004. 768

Lolivier J, Widiez J, Vinet M, et al. Experimental comparison between double gate, ground plane and single gate SO1 CMOSFETs. In: ESSDERC 2004, Leuven, 2004. 77–80

Huang X, Lee W C, Kuo C, et al. Sub 50-nm FinFET: PMOS. In: IEDM 1999, Washington, 1999. 67–70

Doyle B, Boyanov B, Datta S, et al. Tri-gate fully-depleted CMOS transistors: fabrication, design and layout. In: VLSI Tech. Symp. 2003, Kyoto, 2003. 133–134

Jahan C, Faynot O, Cassé M, et al. Ω FETs transistors with TiN metal gate and HfO2 down to 10 nm. In: VLSI Tech Symp. 2005, Kyoto, 2005. 112–113

Park J T, Colinge J P, Diaz C H, et al. Pi-gate SOI MOSFET. IEEE Electron Dev Lett, 2001, 22: 405–406

Yang F L, Lee D H, Chen H Y, et al. 5nm-gate nanowire FinFET. In: VLSI Tech Symp. 2004, Honolulu, 2004. 196–197

Choi Y K, King T J, Hu C. Spacer FinFET: nanoscale double-gate CMOS technology for the terabit era. Solid State Electron, 2002, 46: 1595–1601

Lee H, Yu L E, Ryu S W, et al. Sub-5nm all-around gate FinFET for ultimate scaling. In: VLSI Tech Symp. 2006, Honolulu, 2006. 58–59

Ernst T, Dupré C, Isheden C, et al. Novel 3D integration process for highly scalable nano-beam stacked-channels GAA (NBG) FinFETs with HfO2/TiN gate stack. In: IEDM 2006, San Francisco, 2006. 997–1000

Ernst T, Duraffourg L, Dupré C, et al. Novel Si-based nanowire devices: Will they serve ultimate MOSFETs scaling or ultimate hybrid integration? In: IEDM 2008, San Francisco, 2008. 745–748

Yoon E J, Lee S Y, Kim S M, et al. Sub 30 nm multi-bridge-channel MOSFET (MBCFET) with metal gate electrode for ultra high performance application. In: IEDM 2004, San Francisco, 2004. 627–630

Bernard E, Ernst T, Guillaumot B, et al. Novel integration process and performances analysis of low STandby power (LSTP) 3D multi-channel CMOSFET (MCFET) on SOI with metal/high-k gate stack. In: VLSI Tech Symp. 2008, Honolulu, 2008. 16–17

Dupré C, Hubert A, Bécu S, et al. 15nm-diameter 3D stacked nanowires with independent gates operation: ϕ FET. In: IEDM 2008, San Francisco, 2008. 748–751

Thomas O, Guillaumot B, Ernst T, et al. A power-efficient improved-stability 6T SRAM cell in 45 nm multi-channel FET technology. In: ESSCIRC 2008, Edinburgh, 2008. 150–153

Tachi K, Casse M, Jang D, et al. Relationship between mobility and high-k interface properties in advanced Si and SiGe nanowires. In: IEDM2009, Baltimore, 2009. 313–316

Young K K. Analysis of conduction in fully depleted SO1 MOSFET’s. IEEE Trans Electron Dev, 1989, 36: 504–506

Yan R H, Ourmazd A, Lee K F. Scaling the Si MOSFET: from bulk to SO1 to bulk. IEEE Trans Electron Dev, 1992, 39: 1704

Suzuki K, Tanaka T, Tosaka Y, et al. Scaling theory for double-gate SO1 MOSFET’s. IEEE Trans Electron Dev, 1993, 40: 2326–2329

Auth C P, Plummer J D. Scaling theory for cylindrical, fully-depleted, surrounding-gate MOSFET’s. IEEE Electron Dev Lett, 1997, 18: 74–76

Rafhay Q, Clerc R, Coignus J, et al. Dark space, quantum capacitance and inversion capacitance in Si, Ge, GaAs and In0.53Ga0.47As nMOS capacitors. In: ULIS 2010, Glasgow, 2010. 50–53

Clavelier L, Damlencourt J F, Le Royer C, et al. High hole mobility GeOI pMOSFETs with high-k/metal gate on Ge condensation wafers. In: IEEE Intern.SOI Conf. 2007, Indian Wells, 2007. 19–20

Hutin L, Cassé M, Le Royer C, et al. 20nm Gate Length Trigate pFETs on Strained SGOI for High Performance CMOS VLSI Tech Symp 2010, Honolulu, 2010. 37–38

Mayer F, Le Royer C, Damlencourt J F, et al. Impact of SOI, Si1-xGexOI and GeOI substrates on CMOS compatible tunnel FET Performance. In: IEDM 2008, San Francisco, 2008. 163–166

Mazellier J P, Widiez J, Andrieu F, et al. First demonstration of heat dissipation improvement in CMOS technology using silicon-on-diamond (SOD) substrates. In: IEEE Int SOI Conf 2009, Foster City, 2009. 141–142

Zhang G, Wang X, Li X, et al. Carbon nanotubes: from growth, placement and assembly control to 60 mv/decade and sub-60 mv/decade tunnel transistors. In: IEDM 2006, San Francisco, 2006

Berger C, Song Z, Li X, et al. Electronic confinement and coherence in patterned epitaxial grapheme. Science, 2006, 312: 1191–1196

Lemme M C, Echtermeyer T J, Baus M, et al. A Graphene Field-Effect Device. IEEE Electron Dev Lett, 2007, 28: 282–284

Nishitami-Gamo N, Yasu E, Xiao C, et al. Sulfur doped homoepitaxial (001) diamond with n-type semiconductive properties. Diam Relat Mater, 20009: 941

Lagrange J P, Deneuville A, Gheeraert E. A large range of boron doping with low compensation ratio for homoepitaxial diamond films. Carbon, 1999, 37: 807–810

Oshima K, Cristoloveanu S, Guillaumot B, et al. Novel SOI-like structures for improved thermal dissipation. In: IEEE Intern SOI Conf. 2002, Williamsburg, 2002. 95–96

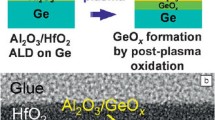

Batude P, Vinet M, Pouydebasque A, et al. Advances in 3D CMOS sequential integration. In: IEDM 2009, Baltimore, 2009. 346–349

Batude P, Vinet M, Pouydebasque A, et al. GeOI and SOI 3D monolithic cell integration for high density applications. VLSI Tech Symp. 2009, Kyoto, 2009. 166–167

Coudrain P, Batude P, Gagnard X, et al. Setting up 3D sequential integration for back-illuminated CMOS image sensors with highly miniaturized pixels with low temperature fully depleted SOI transistors. In: Electron Devices Meeting, San Francisco, 2008. 1–4

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Deleonibus, S. Ultra-thin films and multigate devices architectures for future CMOS scaling. Sci. China Inf. Sci. 54, 990–1003 (2011). https://doi.org/10.1007/s11432-011-4231-x

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-011-4231-x