Abstract

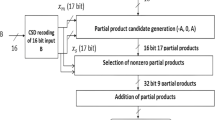

This paper presents a low-power design for a fixed coefficient multiplier, based on the canonic signed digit (CSD) method. The proposed technology overcomes the defects of the general CSD method by reducing system power and area substantially without additional logic. The theoretical basis and a design method are explained in detail in this paper. Our design technology was used to optimize a radio-frequency module. FPGA test results show that logic utilization is reduced by 25%, the total number of registers used is reduced by 23.02%, and the total block memory bits utilization is reduced by 20%. These results show that the proposed low-power design is an effective method.

Similar content being viewed by others

References

Avinash K, Ashwini S, Ahmed L. Adaptive interrouter links for low-power, area efficient and reliable network on Chip (NoC) architectures. In: ASP2DAC 2009. Athens: Ohio University, 2009. 1–126

Avinash K, Ahmed L, Janet W. Design of energy efficient channel buffers with router bypassing for network on chips. Qual Electron Des, 2009, (10): 826–832

Wong A C W, Kathiresan G, Chan K T, et al. A 1V wireless transceiver for an ultra low power SoC for biotelemetry applications. In: European Solid State Circuits Conference. Abingdon, 2007. 127–130

Malvar H S, Hallapuro A, Karczewicz M, et al. Low complexity transform and quantization in H.264/AVC. IEEE Trans Circ Syst Vid, 2003, (13): 598–603

Kang S M. Elements of low power design for integrated systems. In: Proceedings of the 2003 International Symposium on Low Power Electronics and Design. Seoul, 2003. 205–210

Parhi K K. A systematic approach for design of digit-serial signal processing architectures. IEEE Trans Circ Syst, 1991, (38): 358–375

Samueli H. An improved search algorithm for the design of multiplier less FIR filters with power-of-two coefficients. IEEE Trans Circ Syst, 1989, (36): 1044–1047

Yoo H, Anderdon D V. Hardware-efficient distributed arithmetic architecture for high-order digit filter. In: Proceedings of IEEE International Conference on Acoustics, Speed and Signal Processing. Knoxville, 2005. V125–V128

Xu F, Chang C H, Jong C C. Design of low-complexity FIR filters based on signed-powers-of-two coefficients with reusable common sub expression. IEEE Trans Comput Aided Des Circ Syst, 2007, (26): 1898–1907

Uppalapati H, Rastgar H, Ahmadi M, et al. Design of quadrature mirror filter banks with canonical signed digit coefficients using genetic algorithm. In: International Conference on Communications, Circuits and Systems. Hong Kong, 2005. 682–686

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Liu, H., Yuan, B. Low-power design and application based on CSD optimization for a fixed coefficient multiplier. Sci. China Inf. Sci. 54, 2443–2453 (2011). https://doi.org/10.1007/s11432-011-4317-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-011-4317-5