Abstract

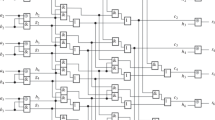

Addition of two binary numbers is a fundamental operation in electronic circuits. Several integer adder architectures have been proposed. Their formal properties are well known, but the proofs are either incomplete or difficult to find. In this paper, we present a formal proof for the correctness of prefix adders. Both sequential and parallel algorithms are formalized and proved. In contrast to previous proofs using higher order functions and rewriting systems, our work is based on first order recursive equations, which are familiar to the computer arithmetic community and are therefore understandable by people working on VLSI circuit design. This study sets up a basis for further work on formal proofs of computer arithmetic algorithms.

Similar content being viewed by others

References

Koren I. Computer Arithmetic Algorithms. Natick: A K Peters, 2002

Ladner R, Fischer M. Parallel prefix computation. J ACM, 1980, 27: 831–838

Lakshmivarahan S, Dhall S K. Parallel Computing Using the Prefix Problem. USA: Oxford University Press, 1994

Blelloch G E. Scans as primitive parallel operations. IEEE Trans Comput, 1989, 38: 1526–1538

Blelloch G E. Prefix sums and their applications. In: Synthesis of Parallel Algorithms. San Francisco: Morgan Kaufmann Publisher, 1993

Kogge P M, Stone H S. A parallel algorithm for the efficient solution of a general class of recurrence equations. IEEE Trans Comput, 1973, C-22: 786–793

Brent R P, Kung H T. A regular layout for parallel adders. IEEE Trans Comput, 1982, C-31: 260–264

O’donnell J T, Runger G. Derivation of a logarithmic time carry lookahead addition circuit. J Funct Program, 2004, 14: 697–713

Sheeran M. Hardware design and functional programming: A perfect match. J Univ Comput Sci, 2005, 11: 1135–1158

Kapur D, Subramaniam M. Mechanical verification of adder circuits using rewrite rulelaboratory. Form Method Syst Des, 1998, 13: 127–158

Chen G, Liu F. Proofs of correctness and properties of integer adder circuits. IEEE Trans Comput, 2010, 59: 134–136

Howie J M. Fundamentals of Semigroup Theory. USA: Oxford University Press, 1996

Knowles S. A family of adders. In: Proceedings of the 15th IEEE Symposium on Computer Arithmetic, Vail, USA, 2001. 277–281

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Liu, F., Tan, Q. & Mohamed, O.A. Formal proof of integer adders using all-prefix-sums operation. Sci. China Inf. Sci. 55, 1949–1960 (2012). https://doi.org/10.1007/s11432-011-4331-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-011-4331-7