Abstract

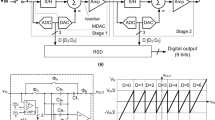

A 6-bit 2 GS/s ADC was implemented using a 65 nm digital CMOS technology. The design is based on a single-channel flash ADC architecture, and utilizes interpolating and averaging techniques. A two-stage CML-CMOS high-speed hybrid comparator is designed for optimal speed and power performance. The total power consumption of the converter is 52 mW and the area is 0.24 mm2. The ADC achieves 42.5 dB SFDR and 5.2 bit ENOB at input frequency of 123 MHz, and at Nyquist frequency 37.67 dB SFDR and 4.9 bit ENOB.

Similar content being viewed by others

References

Huang C C, Wang C Y, Wu J T. A CMOS 6-bit 16 GS/s time-interleaved ADC using digital background calibration techniques. IEEE J Solid-State Circ, 2011, 46: 848–858

Lin Y Z, Liu Y T, Chang S J. A 5-bit 4.2-GS/s flash ADC in 0.13-μm CMOS. In: Proceedings of Custom Integrated Circuits Conference, San Jose, 2007. 213–216

Choi M, Jungeun L, Jungho L, et al. A 6-bit 5-GSample/s Nyquist A/D converter in 65 nm CMOS. In: Proceedings of VLSI Circuits, Honolulu, 2008. 16–17

D’Amico S, Cocciolo G, De Matteis M, et al. A 6.9 mA 5 bits 90 nm 1 GS/s ADC without calibration for UWB application. Microelectron J, 2011, 42: 325–329

Shu Y S. A 6 b 3 GS/s 11 mW fully dynamic flash ADC in 40 nm CMOS with reduced number of comparators. In: Proceedings of VLSI Circuits, Honolulu, 2012. 26–27

Kimura H, Matsuzawa A, Nakamura T, et al. A 10-b 300-MHz interpolated-parallel A/D converter. IEEE J Solid-State Circ, 1993, 28: 438–446

Kattmann K, Barrow J. A technique for reducing differential non-linearity errors in flash A/D converters. In: Proceedings of IEEE International Solid-State Circuits Conference, San Francisco, 1991. 170–171

Scholtens P C S, Vertregt M. A 6-bit 1.6 Gsample/s flash ADC in 0.18-μm CMOS using averaging termination. IEEE J Solid-State Circ, 2002, 37: 1599–1609

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wang, H., Wang, T., Yao, Y. et al. A 6-bit 2 GS/s ADC in 65 nm CMOS. Sci. China Inf. Sci. 57, 1–5 (2014). https://doi.org/10.1007/s11432-014-5101-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-014-5101-0