Abstract

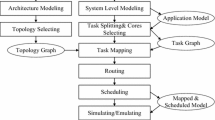

The flexibility of manycore systems to extensive applications is achieved by reconfiguring the interconnections between processing elements (PEs) and the function of PEs. The efficiency of the system is crucially determined by the mapping technique of applications. In this paper, a highly flexible reliability-aware application mapping approach is proposed for manycore network-on-chip (NoC) systems. A reliability cost model (RCM) is first presented to measure the reliability cost for a mapping pattern. This model uses the binary number 0/1 to model the reliability cost of each communication path. The overall reliability cost of a mapping pattern is evaluated by taking the cost of each path as a discrete random variable. Based on RCM, a mapping method called reliability cost ratio based branch and bound (RCRBB) is used. With this method, the best mapping among all the possible patterns is found efficiently by discarding those nonoptimal candidate mappings at early stages. The proposed application mapping approach with reliability awareness is applicable to various NoC topologies and routing algorithms, while other state-of-the-art approaches on the same topic are only limited to a specific topology and routing algorithm. Even for the same NoC architecture, the proposed approach shows significant superiority in many aspects. Experiments show that RCRBB achieves up to 9.07% reliability enhancement on average. Also, it outperforms other approaches in throughput and latency with a relatively low run time.

创新点

本文提出一种满足性能限制的可靠性优化任务映射算法, 该算法在基于片上网络互连(NoC)的众核系统上实现. 本文提出一种新的可靠性开销模型 (RCM) 来评估特定映射下的可靠性开销. 利用该模型, 本文提出一种基于可靠性开销比值的分支界定映射算法(RCRBB). 该算法通过在前期删除大量的非最优映射方式提升映射效率. 本文的方法可以适用于各类拓扑结构和路由算法的NoC, 而目前最新的同类方法只能局限于某些特定的结构. 实验证明, 与同类方法在相同NoC结构下相比, RCRBB在可靠性方面有9.07%的提升, 在吞吐率、延时以及运行时间方面, RCRBB也有较大的优势.

Similar content being viewed by others

References

Micheli D G, Benini L. Networks on Chip: Technology and Tools. Burlington, Massachusetts: Morgan Kaufmann, 2006. 1–19

Bjerregaard T, Mahadevan S. A survey of research and practices of network-on-chip. ACM Comp Surv (CSUR), 2006, 38: 1

Chou C L, Marculescu R. FARM: Fault-aware resource management in NoC-based multiprocessor platforms. In: Proceedings of Design, Automation & Test in Europe Conference & Exhibition. Grenoble, 2011. 1–6

Hu J, Marculescu R. Energy- and performance-aware mapping for regular NoC architectures. IEEE Trans Comput-Aided Des Integr Circuits Syst, 2005, 24: 551–562

Chang Y C, Chiu C T, Lin S Y, et al. On the design and analysis of fault tolerant NoC architecture using spare routers. In: Proceedings of the 16th Asia and South Pacific Design Automation Conference, Yokohama, 2011. 431–436

Kohler A, Schley G, Radetzki M. Fault tolerant network on chip switching with graceful performance degradation. IEEE Trans Comput-Aided Des Integr Circuits Syst, 2010, 29: 883–896

Salminen E, Kulmala A, Hamalainen T D. Survey of network-on-chip proposals. White Paper, OCP-IP, 2008. 1–13

Dong X, Deadlock-Free adaptive routing in meshes with fault-tolerance ability based on channel overlapping. IEEE Trans on Depend Secure Comp, 2011, 8: 74–88

Dong X, Zhang Y L, Pan Y. Practical deadlock-free fault-tolerant routing in meshes based on the planar network fault model. IEEE Trans on Comp, 2009, 58: 620–633

Jie W, A fault-tolerant and deadlock-free routing protocol in 2D meshes based on odd-even turn model. IEEE Trans Comp, 2003, 52: 1154–1169

Murali S, Atienza D, Benini L, et al. A multi-path routing strategy with guarantee in-order packet delivery and fault-tolerance for networks on chip. In: Proceedings of the 43rd annual Design Automation Conference. San Francisco, CA, 2006. 845–848

Ebrahimi M, Daneshtalab M, Plosila J, et al. Minimal-path fault-tolerant approach using connection-retaining strcuture in Networks-on-Chip. In: Proceedings of the 2013 Seventh IEEE/ACM International Symposium on Networks on Chip (NoCS), Tempe, AZ, 2013. 1–8

Ebrahimi M, Daneshtalab M. Plosila J, et al. MD: Minimal path-based fault-tolerant routing in on-Chip Networks. In: Proceedings of Asia and South Pacific Design Automation Conference (ASP-DAC), Yokohama, 2013. 35–40

Yan F G, Jin M, Qiao X L. Source localization based on symmetrical MUSIC and its statistical performance analysis. Sci China Inf Sci, 2013, 56: 062307(13), doi: 10.1007/s11432-013-4841-6 DOI

Khalili F, Zarandi H R. A reliability-aware multi-application mapping techinique in Networks-on-Chip. In: Proceedings of 2013 21st Euromicro International Conference on Parallel, Distributed and Network-Based Processing (PDP), Belfast, 2013. 478–485

Patooghy A, Tabkhi H, Miremadi S G. RMAP: A reliability-aware application mapping for Network-on-Chips. In: Proceedings of 2010 Third International Conference on Dependability (DEPEND), Venice, 2010. 112–117

Ababei C, Hia H S, Yadav O P, et al. Energy and reliability oriented mapping for regular networks-on-chip. In: Proceedings of the 2011 Fifth IEEE/ACM International Symposium on Networks on Chip (NoCS), Pittsburgh, 2011. 121–128

Marculescu R, Ogras U Y, Peh L S, et al. Outstanding research problems in NoC design: system, microarchitecture, and circuit perspectives. IEEE Trans Comput-Aided Des Integr Circuits Syst, 2009, 28: 3–21

Tsai W C, Zheng D Y, Chen S J, et al. A fault-tolerant NoC scheme using bidirectional channel. In: Proceedings of 2011 48th Design Automation Conference (DAC). New York, NY, 2011. 918–923

SoCDesigner, http://www.carbondesignsystems.com/soc-designer-plus/.

Sahu P K, Chattopadhyay S. A survey on application mapping strategies for Network-on-Chip design. J Syst Archit, 2013, 59: 60–76

Dick R P, Rhodes D L, Wolf W. TGFF: Task graphs for free. In: Proceedings of the 6th international workshop on Hardware/sofeware codesign. Seattle, WA, 1998. 97–101

Bertsimas D, Tsitsiklis J. Simulated annealing. Statist Sci, 1993, 8: 10–15

Van Der Tol E B, Jaspers E G. Mapping of MPEG-4 decoding on a flexible architecture platform. Proc SPIE 4674, Media Processors 2002, 1. doi: 10.1117.12.45.0.67

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Wu, C., Deng, C., Liu, L. et al. Reliability-aware mapping for various NoC topologies and routing algorithms under performance constraints. Sci. China Inf. Sci. 58, 1–14 (2015). https://doi.org/10.1007/s11432-014-5248-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11432-014-5248-8