Abstract

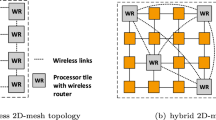

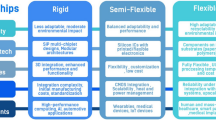

In this paper, we propose an intelligent partitioning approach of the system-on-chip (SoC) to improve the bendability and stretchability of flexible and stretchable systems. The proposed approach partitions the SoC intelligently into clusters of functional modules according to the communication flows and area constraint. Based on the communication volume between clusters, a heuristic algorithm is applied to map these clusters onto the 2D mesh network-on-chip (NoC) for co-optimization of communication energy and delay. Experimental results show that our approach can effectively partition the SoC into small ICs of the same size. The approach also reduces power consumption and communication delay by 10.64%–56.63% and 15.06%–50.30%, respectively.

Similar content being viewed by others

References

Wong W S, Salleo A. Flexible Electronics: Materials and Applications. Berlin: Springer, 2009

Sekitani T, Zschieschang U, Klauk H, et al. Flexible organic transistors and circuits with extreme bending stability. Nat Mater, 2010, 9: 1015–1022

Gupta U, Ogras U Y. Extending networks from chips to flexible and stretchable electronics. In: Proceedings of the 10th IEEE/ACM International Symposium on Networks-on-Chip (NOCS), Nara, 2016. 1–6

Council N R. Flexible Electronics for Security, Manufacturing, and Growth in the United States: Summary of a Symposium. Washington: The National Academies Press, 2013

Kim D H, Ahn J H, Choi W M, et al. Stretchable and foldable silicon integrated circuits. Science, 2008, 320: 507–511

Kim D H, Song J, Choi W M, et al. From the cover: materials and noncoplanar mesh designs for integrated circuits with linear elastic responses to extreme mechanical deformations. Proc Natl Acad Sci USA, 2008, 105: 18675–18680

Yoon J, Baca A J, Park S I, et al. Ultrathin silicon solar microcells for semitransparent, mechanically flexible and microconcentrator module designs. Nat Mater, 2008, 7: 907–915

Kim D H, Kim Y S, Wu J, et al. Flexible electronics: ultrathin silicon circuits with strain-isolation layers and mesh layouts for high-performance electronics on fabric, vinyl, leather, and paper. Adv Mater, 2009, 21: 3703–3707

Fusella E, Cilardo A. PhoNoCMap: an application mapping tool for photonic networks-on-chip. In: Proceedings of 2016 Design, Automation & Test in Europe Conference & Exhibition (DATE), Dresden, 2016. 289–292

Chen W, Deng C C, Liu L B, et al. An efficient application mapping approach for the co-optimization of reliability, energy, and performance in reconfigurable NoC architectures. IEEE Trans Comput-Aided Des Integr Circ Syst, 2015, 34: 1264–1277

Li J S, Pan Y. A fast and energy efficient branch and bound algorithm for NoC task mapping. In: Proceedings of the 33rd IEEE International Conference on Computer Design (ICCD), New York, 2015. 9–16

Bo H, Song C, Wei Z, et al. Application-specific network-on-chip synthesis with topology-aware floorplanning. In: Proceedings of the 25th Symposium on Integrated Circuits and Systems Design (SBCCI), Brasilia, 2012. 1–6

Ye T T, Benini L, Micheli G D. Analysis of power consumption on switch fabrics in network routers. In: Proceedings of 2002 Design Automation Conference, New Orleans, 2002. 524–529

Elmiligi H, Morgan A A, El-Kharashi M W, et al. A delay-aware topology-based design for networks-on-chip applications. In: Proceedings of the 4th International Design and Test Workshop (IDT), Riyadh, 2009. 1–5

Sivanandam S N, Deepa S N. Introduction to Genetic Algorithms. Berlin: Springer, 2008

Chatha K S, Srinivasan K. Layout aware design of mesh based NoC architectures. In: Proceedings of the 4th International Conference on Hardware/Software Codesign and System Synthesis (CODES+ISSS’ 06), Seoul, 2006. 136–141

Seiculescu C, Murali S, Benini L, et al. SunFloor 3D: a tool for networks on chip topology synthesis for 3-D systems on chips. IEEE Trans Comput-Aided Des Integr Circ Syst, 2010, 29: 1987–2000

Yu B, Dong S Q, Chen S, et al. Floorplanning and topology generation for application-specific network-on-chip. In: Proceedings of the 15th Asia and South Pacific Design Automation Conference (ASP-DAC), Taipei, 2010. 535–540

Dick R P, Rhodes D L, Wolf W. TGFF: task graphs for free. In: Proceedings of Hardware/Software Codesign, Seattle, 1998. 97–101

Shuang Y, Fen G, Gui F, et al. A two-phase floorplanning approach for application-specific network-on-chip. In: Proceedings of the 10th International Conference on ASIC, Shenzhen, 2013. 1–4

Zhong L L, Sheng J Y, Jing M E, et al. An optimized mapping algorithm based on simulated annealing for regular NoC architecture. In: Proceedings of the 9th IEEE International Conference on ASIC, Xiamen, 2011. 389–392

Li Z X, Liu Y, Cheng M S. Solving NoC mapping problem with improved particle swarm algorithm. In: Proceedings of the 6th International Conference on Advanced Computational Intelligence (ICACI), Hangzhou, 2013. 12–16

Palaniveloo V A, Ambrose J A, Sowmya A. Improving GA-based NoC mapping algorithms using a formal model. In: Proceedings of 2014 IEEE Computer Society Annual Symposium on VLSI, Tampa, 2014. 344–349

Acknowledgements

This work was supported by National Basic Research Program of China (Grant No. 2015CB351906), National Natural Science Foundation of China (Grant No. 61172030), and Programme of Introducing Talents of Discipline to Universities (111 Project) (Grant No. B12026).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Xu, C., Liu, Y. & Yang, Y. An intelligent partitioning approach of the system-on-chip for flexible and stretchable systems. Sci. China Inf. Sci. 61, 060415 (2018). https://doi.org/10.1007/s11432-017-9351-4

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11432-017-9351-4