Abstract

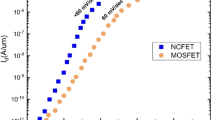

Power consumption has become one of the bottlenecks limiting the future development of integrated circuits. Tunnel FETs (TFETs) and negative capacitance FETs (NCFETs) can break the subthreshold swing limitation (60 mV/dec at room temperature) of conventional metal-oxide-semiconductor field-effect transistor (MOSFET) to reduce the operating voltage and thus power consumption. However, induced by the band-to-band tunneling mechanism, TFETs have a subthreshold swing degradation issue and relatively low ON current. Although NCFETs with ferroelectric/dielectric gate stack can theoretically maintain a high ON current comparable to conventional MOSFET, the physical origin of sub-60 SS is controversial and the mechanism of switching behavior in NCFET is still not clear. In this work, by experimentally investigating the whole negative differential capacitance process and its gate voltage amplification coefficient, an intrinsic issue of SS degradation with increased gate voltage is also found in NCFET for the first time. Based on the physical investigation and simulation results, it is shown that the intrinsic SS degradation in NCFET is resulting from the instant dielectric polarization response. Both the decrease of dielectric thickness and the increase of dielectric constant may lead to the severer SS degradation, which is not favorable for scaled NCFETs.

Similar content being viewed by others

References

Moore G E. Progress in digital integrated electronics. In: Proceedings of IEEE International Electron Devices Meeting, San Francisco, 1975. 11–13

Nowak E J. Maintaining the benefits of CMOS scaling when scaling bogs down. IBM J Res Dev, 2002, 46: 169–180

Ionescu A M, Riel H. Tunnel field-effect transistors as energy-efficient electronic switches. Nature, 2011, 479: 329–337

Seabaugh A C, Zhang Q. Low-voltage tunnel transistors for beyond CMOS logic. Proc IEEE, 2010, 98: 2095–2110

Jia R D, Chen L, Huang Q Q, et al. Complementary tunneling transistors based on WSe2/SnS2 van der Waals heterostructure. Sci China Inf Sci, 2020, 63: 149401

Nirschl T, Wang P F, Weber C, et al. The tunneling field effect transistor (TFET) as an add-on for ultra-low-voltage analog and digital processes. In: Proceedings of IEEE International Electron Devices Meeting, San Francisco, 2004. 195–198

Zhao Y, Huang Q Q, Huang R. A novel tunnel FET design through hybrid modulation with optimized subthreshold characteristics and high drive capability. Sci China Inf Sci, 2020, 63: 129402

Wu C, Huang Q, Zhao Y, et al. A novel tunnel FET design with stacked source configuration for average subthreshold swing reduction. IEEE Trans Electron Devices, 2016, 63: 5072–5076

Müller J, Böscke T S, Schröder U, et al. Ferroelectricity in simple binary ZrO2 and HfO2. Nano Lett, 2012, 12: 4318–4323

Boscke T, Muller J, Brauhaus D, et al. Ferroelectricity in hafnium oxide: CMOS compatible ferroelectric field effect transistors. In: Proceedings of International Electron Devices Meeting, San Francisco, 2011. 547–550

Khan A I, Bhowmik D, Yu P, et al. Experimental evidence of ferroelectric negative capacitance in nanoscale heterostructures. Appl Phys Lett, 2011, 99: 113501

Tu L, Wang X, Wang J, et al. Ferroelectric negative capacitance field effect transistor. Adv Electron Mater, 2018, 4: 1800231

Kobayashi M. A perspective on steep-subthreshold-slope negative-capacitance field-effect transistor. Appl Phys Express, 2018, 11: 110101

Zhou J, Han G, Li Q, et al. Ferroelectric HfZrOx Ge and GeSn PMOSFETs with sub-60 mV/decade subthreshold swing, negligible hysteresis, and improved Ids. In: Proceedings of IEEE International Electron Devices Meeting, San Francisco, 2016. 310–313

Si M, Su C J, Jiang C, et al. Steep-slope hysteresis-free negative capacitance MoS2 transistors. Nat Nanotech, 2018, 13: 24–28

McGuire F A, Lin Y C, Price K, et al. Sustained sub-60 mV/decade switching via the negative capacitance effect in MoS2 transistors. Nano Lett, 2017, 17: 4801–4806

Wang H, Yang M, Huang Q, et al. New insights into the physical origin of negative capacitance and hysteresis in NCFETs. In: Proceedings of IEEE International Electron Devices Meeting, San Francisco, 2018. 707–710

Wang H M, Huang Q Q, Yang M X, et al. Deep insight into the voltage amplification effect from ferroelectric negative capacitance. Sci China Inf Sci, 2019, 62: 89401

Phillips R. The Feynman lectures on physics. Physics Bulletin, 2013, 17: 367

Lee C K, Cho E, Lee H S, et al. First-principles study on doping and phase stability of HfO2. Phys Rev B, 2008, 78: 012102

Blaeser S, Glass S, Schulte-Braucks S, et al. Novel SiGe/Si line tunneling TFET with high Ion at low VDD and constant SS. In: Proceedings of IEEE International Electron Devices Meeting, San Francisco, 2015. 608–611

Huang Q, Huang R, Wu C, et al. Comprehensive performance reassessment of TFETs with a novel design by gate and source engineering from device/circuit perspective. In: Proceedings of IEEE International Electron Devices Meeting, San Francisco, 2014. 355–338

Jo J Y, Han H S, Yoon J G, et al. Domain switching kinetics in disordered ferroelectric thin films. Phys Rev Lett, 2007, 99: 267602

Acknowledgements

This work was supported by the National Key R&D Program of China (Grant No. 2018YFB2202800), National Natural Science Foundation of China (Grant Nos. 61851401, 61822401, 61927901, 61421005), and 111 Project (Grant No. B18001).

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

About this article

Cite this article

Yang, M., Huang, Q., Wang, K. et al. Physical investigation of subthreshold swing degradation behavior in negative capacitance FET. Sci. China Inf. Sci. 65, 162404 (2022). https://doi.org/10.1007/s11432-021-3283-5

Received:

Revised:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11432-021-3283-5