# Acceleration Techniques and Evaluation on Multicore CPU, GPU and FPGA for Image Processing and Super-Resolution.

Georgios Georgis · George Lentaris · Dionysios Reisis

Received: 2015 / Revised: 2016

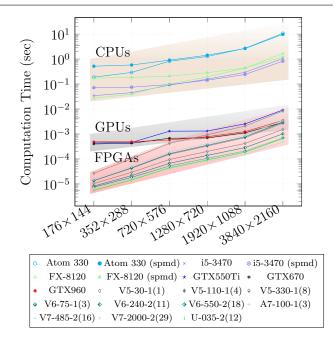

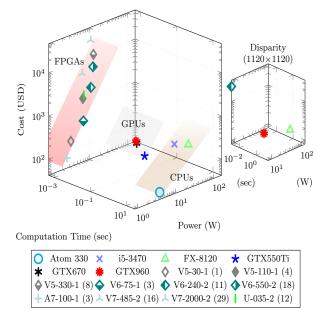

Abstract Super-Resolution (SR) techniques constitute a key element in image applications, which need highresolution reconstruction while in the worst case only a single low-resolution observation is available. SR techniques involve computationally demanding processes and thus researchers are currently focusing on SR performance acceleration. Aiming at improving the SR performance, the current paper builds up on the characteristics of the *L-SEABI* Super-Resolution (SR) method to introduce parallelization techniques for GPUs and FPGAs. The proposed techniques accelerate GPU reconstruction of Ultra-High Definition content, by achieving three (3x) times faster than the real-time performance on mid-range and previous generation devices and at least nine times (9x) faster than the real-time performance on high-end GPUs. The FPGA design leads to a scalable architecture performing four (4x) times faster than the real-time on low-end Xilinx Virtex 5 devices and sixty-nine times (69x) faster than the real-time on the Virtex 2000t. Moreover, we confirm the benefits of the proposed acceleration techniques by employing them on a different category of image-processing algorithms: on window-based Disparity functions, for which the proposed GPU technique shows an improvement over the CPU performance ranging from 14 times (14x) to 64 times (64x) while the proposed FPGA architecture provides 29x acceleration.

D. Reisis Electronics Laboratory Department of Physics National and Kapodistrian University of Athens, Greece Tel.: +0030-210-7276708 Fax: +0030-210-7276801 E-mail: dreisis@phys.uoa.gr

#### **1** Introduction

There is a wide range of image processing applications such as satellite and medical reconstruction/enhancement, high definition video broadcasting/processing, iris recognition and text images upgrade, for which the presence of high-resolution images is essential; meanwhile hardware limitations and/or an increasing implementation cost prevent the integration of high-resolution sensors in the systems supporting the above applications. Researchers and engineers addressed this problem by modeling image degradations and by introducing signal processing techniques to post process the acquired images. Such approaches exploit Super-resolution (SR) techniques that construct high-resolution (HR) images from several low-resolution (LR) observations and they thus trade off computational with hardware/implementation cost [1]. Consequently, current research focuses on improving the complexity and/or the running time performance of these processes [2] [3] [4] [5].

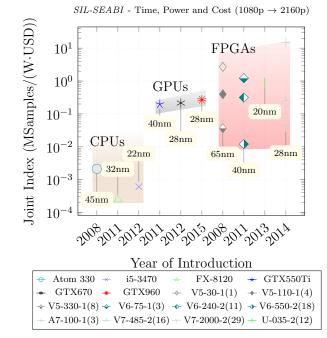

Aiming at providing an efficient solution for these processes the current manuscript proposes acceleration procedures of image processing techniques on multi-core, General Purpose Graphics Processing Units (GPUs) and Field-Programmable Gate Array (FPGA) platforms. It emphasizes the benefits of employing our *Low-complexity* Statistical Edge-Adaptive Back-projected Interpolation (L-SEABI) SR method [6] to speed up the reconstruction process by presenting efficient parallelization techniques for this method performing on GPUs and FPGAs. Our goal is to provide techniques and the corresponding implementations, which overcome the underlying platform's drawbacks and ultimately, to present a comprehensive performance assessment. To our knowledge, this assessment contributes to the current literature by jointly examining four parameters: i) absolute performance, ii) input size, iii) power consumption and iv) cost of ownership on multiple GPU, FPGA and multi-core CPUs designating low to high-end ICs. Additionally, to confirm the benefits of our acceleration techniques, we apply the entire design/optimization/evaluation process on a computationally demanding window-based Disparity algorithm. Finally, taking into account all the results on multiple platforms and devices presented by this work, we perform a comparative study at the platform level to evaluate the relative performance of FPGAs, GPUs and CPUs, in terms of speed and power consumption.

The proposed GPU parallelization/optimization techniques are effective for a large span of GPU architecture generations including the latest. We apply these techniques on multiple abstraction levels ranging from the design phase to the implementation API and exploit GPU architectural features to fuse increased throughput, instruction-level parallelism, with decreased latency and divergence [7]. These techniques allow the achievement of real-time (i.e., 30 frames/sec) GPU reconstruction of Ultra-High Definition content. Furthermore, as it will be demonstrated in the remaining sections of the paper, we achieve 3x faster performance (frame rate) than the conventional real-time requirement on mid-range and previous generation devices and at least 9x faster performance on the currently available high-end GPUs. Moreover, we introduce a parameterizable and highly scalable hardware architecture for L-SEABI and we evaluate its performance under varying parallelization factors and FPGA devices. By exploiting pixel and tasklevel pipelining, the proposed architecture performs four (4x) times faster than the conventional real-time requirement on low-end Virtex 5 devices and at most sixty-nine (69x) times faster than real-time on the Virtex 2000t device. When implementing the proposed architecture on a Virtex 7 485T device, we accomplish real-time processing of 182 Mpixel images, which is twice the resolution of upcoming 11K monitors. Furthermore, we comparatively evaluate the performance of SIL-SEABI among CPU, GPU and FPGA implementations, taking into account the power dissipation of each platform thereby estimating the achieved performance per Watt.

To enhance our evaluation and to strengthen the results reached from our SR study regarding the efficiency of our acceleration techniques, we consider a more computationally intensive scenario: the stereo correspondence problem and more specifically a Disparity algorithm, which computes a depth map based on metric aggregations with non-separable filters, left-right consistency checks and sub-pixel accuracy estimations. As with *SIL-SEABI*, we provide i) a GPU-accelerated implementation aiming at assessing bottlenecks through kernel profiling and ii) an FPGA architecture targeting the reduction of memory requirements. On a mid-range device, our GPU disparity implementation achieves an acceleration of over 14x against the fastest CPU examined for  $1120 \times 1120$  input and 200 disparities, while the proposed FPGA architecture attains an acceleration of 29x over the same CPU.

The manuscript is organized with the following Section presenting related work in the field of application acceleration through many-core architectures and FPGAs. Section 3 highlights the benefits of using *SIL-SEABI* through a quality evaluation of the SR algorithm both as stand-alone solution as well as an enhancement to more recent state-of-the-art SR. Section 4 presents a thorough profiling of the CPU and the coarse-grain GPU techniques leading to our optimized real-time GPU implementation. Section 5 delineates our scalable FPGA SR architecture and evaluates its performance. Section 6 extends our study onto the Disparity algorithm of Stereo Correspondence and section 7 displays our comparative study. Finally, section 8 concludes the paper.

# 2 Related Work

# 2.1 GPU Acceleration

Throughout the literature, many-core architectures have been widely employed as an efficient means to accelerating image and/or video processing. In the field of Super-Resolution, Freedman et al. [8] applied their single-image SR method on a GTX 480 GPU to achieve near realtime performance when upsampling from  $640 \times 360$ to  $1920 \times 1080$ . Using *dictionary-based* methods, the authors of [9] also provide a GPU implementation of their deformable image patch method. On a different approach, the authors of [3] and [4] exploited the *cuda*convnet library [10] to train their Convolutional Neural Network mapping between low and high-resolution images. More recently, Jung et al. employed the cuFFT[11] library in their deconvolution-based SR approach, achieving 53 ms for 2x upsampling to  $1920 \times 1080$  on a GTX 580 GPU device. GPUs have also been common early on in accelerating stereo vision applications, as the authors of [12] displayed. Their box filter window-based matching method attains real-time performance on a 8800GTX in  $1024 \times 768$  resolution for 50 disparities. Also, in [13], a hardware-efficient bilateral filter that features high accuracy and fast aggregation was proposed and implemented on a GTX 580 GPU. The authors of [14] [15] combine spatial with temporal-based processing to achieve real-time performance for  $320 \times 240$  resolutions on more recent GPU microarchitectures.

# 2.2 FPGA Acceleration

Whenever the application's computational characteristics necessitate a combination of high performance and low power consumption, mapping algorithms onto integrated circuits (ICs) seems like the most preferable solution. Field-Programmable Gate Arrays (FPGAs) consist of configurable logic blocks and embedded functions which altogether cater for such requirements with great flexibility, especially in problems pertinent to computer vision. For instance, Bowen et al. [16], combined a weighted-mean estimator with iterative refinement for multi-frame image upsampling to 720p at 61 frames per second (fps) on a Xilinx Virtex II FPGA. The authors of [17] implement a multi-frame Iterative Back-projection framework on a Virtex 4 FPGA to maintain a performance of 25 frames per second for 2 iterations on  $1024 \times 1024$  output.

In more recent developments, Sanada et al. [18] proposed an edge enhancement single-image Super Resolution architecture relying on integer operations which achieved a performance of  $60, 400 \times 400$  fps on an Altera ep2s130 Stratix II FPGA. Pérez et al. designed a stream-processing FPGA architecture to super-resolve data from micro-lens arrays in light-field cameras [19]. Their solution requires 105.9 ms to produce  $589 \times 589$ images from 291×291 micro-lenses on low-power FPGA platforms. Extending the problem to High Definition resolutions, the authors of [20] present a real-time Altera Aria II SR implementation. For more computationally intensive computer vision problems, Greisen et al. propose a window-based stereo matching FPGA implementation, which can compute 256 disparities of 1080p images in real-time [21]. The latter is feasible due to the authors' hierarchical approach, which initially computes the disparity for 16 times smaller images and then refines the upsampled disparity map by searching at a local pixel area. In general, a common feature of real-time stereo implementations is their increased resource cost as [22, 23] display.

#### 2.3 GPU-FPGA Comparison

Throughout the literature, the comparative assessment of performance between GPUs and FPGAs is based on accelerating well-known algorithms or generic implementations of a specific algorithmic category. For instance, Che et al. [24] employ a 8800GTX GPU and a Virtex II FPGA to examine Gaussian Elimination used in linear algebra, the DES used in cryptography and the Needleman-Wunsch algorithm used in DNA sequence alignment. The work in [25] proposes fully customized

Cholesky Decomposition implementations on the highend GTX 480 and Virtex 6 xc6vsx475t. The authors of [26] assess a wide range of applications (i.e., random number generation, matrix multiplication, parallel reduction and N-body simulation) on a GTX 285 and the HC-1 HPC multi-FPGA platform. In the field of computer vision, Kalarot et al. [27] implement a generic disparity algorithm on the GTX 280 and the Altera Stratix III platforms. A complete blood vessel detection system from medical images [28] is implemented on a GTX 295 GPU and a Spartan-3 FPGA, while more recently, a) Pietron et al. [29] compare a human skin classifier implementation on a Tesla m2090 and a Virtex 5 device and b) the ceramic tile defect detection algorithm of [30] is evaluated on the 9800GT GPU and three different FPGAs. In a slightly different direction, the authors of [31] evaluate the performance of High-Level Synthesis of GPU to FPGA stereo matching code.

The above literature survey leads to the conclusion (to be revised by our current work) that, GPUs are more suitable for SIMD computations with no interdependencies. They enable easier migration from a conventional software implementation, provide flexibility whenever the designer needs to implement changes and present a low total cost of ownership. On the other hand, they are less efficient in applications requiring a high amount of and/or irregular memory accesses, extensive synchronization and, finally, they consume more power. FPGAs, being more suitable for bit-level streaming operations, provide a higher level of control over the implementation's details. To their advantage is the fact that they combine high throughput, low power consumption, feature deterministic performance and resource cost. They are though more complex to program/customize, require thorough comprehension of the underlying algorithm and are not fully suitable for a) applications of high dataflow complexity or b) large input problems due to their restricted memory resources.

Focusing on improving solutions for image processing problems, this work presents parallelization techniques for the low-complexity *SIL-SEABI* SR algorithm [6]. As a preface to the *SIL-SEABI* parallelization, the following section stresses the advantages of using it as an enhancement to well-established and more recent state-of-the-art SR techniques.

# 3 The *L-SEABI* Algorithm as a standalone SR solution and State-of-the-Art enhancement

Our proposed *L-SEABI* Super-Resolution algorithm [6], achieves objective quality comparable to highly involved SR methods at significantly lower computational cost,

Table 1: Objective comparison of the *L-SEABI* algorithm against its single iteration case, its construction phase, the *NARM* SR and the Super-Resolution method using Deformable Patches (scaling factor f=2). All algorithms use the parameters proposed by their authors. Lower BRISQUE indicates higher quality.

| $\mathbf{N}$  | lethod:           | L-               | SIL-    | L-      | NARM    | DPSR    |

|---------------|-------------------|------------------|---------|---------|---------|---------|

| ou            | tput size         | $\mathbf{SEABI}$ | SEABI   | SEAI    | [36]    | [9]     |

|               | QCIF              | 0.9114           | 0.9086  | 0.9013  | 0.9278  | 0.9106  |

| Σ             | CIF               | 0.8763           | 0.8743  | 0.8604  | 0.8817  | 0.8834  |

| $\mathbf{SI}$ | SD1               | 0.9702           | 0.9679  | 0.9652  | 0.9730  | 0.9751  |

| MISSIM        | 720p              | 0.9403           | 0.9567  | 0.9537  | 0.9618  | 0.9636  |

|               | $1080 \mathrm{p}$ | 0.9796           | 0.9784  | 0.9783  | 0.9808  | 0.9816  |

|               | $2160 \mathrm{p}$ | 0.9880           | 0.9879  | 0.9874  | 0.9887  | 0.9883  |

|               | avg               | 0.9474           | 0.9456  | 0.9411  | 0.9523  | 0.9504  |

| 63            | QCIF              | 39.9237          | 43.5880 | 42.5035 | 39.7551 | 30.1888 |

| BRISQUE       | CIF               | 33.8815          | 36.1080 | 33.0046 | 45.2763 | 42.7670 |

| S.            | SD1               | 42.7928          | 44.4549 | 47.5913 | 46.7715 | 38.9799 |

| SIS           | 720p              | 41.6382          | 43.5580 | 46.1487 | 46.9208 | 41.8770 |

| BI            | $1080 \mathrm{p}$ | 40.4554          | 42.0595 | 46.7294 | 47.1687 | 44.9506 |

|               | $2160 \mathrm{p}$ | 56.8680          | 57.9444 | 58.4345 | 59.8403 | 55.7759 |

|               | avg               | 42.5948          | 44.6188 | 45.7353 | 47.6221 | 42.4232 |

i.e. 3 orders of magnitude less execution time. It consists of a construction phase which is executed once and a refinement phase which is iterative. The single iteration case of *L-SEABI* [6], namely *SIL-SEABI*, further reduces the execution time by an order of magnitude at the expense of negligible quality degradation.

Comparison to the state-of-the-art shows [6] that L-SEABI is faster than a) dictionary-based methods such as the Sparse Representation with over-complete dictionaries [32], the Nonlocal Similarity Adaptive Regularization [33] (ASDS-AR-NL) and the Anchored Neighborhood Regression (ANR) [2], b) Bayesian prior methods such as the Norm l1 [34], and better than c) *IBP*based methods such as the Nonlocal Iterative Back-Projection [35] (*NLIBP*). More recently, the authors in [36] proposed the concept of a nonlocal autoregressive model (NARM) i.e. the adaptive exploitation of nonlocal image redundancies in a sparse representation context to improve the performance of the standard sparse representation model. Authors in [9] also enhance the sparse-representation approach by proposing a regularized deformation field instead of fixed vector patches (i.e., Deformable Patch Super-Resolution, DPSR). Common ground in the aforementioned state-of-the-art methods is an initial reconstruction step which builds an initial estimation image through bicubic interpolation.

Motivated by the result that L-SEABI can increase the quality of common interpolation methods we use L-SEABI to improve the performance of state-of-theart SR. Ergo, this section presents the application of a) L-SEABI, b) SIL-SEABI and c) their construction phase only (noted as L-SEAI), in place of the initial reconstruction step of the [32,33,2,35,9,36] methods to upsample each low-resolution image by a factor of two in each dimension. The output quality is measured by employing the full-reference MSSIM [37] and the no-reference BRISQUE [38] metrics.

Table 1 presents the average MSSIM and BRISQUE metrics for *L-SEABI*, *SIL-SEABI*, *L-SEAI*, versus the more recent *NARM* and *DPSR* methods of the dataset used in [6] (26 images in resolutions from  $176 \times 144$  up to  $3840 \times 2160$ ). The results display that appending adaptive iterations to *L-SEAI* marginally increases the output quality with respect to the MSSIM metric, though the difference is more pronounced with BRISQUE. All *L-SEABI* cases perform comparably to the *NARM* and *DPSR* methods and even achieve higher quality when considering BRISQUE. These results are consistent with those documented in [6] regarding dictionary-based methods processing a single image.

Table 2 displays the average per resolution quality difference between the results obtained by the methods in [32, 33, 2, 35, 9, 36] when using L-SEABI/SIL-SEABI/L-SEAI and the results obtained by the same methods when using the parameters proposed by their respective authors in place of their construction phase. Providing alternative initialization to the method in [35] results in a slight MSSIM degradation of 0.08 on average.  $\Delta$ BRISQUE on the other hand signifies a quality increase, especially when using the L-SEABI/SIL-SEABI methods in 720p or higher resolutions. Note that the method in [35] as proposed by the authors performs 20 back-projection iterations which, when combined with the already back-projected result of L-SEABI/SIL-SEABI oversharpen the image. Thus, in NLIBP, using the L-SEAI produces more balanced results in all resolutions while L-SEABI and SIL-SEABI can be used in high-definition content. Similar results were obtained when considering the more robust ANRmethod; we measure an average MSSIM degradation of 0.02 while BRISQUE favors the application of L-SEABI/SIL-SEABI by displaying a quality increase in almost all resolutions. When augmenting the method in [32] we measure similar MSSIM results to the ANR. L-SEABI and SIL-SEABI now increase quality under all resolutions when considering BRISQUE. Regarding NARM and ASDS-AR-NL, MSSIM displays a negligible increase of approximately 0.002, while BRISQUE shows that SIL-SEABI and L-SEABI respectively provide the highest quality in all resolutions. Our low complexity methods also enhance the quality of DPSR, by 0.005 and 2.63 when evaluating MSSIM and BRISQUE respectively. Therefore, the above results show that in most cases, the SIL-SEABI algorithm can be used to further

Table 2: Per resolution objective comparison of state-of-the-art SR algorithms (scaling factor f=2) when using *L-SEABI* (a), *SIL-SEABI* (b) and *L-SEAI* (c) as their initial reconstruction phase against the parameters proposed by their authors. Lower  $\Delta$ BRISQUE indicates higher quality.

| $\downarrow \mathbf{Metric}$ |                   | $\mathbf{Algorithm} \rightarrow$ | NLIBP    | ANR                                      | Yang et al. | NARM     | DPSR     | ASDS-AR-NL |

|------------------------------|-------------------|----------------------------------|----------|------------------------------------------|-------------|----------|----------|------------|

| output size↓                 |                   | Initialization                   | [35]     | [2]                                      | [32]        | [36]     | [9]      | [33]       |

|                              |                   | (a)                              | -0.07074 | -0.01943                                 | -0.01730    | 0.00116  | 0.00276  | 0.00171    |

| Σ                            | $720 \mathrm{p}$  | (b)                              | -0.07234 | -0.02162                                 | -0.01914    | 0.00113  | 0.00267  | 0.00169    |

| AMSSIM                       |                   | (c)                              | -0.01511 | -0.01082                                 | -0.01407    | 0.00114  | 0.00206  | 0.00164    |

| W.                           | 1080p             | (a)                              | -0.05187 | -0.01130                                 | -0.01427    | 0.00128  | 0.00087  | 0.00168    |

| N                            |                   | (b)                              | -0.05229 | -0.01223                                 | -0.01473    | 0.00126  | 0.00083  | 0.00168    |

|                              |                   | (c)                              | -0.02102 | -0.00564                                 | -0.00973    | 0.00125  | 0.00064  | 0.00165    |

| ۲٦                           |                   | (a)                              | -8.77396 | -2.94443                                 | -6.10462    | 0.05638  | -0.93106 | -0.0634    |

| 5                            | $720 \mathrm{p}$  | (b)                              | -5.48932 | -2.42523                                 | -4.26859    | -0.38838 | -0.83522 | -0.07618   |

| $s_{\rm Q}$                  |                   | (c)                              | -5.10736 | -0.39096 $-0.25632$ $0.09672$ $-0.79050$ | -0.79050    | -0.03506 |          |            |

| ABRISQUE                     |                   | (a)                              | -7.86562 | -7.99265                                 | -10.8402    | 1.36240  | -1.83855 | -0.01110   |

| $\Delta E$                   | $1080 \mathrm{p}$ | (b)                              | -4.88077 | -7.44972                                 | -9.51325    | 0.48452  | -1.76727 | 0.00032    |

|                              |                   | (c)                              | -3.97212 | -2.69070                                 | -3.31287    | 0.70232  | -1.56985 | -0.00012   |

(a) normal SR: [36]

BRISQUE: 39.3129

MSSIM: 0.865780

(b) [36]+*SIL-SEABI*

(b) [36]+*SIL-SEABI* MSSIM: 0.869826 BRISQUE: 38.4339

(c) normal SR: [32]

MSSIM: 0.863308

BRISQUE: 37.0668

(d) [32]+*SIL-SEABI* MSSIM: 0.837666 BRISQUE: 33.3080

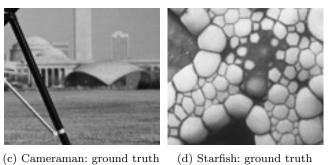

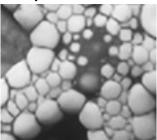

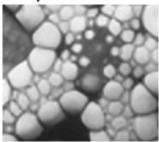

Fig. 1: Subjective comparison of [36], [32]: normal execution and enhanced with SIL-SEABI (f = 2).

improve state-of-the-art SR quality, as evaluated objectively by the MSSIM and BRISQUE metrics. Please see Appendix A for Table 9 which includes the results for all resolutions.

To subjectively assess state-of-the-art SR enhancement based on our methods, in Fig. 1 we present the output of [36] and [32] when processing the  $256 \times 256$ *Cameraman*, image. Using *SIL-SEABI* to complement *NARM*, (Fig. 1b) noticeably reduces the aliasing effects of the method. When we employ *SIL-SEABI* to initialize [32] (Fig. 1d) the results display a perceptible contrast enhancement. Similar results (i.e., aliasing reduction and contrast enhancement) can be observed when *SIL-SEABI* is applied before *DPSR* [9] and *ANR* [2] respectively. Please see Fig. 17 in Appendix A which displays subjective results for 4 different images.

#### 4 Acceleration of L-SEABI on GPU

The current section presents first, the strategy followed for parallelizing L-SEABI on GPU and second, the

implementation, optimization issues, and performance evaluation.

#### 4.1 Implementation Strategy: CPU to GPU

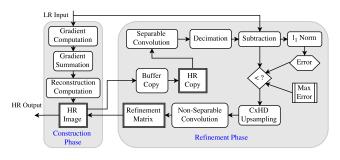

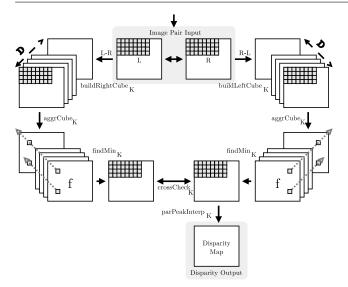

This section describes the steps leading from a *SIL-SEABI* CPU implementation to our GPU implementation. Figure 2 provides an overview of the two phases and the distinct processes involved in the *L-SEABI* algorithm. All image operations are executed serially, beginning with the operation of the gradient computation and summation for each pixel position in the original image. Following the construction phase of *L-SEABI*, the initial reconstruction outcome is copied to a temporary buffer. Subsequently, the image is refined iteratively and adaptively, based on the error minimization criterion.

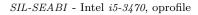

To determine the proposed parallelization strategy on the GPU platform we use *oprofile* [39] to analyze the single-threaded execution of the *SIL-SEABI* 4.9.2 GCC executable. We evaluate our code on an Intel

Fig. 2: L-SEABI algorithm: distinct processes.

Core i5-3470 CPU for 100 repetitions on at least 50 successive frames of each dataset sequence and average the results over all image sizes. As is plotted in Fig. 3, approximately 42% of the total execution time is on average consumed on the address clamping (clamp x, y)function which restricts pixel coordinates according to the image boundaries, while clamping the luminance values to the range of [0, 255] requires 3% of the total upsampling time (Y-clamp). The non-separable,  $5 \times 5$ back-projection filter (bp-flt) is accountable for 20% of the total computation time, i.e. almost the same as the construction phase and the CxHD upsampling combined (12.04% and 4.27% respectively). Separable convolution on the other hand takes up 12% of CPU time (*blr*ft). Adding the error back to the HR image consumes approximately 1.36% of the total time (adderror in Fig. 3), creating a copy of the constructed HR buffer for the algorithm's refinement phase (copybuffer) accounts for approximately 1.25% CPU time and the remaining processes sum up to 4%. Based on the obtained profiling results, we will first describe our generic L-SEABI GPU technique, then document the improvements towards the proposed SIL-SEABI implementation and finally evaluate the performance achieved.

#### 4.2 GPU Implementation and Optimizations

The CUDA programming model allows for unified employment of massively multithreaded processors for both graphics and general-purpose parallel computing. CUDAcapable devices consist of scalable arrays of Streaming Multiprocessors (SMs) to which the programmer distributes parallel threads through high-level GPU programs called kernels [7]. The CUDA API also defines an assembly-resembling intermediate language, the Parallel Thread Execution virtual machine and instruction set architecture (PTX ISA) [40]. The nVidia compiler translates CUDA code to PTX and the driver converts the PTX into GPU-executable code. For all evaluation purposes, we will test our GPU code on three devices designating successive major compute capability versions: the *GeForce GTX 550 Ti* (Fermi microarchitec-

Fig. 3: Profiling the *SIL-SEABI* algorithm for singlethreaded execution on the CPU.

ture) with compute capability 2.1, the GeForce GTX670 (Kepler microarchitecture) with compute capability 3.0 and the GeForce GTX 960 (Maxwell microarchitecture) with compute capability 5.2. The respective number of CUDA cores are 192, 1344 and 1024. In our evaluation we first provide a coarse-grained profiling analysis for a single iteration of our generic L-SEABI GPU implementation. Using CUDA 7.0 we will compare against the results of Fig. 3 and then we will modify the GPU-accelerated version as required for SIL-SEABI. To implement SIL-SEABI we will focus on improving the overall flow and the specifics of each kernel, using our L-SEABI implementation as the groundwork for additional optimizations. We will focus on creating a GPU implementation which does not rely on specific libraries and provides good performance regardless of the underlying architecture.

As reported in [41] the use of page-locked memory (stored in the Host's physical RAM) allows for an approximate twofold increase in bandwidth compared to pageable memory. Thus, on our Host code we begin by allocating page-locked memory for the LR and HR image buffers using the *cudaHostAlloc* function. Besides, in cases where memory access patterns display a spatial locality - such as is our case throughout the L-SEABI algorithm - the use of texture memory is preferred, as it is also cached. Additionally, boundary addressing is handled automatically and therefore, the increased cost related to the address clamping function of the CPU implementation will be mitigated. As a result of texture memory usage, we copy the page-locked buffers onto the device using the *cudaMemcpy2D* function with which we also handle the required texture memory alignment.

```

Input: LR Image, max_iterations, max_error

Output: HR Image

1: gradientCompute<sub>K</sub>

2:

reduce_{\mathcal{K}1} \implies rdc_{res_1}

3:

lseai<sub>K</sub>

for (int i=0; i<max_iterations; i++)</pre>

cudaMemcpy2D(Device->Device)

4:

5:

\operatorname{convCols}_{\mathcal{K}}

6:

convRows<sub>K</sub>

\operatorname{decimate}_{\mathcal{K}}

7:

\operatorname{errimg}_{\mathcal{K}}

8:

9:

abs_{\mathcal{K}}

10:

reduce_{\mathcal{K}2} \implies rdc_{-}res_{2}

if (rdc_res<sub>2</sub> < max_error)

11:

CxHD_{\mathcal{K}}

12:

convNoSep<sub>K</sub>

13:

adderror_{\mathcal{K}}

else break;

}

```

Fig. 4: *L-SEABI* GPU implementation: pseudocode listing kernels.

For performance reasons, it is recommended practice that the number of threads in each block are a multiple of the fixed warp size of 32 threads (i.e., the number of threads executed in a lockstep). According to Xu et al. [42] splitting the image buffer into 2D tiles of  $32 \times 4$ samples provides better performance results on devices having compute capability of 1.3 or higher. Based on the above result and our experimentation we employ the aforementioned thread partitioning scheme on the GTX 670, GTX 960 GPUs and increase the block size to  $32 \times 8$  threads on the GTX 550Ti by adapting the grid size according to the input image dimensions.

Figure 4 lists the pseudocode of the device processing flow in the proposed *L-SEABI* implementation; the GPU kernels are denoted with the  $\mathcal{K}$  subscript. In the  $gradientCompute_{\mathcal{K}}$  kernel every thread computes the gradient in both dimensions and in the process creates a  $W \times H$  buffer storing the per-pixel sums of squared gradients. Next, to compute the total variation we employ the nVidia designed parallel reduction kernel [43], which features unrolling of operations and summation of multiple values per each thread ( $reduce_{\mathcal{K}}$  in Fig. 4). The  $lseai_{\mathcal{K}}$  kernel involves computation of the initial reconstruction by employing the  $rdc_{-}res_{1}$  result of the  $gradientCompute_{\mathcal{K}}$  and it features a balanced cost between arithmetic and memory transfer operations; each thread fetches 16 surrounding samples per-pixel from texture memory to registers, performs characterization based on the threshold result and computes the luminance outcome for the horizontal, vertical and diagonal positions of the upsampled grid. Note here that, in order to avoid thread divergence when calculating the coordinates in the HR grid, we execute our upsampling kernels by using the LR grid partitioning scheme. Thus, the HR offsets are computed as follows:

$$\begin{split} I_{offset} &= [(ty*2)*(W*2)] + (tx*2) \\ HH_{offset} &= [(ty*2)*(W*2)] + [(tx*2)+1] \\ HV_{offset} &= \{ [(ty*2)+1]*(W*2)\} + (tx*2) \\ HD_{offset} &= \{ (ty*2)+1]*(W*2)\} + [(tx*2)+1] \end{split}$$

(1)

where tx, ty are the translated 2D thread coordinates inside a 1D memory array and W is equal to the LR image width or the pitch size in bytes, in case of a non-texture or texture-bound output HR buffer respectively. Furthermore, this approach effectively increases the instruction level parallelism (ILP) to 4 because each thread computes and stores four pixel values in the upsampled grid.

The iterative refinement phase (lines 4–13) begins its first/subsequent iterations by copying the reconstructed/refined image to an intermediate, texture-bound buffer. This copy takes place inside the device and precedes the two separable filtering kernels ( $convCols_{\mathcal{K}}$ ,  $convRows_{\mathcal{K}}$ ), which also rely on texture memory and register storage: each thread fetches 5 pixels per input sample from the HR buffer into device registers, computes the convolution sum and copies the result from registers back into global memory. We note here that all the filtering operations in our kernels are based on unrolled operations.

The image is then subsampled by  $decimate_{\mathcal{K}}$ , which employs the LR thread partitioning scheme and it simply copies data from the samples in the HR buffer with coordinates (tx \* 2, ty \* 2), to the samples in the LR buffer with coordinates (tx, ty). The  $CxHD_{\mathcal{K}}$  and the  $convNoSep_{\mathcal{K}}$  follow similar design choices to the L-SEAI kernel, i.e., they rely on texture fetches for input and perthread registers to store intermediate results; threads of the  $CxHD_{\mathcal{K}}$  read 12 pixels per input sample, while  $convNoSep_{\mathcal{K}}$  threads read 25 pixels per input sample. The remaining kernels are functionally straightforward:  $errimg_{\mathcal{K}}$  subtracts the decimated image from the LR input and then its result is conditionally forwarded to  $CxHD_{\mathcal{K}}$  based on the current norm  $l_1$  value  $(rdc_res_2,$ i.e., the outcome of  $abs_{\mathcal{K}}$  and  $reduce_{\mathcal{K}})$ .

Figure 5 displays the execution analysis of the proposed L-SEABI implementation using nVidia's profiler on the devices tested averaged over all image resolutions. Bars outlined in black describe the corresponding cost on the GTX 670 and bars outlined in blue refer to the cost as measured on the GTX 550 Ti. As mentioned earlier, due to the use of texture-bound buffers, address clamping is handled with minimal overhead and therefore, the profiler does not report a discrete cost.

L-SEABI Single-iteration: GTX 670 and GTX 550Ti

Fig. 5: L-SEABI: Single-iteration GPU Analysis.

Luminance clamping on the other hand requires an explicitly designed device function. The compiler fuses our luminance clamping code with the kernels it is employed in, namely  $lseai_{\mathcal{K}}$  and  $adderror_{\mathcal{K}}$  and thus its computational cost is included in the corresponding cost reported in Fig. 5 for the *L-SEAI* and *adderror* processes. Note here that the L-SEAI process incorporates lines 1-3 of Fig. 4 and additionally a single-value D2H copy, which accounts for 0.24% of the total time. In the case of the GPU implementation more than 30% of the computation time is consumed on filtering operations, namely the  $convNoSep_{\mathcal{K}}$  displayed as bp-flt (back-projection filter) and  $convCols_{\mathcal{K}}$ ,  $convRows_{\mathcal{K}}$  shown as *blr-flt* (blur filter) in Fig. 5. There is also a noticeable discrepancy between the same filtering kernels on the two devices tested. Since the  $convNoSep_{\mathcal{K}}$  requires 25 pixel reads per input sample, its performance is texture memory bandwidth bound and the kernel reaches the limit of 232.7 GB/son the GTX 550 Ti (680.7 GB/s on the GTX 960). The utilization is more balanced in the cases of separable convolution kernels; in the case of  $convRows_{\mathcal{K}}$  the performance is compute-bound because all the texture fetches refer to sequential addresses while the  $convCols_{\mathcal{K}}$ displays a memory-bound performance. The memory transactions that do not belong to the kernels have a significant cost, i.e., they account for approximately 26% of the total computation time. Specifically, the H2D and D2H transfers - related to transferring the LR image to and the HR result from the device - are obligatory and apart from the already adopted page-locked memory approach there cannot be further improved. There is also a negligible amount of time related to two singlevalue D2H transactions of the integer  $reduce_{\mathcal{K}}$  results. Intra-device transfers though (denoted as D2D in Fig.

5) can be minimized as they pertain to copying data to texture-bound memory.

The following subsection will describe and classify the performed optimizations based on their scope, as *algorithmic-level* and *platform-dependent*. Moreover, it will evaluate these ameliorations by comparing the relative performance gains against the proposed baseline *L-SEABI* implementation. All modified kernels will be denoted by prepending "m" on their symbolic names.

# 4.2.1 Algorithmic-level optimizations.

Optimizations at the algorithm's level are achievable because the proposed technique's goal is the single iteration execution of *L*-SEABI assuming a priori that the adaptive back-projection of the error image occurs in all cases. Thus, in the proposed SIL-SEABI implementation we can omit the execution of the  $abs_{\mathcal{K}}$  in line 9 of Fig. 4, and the second reduction kernel in line 10 both of which account on average for 3.75% of the total execution time  $(l_1 \text{ norm in Fig. 5})$  on the devices tested. Additionally, the  $CxHD_{\mathcal{K}}$  kernel is modified to limit the neighboring checks from 8 pixels to only the 4 pixels surrounding each diagonal sample. This results in the modified  $mCxHD_{\mathcal{K}}$  kernel, which applies the same averaging filter: the improvement is that it requires 2 less registers per thread, and 12 less diagonal edgecharacterization comparison operations up from 14 in the original *CxHD* algorithm.

To optimize the separable convolution operations, we first exploit the fact that our  $5 \times 5$  separable Gaussian kernel features symmetric coefficients. Therefore, we can reduce the number of multiplication operations to three per input sample by rewriting the convolution sum as  $p^{out} = h_0 * p_0^{in} + h_1 * p_1^{in} + h_2 * p_2^{in} + h_3 * p_3^{in} + h_4 * p_4^{in} =$  $h_0 (p_0^{in} + p_4^{in}) + h_1 (p_1^{in} + p_3^{in}) + h_2 (p_2^{in}), \text{ where } p^{out} \text{ denotes the}$ luminance of the output sample,  $h_n$  and  $p_n^{in}$ ,  $n \in [0, 4]$ the filter coefficients and the input luminance values respectively. Notice also that in Fig. 4 the  $convRows_{\mathcal{K}}$ kernel is always followed by  $decimate_{\mathcal{K}}$ . The fusion of these two operations into the single  $convRowsdec_{\mathcal{K}}$  kernel provides the following two benefits: a) it circumvents the overhead of creating and executing a separate decimation kernel; and b) it leads to the reduction of the number of computations and read operations related to  $convRows_{\mathcal{K}}$  since due to the immediate decimation process only the even numbered samples are essentially needed. To avoid thread divergence we follow a similar approach to Eq. 1: we employ the LR thread partitioning scheme and fetch the even samples from the texture-bound buffer as follows:

$$p_n^{in} = tex2D(texref, tx*2 + n - 2, ty*2), n \in [0, 4]$$

(2)

Table 3: Separable convolution PTX ISA instruction type, amount ran and associated throughput per arithmetic/device.

| blr-flt Arith. Instr. Type               | Run | ops/c                | ycle/MP                |

|------------------------------------------|-----|----------------------|------------------------|

| int $\blacksquare$ float                 | -   | 550 Ti               | 670                    |

| and.b32 $\blacksquare$ and.b16           | 5   | 48 🔳 48              | 160 🔳 160              |

| $add.s32 \blacksquare add.ftz.f32$       | 2   | $48 \blacksquare 48$ | $160 \blacksquare 192$ |

| mul.lo.s32 $\blacksquare$ mul.ftz.f32    | 1   | $16 \blacksquare 48$ | 32 🔳 192               |

| mad.lo.s32 $\blacksquare$ fma.rn.ftz.f32 | 2   | $16 \blacksquare 48$ | 32 🔳 192               |

| shr.u32                                  | 1   | 16 🔳 16              | 32 🔳 32                |

| - ■ cvt.u16.u32                          | 5   | - 🔳 16               | - 🔳 32                 |

| - ■ cvt.rn.f32.u16                       | 5   | - 🔳 16               | - 🔳 128                |

where tex2D is the two-dimensional texture lookup CUDA function and texref is the texture-bound device array containing the column-filtered HR construction.

# 4.2.2 Platform-Dependent and Lower Level Optimizations.

More specialized optimizations can be applied through the use of specific CUDA API code modifications by studying the proposed implementation both at a high (CUDA C code) and at a low level (PTX ISA code). The GPU execution analysis in this work (Fig. 5) showed that most of the processing time is consumed on the non-separable  $5 \times 5$  filtering operation during the L-SEABI refinement phase. Since the overall performance is bounded by the memory bandwidth,  $convNoSep_{\mathcal{K}}$ can be improved by using shared memory architecture. We employ the scheme that Eklund et al. proposed in [44] since this scheme is compatible with all of our devices: i.e., blocks of  $32 \times 32$  threads transfer an image window of  $96 \times 64$  samples to the shared memory prior to performing unrolled 2D convolution. Note that the GTX 960 has 33% larger shared memory size, a fact which allows increasing the window to  $128 \times 64$  samples.

The detailed execution analysis of the proposed separable kernels revealed that their performance is computebound. As documented in [45], increasing the instruction level parallelism (ILP) in CUDA can improve the performance even with fewer threads. In our case, we modify the  $convRows_{\mathcal{K}}$  and  $convCols_{\mathcal{K}}$ , so that each thread fetches four 5-pixel sets from four consecutive blocks, performs four convolution sums and stores four results. This increases the number of required registers per thread from 12 to 28 on the GTX 550Ti, from 14 to 31 on the GTX 670 and from 13 to 31 on the GTX960. On the Fermi-based device the modified kernels then reach the texture memory bandwidth limit; to further improve the performance we turn our attention to the use of shared memory by modifying the nVidia separable convolution code sample [46]. Reworking the

kernels for ILP=4 causes the texture memory bandwidth to exceed 800GB/s on the *GTX 670* without hindering performance while the Maxwell-based device can reach 534GB/s. In [6], the operations of *L-SEABI* were designed to rely on integer arithmetic excluding the separable filtering process. In particular, to enhance the output quality convolution is applied by using the  $\langle h_0, h_1, h_2 \rangle = \langle 0.00257, 0.165795, 0.664904 \rangle$  filter and converted the result back to integer.

Conveniently, the modern GPUs incorporate native floating-point units that provide higher multiplication performance than the use of integer operations; the respective throughput of 32-bit floating-point multiplyadd operations (ops) per clock cycle (cc) and multiprocessor (MP) is 48, 192 and 128 on the GTX 550Ti, the GTX 670 and the GTX 960 respectively. Note that we have to explicitly cast all coefficients and variables as floating-point in the convolution code, otherwise the compiler will assume 64-bit precision, which has quite lesser throughput (4, 8 and 1 ops/cc/MP)respectively). To comply with the integer storage/operations of the proposed implementation though, additional type conversions are required. The review of the PTX ISA generated code reveals that apart from the computation instructions, the floating-point convolution requires 5 conversions from 32-bit to 16-bit unsigned numbers, 5 conversions from 16-bit to 32-bit floating-point and 1 conversion from floating-point to 32-bit unsigned. The generated instructions considering the integer and the floating-point separable convolution implementation are shown in Table 3 juxtaposed by their respective throughput. On the Fermi and Kepler devices the throughput of 32-bit integer multiply-add operations/cc/MP is 16 and 32 respectively [47]. To compare against the floating-point filtering process we compute integer Gaussian coefficients by multiplying the original coefficients with  $2^{23}$ , resulting in the filter  $\langle h_0, h_1, h_2 \rangle = \langle 21559, 1390789, 5577619 \rangle$ . Note that the division operation is converted to an arithmetic shift by the compiler (shr.u32). Also, Table 3 shows that while the floating-point multiplication throughput is considerably higher compared to integer operations, the amount of conversions is non-trivial and therefore, the impact on the computation time requires evaluation. The  $GTX \ 960$  has in some cases lower throughput than the compute-capability 3.0 GTX 670 - this is mitigated by the Maxwell-based device's reduced instruction latency and stall cycles.

In this work, the upsampling optimizations mainly target the  $lseai_{\mathcal{K}}$  and  $CxHD_{\mathcal{K}}$  and they are based on lower level PTX ISA observations. Notice that the original *L-SEABI* algorithm requires a square root to compute the edge characterization threshold [6]. On CUDA, the floating point square root is computed as a reciprocal square root followed by a reciprocal. In PTX ISA this is translated as the sqrt.approx.ftz.f32 instruction. Due to the integer nature of *L-SEABI* and the threshold being  $T = \sqrt{\frac{\mathcal{T}\mathcal{V}^{LR}}{WH}}$  where  $\mathcal{T}\mathcal{V}^{LR} = \text{rdc\_res}_1$  (Fig. 4) we consider two alternatives: a) set  $T = \frac{T \mathcal{V}^{LR}}{WH}$  and then compute the square of the luminance differences in order to characterize edges, b) compute the reciprocal square root of  $\frac{WH}{T \mathcal{V}^{LR}}$ . Besides these two options, the following subsection will evaluate the performance of a lower precision threshold computation, which employs integer division. Finally, based on the generated PTX ISA code we rewrite all comparisons as Boolean statements and fine-tune all comparison operations in  $mlseai_{\mathcal{K}}$  and  $mCxHD_{\mathcal{K}}$  to eliminate nested *if* statements by applying branch fusion. As an example, Fig. 6 shows how we convert the computation of HH output samples  $p_{HH}^{out}$  in the  $mCxHD_{\mathcal{K}}$ kernel (lines 5-10) to a divergent-free optimized version (line 13). Notice that in this case we have to explicitly define two additional Boolean conditions (lines 11-12) to procure the same result. Through this optimization we seemingly convert the branch statement to a sum of integer products; actually though, only one of the products contributes to the  $p_{HH}^{out}$  value for any given sample. Moreover, since every left operand of these multiplication operations evaluates to either 0 or 1 we can improve the performance by converting each Boolean multiplication to two bitwise and one integer addition operations as follows: cnd \* flt = [!(cnd) + 1] & flt, where  $cnd \in \{0, 1\}$  is the Boolean condition, flt is the integer result of the filter, where ! is the bitwise NOTand & is the bitwise AND operator. Both of these operations have significantly higher throughput compared to the integer multiplication, especially on more recent devices [47].

Regarding the remaining kernels, the proposed optimizations target the computation of the absolute difference values in the  $mgradientCompute_{\mathcal{K}}$ ,  $mlseai_{\mathcal{K}}$  and  $mCxHD_{\mathcal{K}}$  kernels. To that end, for the computation of the absolute difference |dif| between pixel values  $p_0^{in}$  and  $p_1^{in}$ , we utilize the *usad* integer intrinsic of CUDA as:  $|dif| = |p_0^{in} - p_1^{in}| = usad(p_0^{in}, p_1^{in}, 0)$ . We also compare the performance of \_usad against four distinct implementations of the absolute function: i) the *fabsf* function, ii) the \_vabsdiffu4 intrinsic, which computes per-byte unsigned absolute difference in an SIMD fashion; iii) an inline implementation using the ternary operator (denoted as  $ABS_t$  and iv) an inline implementation using shift operations  $(ABS_s = [dif + \{dif \gg 31\}] \land \{dif \gg 31\},\$ where ">>" and " $\wedge$ " denote right shift and XOR operations respectively). Finally, we focus on reducing the

$mCxHD_{\mathcal{K}}$  HH Computation: **Initial Boolean Conditions:** // condition #1, vertical edge 1: A > 02: A < 0' condition #2, horizontal edge // condition #3, NE direction 3: B > 0// condition #4, SW direction 4: B < 0Computation using nested if statements: 5: **if** A > 0: **if** B > 0:  $p_{HH}^{out} \leftarrow \text{bicubic filtering } \#1$ 6: else if B < 0:  $p_{HH}^{out} \leftarrow$  bicubic filtering #2 7:  $p_{HH}^{out} \gets \text{bilinear filtering}$ 8: else: 9: else if A < 0:  $p_{HH}^{out} \leftarrow \text{bicubic filtering } \#3$  $p_{HH}^{out} \leftarrow \text{bilinear filtering}$ 10: **else**: **Additional Boolean Conditions:** 11: A = 0// condition #5, homogeneity 12: B = 0// condition #6, strictly vertical **Divergent-free computation:** 13:  $p_{HH}^{out} \leftarrow$ (cnd#1 && cnd#3) \* (bicubic #1) +(cnd#1 && cnd#4) \* (bicubic #2) +(cnd#2) \* (bicubic #3) +(cnd#6 | (cnd#1 && cnd#5)) \* (bilinear)

Fig. 6: HH pixel code in  $mCxHD_{\mathcal{K}}$ : divergent-free computation.

amount of D2D transfers by directly writing to texturebound memory or by employing shared memory instead.

# 4.2.3 Performance Evaluation

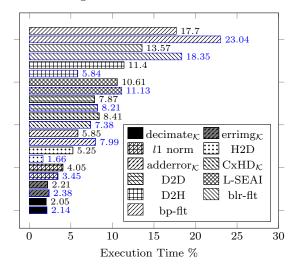

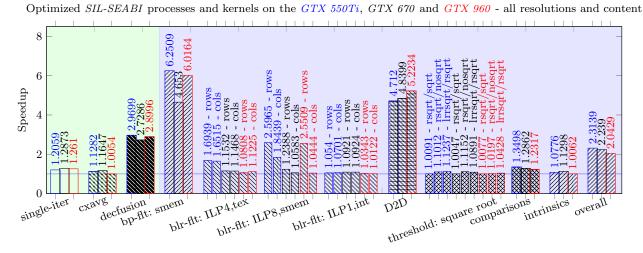

This section will first evaluate the relative performance, i.e., the induced speedup of the proposed optimizations against the baseline *L-SEABI* implementation. Second, it will assess the computation time required to upsample each LR input. To evaluate the performance of the proposed optimizations regarding *SIL-SEABI* we perform the tests on the *GTX 550 Ti*, representing mid-range performance and on the *GTX 670*, *GTX 960* VGAs representing the high-end.

Figure 7 shows the achieved speedup per device and kernel depending on the type of the optimization. Algorithmic-level and Platform-dependent optimizations are highlighted in the green and blue areas respectively. Regarding algorithmic-level optimizations, we observe an overall execution speedup of up to 1.29x by omitting the  $abs_{\mathcal{K}}$  and the second reduction kernel (single-iter in Fig. 7). When we limit the number of comparisons during adaptive back-projection we notice a speed improvement in  $CxHD_{\mathcal{K}}$  by up to 1.16x (cxavg in Fig. 7). Fusing decimation with separable row convolution by the proposed divergent-free solution (Eq. 2, decfusion in Fig. 7) produces a more pronounced speedup:  $convRows_{\mathcal{K}}$ is accelerated by over 2.7x. Note though that rewriting the convolution computation to exploit the Gaussian kernel symmetry does not provide additional speedup

Fig. 7: Optimized GPU Analysis for SIL-SEABI speedup per kernel involved vs the baseline implementation, averaged over all resolutions and image content.

as the compiler automatically generates identical PTX ISA code in both cases.

*Platform-dependent* optimizations provide the highest speedup as the remaining bar graphs show. Specifically, the use of shared memory in  $mconvNoSep_{\mathcal{K}}$  (shown as BP-flt: smem in Fig. 7) is critical, increasing the performance of the original kernel by 4.65x on the GTX670 and more than 6x on the GTX 550Ti and GTX 960, which have less texture memory bandwidth. Note here that taking advantage of the increased shared memory of the GTX 960, i.e. modifying the method by Eklund et al. [44] to effectively process a  $124 \times 60$  area and thereby increasing ILP to 8 compared to 6 slightly increases occupancy by 1.5%; though it does not produce a significant performance advantage as a result of the small  $5 \times 5$ filter size. When considering texture-based separable convolution, increasing the ILP to 4 for each thread in the  $convCols_{\mathcal{K}}$  and  $convRows_{\mathcal{K}}$  kernels results in over 1.6x speedup on the GTX 550Ti and 1.15x on the GTX670 (blr-flt: ILP4.tex in Fig. 7). The texture-based implementation can be further enhanced by employing shared memory combined with doubling the ILP (*blr-flt*: ILP8, smem in Fig. 7, [46]). Due to the small radius of our Gaussian convolution filter, the high register bandwidth of the GPUs and the spatial locality of the convolution process, the acceleration achieved is more prominent when modifying  $convRows_{\mathcal{K}}$  to use shared memory (speedup of approximately 2.6x). This level of parallelism is the maximum that can be achieved for these kernels on the devices tested, as increasing the ILP to a greater extent results in arithmetic latency due to decreased warp occupancy. Evaluating the use of integer operations on the SIL-SEABI filtering process confirms the observations of Table 3: the absence of additional

conversion instructions required for floating-point filtering slightly favour our integer implementation by 1.05x on average. The speedup related to Device to Device (D2D) memory transfers emphasizes the importance of memory latency in GPUs; using a single D2D memory transfer (i.e., by directly writing to texture-bound memory or using shared memory instead) reduces the time spent on D2D transfers by approximately 5x compared to our original GPU implementation.

Next, we evaluate the proposed optimizations pertinent to the  $lseai_{\mathcal{K}}$  and  $CxHD_{\mathcal{K}}$  kernels. Omitting a reciprocal computation provides a negligible advantage compared to the GPU floating-point square root implementation (rsqrt/sqrt in Fig. 7), which is justified as there is only a single threshold computation involved in the whole  $lseai_{\mathcal{K}}$  kernel. Notice that avoiding the square root altogether substitutes a single reciprocal square root with 6 integer multiplication instructions required for comparison reasons and thus decreases the instruction throughput on GPUs (*rsqrt/nosqrt* in Fig. 7). Hence, the reciprocal square root provides the highest performance when computing threshold T in  $lseai_{\mathcal{K}}$ . We can also exchange accuracy for a marginal performance increase by using integer arithmetic on the  $\frac{WH}{TV^{LR}}$ division as *lrrsqrt/rsqrt* in Fig. 7 suggests. Branching optimizations in difference comparisons are used throughout  $lseai_{\mathcal{K}}$  and  $CxHD_{\mathcal{K}}$  (averaged as "comparisons" in Fig. 7); particularly these depicted in Fig. 6, display speedup of up to 1.35x on average for the aforementioned kernels. Performance increase is more prominent on the  $CxHD_{\mathcal{K}}$  kernel compared to  $lseai_{\mathcal{K}}$  (1.48x vs 1.15x on average) because the compiler derives predicated instructions for the latter due to the absence of multiple/nested conditions in the original algorithm [6].

Also, the perceived gains are more pronounced on the lower compute capability GTX 550Ti GPU, as the GTX670 and GTX 960 can schedule four warps and two independent instructions per warp per cycle (|48|). To conclude our relative performance evaluation, we assess the five different implementations of the absolute difference as mentioned in Section 4.2.2. According to our evaluation regarding  $lseai_{\mathcal{K}}$  and  $CxHD_{\mathcal{K}}$  (averaged as "intrinsics" in Fig. 7), the *usad* solution accomplishes the highest performance. The speedup we measured is consistent between devices and kernels, i.e., 1.0617x compared to the *fabsf* function, 1.1416x compared to the ternary operator  $(ABS_t)$ , 1.0719x compared to the integer shifts implementation  $(ABS_s)$  and 1.1591x compared to the \_vabsdiffu4 intrinsic (supported on the Kepler and Maxwell devices). Notice that even though the latter SIMD operation has an instruction throughput of 160 ops/cc/MP on the *GTX 670*, when considering  $lseai_{\mathcal{K}}$  the *usad* solution translates to only 4 sad. u32 instructions. These 4 sad.u32 instructions have the same throughput as 4 shl.b32 instructions required to employ the SIMD intrinsic. Studying the PTX ISA code though, reveals that the  $_vabsdiffu4$  implementation requires 8 additional and. b32, 2 additional shl. b32 and 6 additional or.b32 instructions which rationalize the performance penalty.

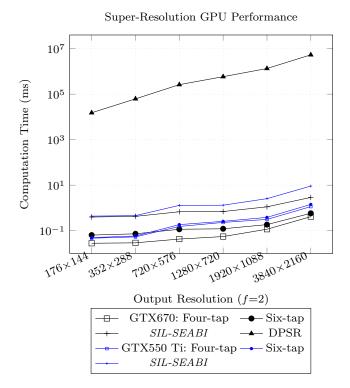

Finally, to evaluate the absolute performance of the proposed SIL-SEABI implementation we set apart H2D D2H transfers, thus measuring the computation time consumed only by the upsampling kernels. To that end, we compare against our own implementations of separable 4-tap and 6-tap integer kernel interpolation, both of which represent two of the simplest upsampling solutions. We also compare against the GPU implementation of DPSR, representing the state-of-the-art. Evaluation results are plotted in Fig. 8 where computation time required to upsample each image by 2 in both dimensions is displayed as the average for every image resolution in the experimental dataset (Sec. 3). We note here that although the GTX~670 has approximately 24% more cores compared to the GTX 960 it achieves similar performance, i.e., less than 10% discrepancy and it is 14.77%faster when executing the *SIL-SEABI*. This is mainly attributed to the benefits of the internal design of the Maxwell architecture: each Streaming Multiprocessor has a power of two number of cores, functional units have a dedicated scheduler, there are 8 Load/Store units per 32 cores (compared to 16 per 96 cores for Kepler) and finally, more registers per core.

As expected, the simple interpolation kernels prove to be the fastest option; upsampling to  $3840 \times 2160$  from  $1920 \times 1080$  by employing Bicubic interpolation requires up to 0.4ms on the *GTX* 670 and up to 1.14ms on the

Fig. 8: SIL-SEABI on GPU: Execution Time (f = 2).

GTX 550 Ti. The 6-tap filter is 1.4x slower on average, a result which is consistent with the filtering kernel ratio. Thus, when considering  $1920 \times 1080$  input, our simple interpolation kernels attain a performance of 698 frames per second (fps) on the mid-range GPU and up to 1718 fps on the high-end device. Also, it is anticipated that these methods perform approximately an order of magnitude faster than SIL-SEABI (5.1x and 7.6x considering 6-tap and 4-tap interpolation respectively). Still, our SIL-SEABI implementation remains suitable for real-time 1080p processing as it achieves 109 fps on the GTX 550 Ti and 345 fps on the GTX670. Contrastingly, Super-Resolution using Deformable Patches [9], consumes four orders of magnitude more time when upsampling to  $176 \times 144$  and up to six orders of magnitude in the case of 2160p output. The memory footprint of SIL-SEABI is also relatively small and comparable to the 46MB of the simple methods because it requires only 151MB of device memory; hence, it can be executed on all modern discrete GPUs. DPSR execution on the other hand is significantly restricting because it consumes at least 466MB ( $176 \times 144$ ) and up to 1452MB of device memory for larger inputs.

# 5 Acceleration of L-SEABI on FPGA

The proposed hardware acceleration involves the parallel architectural design, the parametric VHDL development, and the deployment of L-SEABI on a variety of FPGA devices. The purpose of implementing L-SEABI in a parametric fashion on various FPGA devices is to assess its performance and power dissipation with multiple parallelization factors and FPGA technologies. The following subsection describes the proposed architecture and the parallelization techniques devised to accelerate L-SEABI, whereas the second subsection presents our design exploration and the implementation results.

#### 5.1 Parallel architecture design of SIL-SEABI

The super-resolution algorithm in [6], besides improved quality, targets parallelization amenability and low-cost implementation on hardware, especially on reconfigurable platforms with limited memory resources, such as the FPGA. Hence, compared to similar and more sophisticated super-resolution algorithms, *SIL-SEABI* avoids highly-involved mathematical/statistical solutions, abundant dependencies among the calculations, or increased storage of side information (e.g., dictionaries). Instead, *SIL-SEABI* promotes locality and regularity.

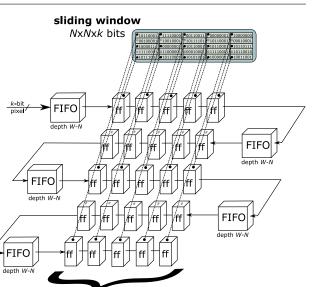

The proposed architectural design relies on extensive pipelining of the computation, both on pixel basis and on task level. It is based on a technique involving the continuous processing of the image in a pixel-by-pixel basis by using a long pipeline, which lines up all arithmetic operations required to complete a given task of the algorithm for a single pixel. Note that the term task refers here to any elementary, conceptually distinct, transformation of the image, such as blurring, decimation, 2D convolution with a fixed kernel, calculation of image derivatives, etc. Generally, the hardware cost of a pixel-based pipeline reduces to the cost of a single-pixel processing engine and it is independent of the image size. In specific cases, the pipeline must cache internally a group of pixels (to operate on a local area of the image, e.g., compute derivatives) the number of which could be proportional to the width of the image (e.g., when reading the pixels in raster-scan order). In the case of a pipeline designed optimally to achieve 100% utilization, the throughput of the pixel-based pipeline increases to one pixel per cycle and allows the entire task to complete in  $W \times H + L$  cycles, where W is the image width, H is the image height, and L is the latency of the pipeline. In other words, we design the pipeline so that it will complete one algorithmic task/iteration in a single burst read of the image. To achieve the aforementioned throughput, we parallelize the calculations required for each pixel, both in terms of arithmetic operations within a formula evaluation, as well as in terms of partial products within a task. That is, considering the

NxN flip-flop array

Fig. 9: Proposed architecture of a serial-to-parallel buffer for 2D raster-scanning of the image with a NxN sliding window

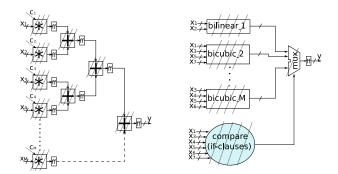

latter, we compute in parallel the vertical and horizontal derivatives of the pixel, we compute in parallel the multiple FIRs considered by our adaptive upsampling mechanisms, we compute in parallel the two 1D convolutions of a separable kernel by using its 2D equivalent kernel, etc. The key idea in our parallelization approach is to operate concurrently on a local area of the image and complete a pixel transformation, virtually, in a single cycle. To facilitate such concurrency, we design and integrate in our pipeline a serial-to-parallel buffer, which inputs one sample per cycle (equal to the input rate of the pipeline) and outputs  $N \times N$  samples per cycle. Figure 9 depicts the architecture of the proposed buffer interconnecting in series N FIFO memories with  $N \times N$  registers. We set the depth of each FIFO to W - N and we feed the buffer with pixels/samples in raster-scan order. As a result, the  $N \times N$  output of the buffer will scan the image in a raster-scan order providing one distinct  $N \times N$  window per cycle. The proposed design uses the minimum amount of connections (1 input and 1 output per component, excluding the unavoidable output ports of the buffer) and the minimum amount of flip-flops (equal to the number of parallel output ports). Subsequently, in a single cycle, the  $N \times N$  samples are forwarded to the processing part of the pipeline, where we perform parallel calculations by using multiple arithmetic units interconnected according to the implemented arithmetic formula. Figure 10, on the left, depicts a processing part performing generic convolution; we use  $M = N \times N$  independent

Fig. 10: Architecture of two fine-grain pipelined processing parts which follow a serial-to-parallel buffer to perform 2D convolution (left) or adaptive FIR upsampling (right)

constant multipliers, each developed as a fine-grained pipeline with 2-4 stages depending on the width of the  $x_i$  inputs, and a fine-grain pipelined adder tree of height  $\log M$ . This configurable engine can implement blurring, Laplacian, Derivatives of Gaussian, etc. Figure 10, on the right, depicts another processing part performing adaptive upsampling. We use multiple FIRs working in parallel to perform bilinear and bicubic filtering in a fine-grain pipelined fashion. Finally, we select the highest quality output via a multiplexer controlled by the if-clauses detecting the dominant local orientation/edge (according to the rules of the construction phase of L-SEABI, or the CxScale technique). Altogether, a long pipeline consisting of the buffer and its processing part; it will input one datum per cycle and it will output one result per cycle in a continuous flow (with very small gaps at regular time intervals corresponding to the wrap-around step of our 2D scanner at the end of each image row). A substantial fraction of the latency is equal to the time required to initially fill the FIFOs of the buffer and is negligible when compared to the total execution time (e.g., 0.4% when blurring a  $1920 \times 1080$ image with a 5x5 kernel).

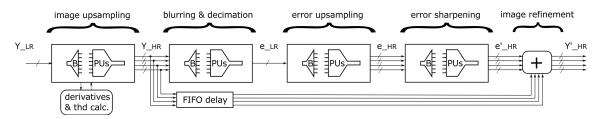

On top of pixel-based pipelining, we apply pipelining at task level by connecting in series the five distinct engines developed for the five tasks of *SIL-SEABI*. Figure 11 depicts the entire architecture designed in a "continuous flow transformation" approach. That is, every sample/pixel is forwarded directly to the next stage for further processing to complete the entire SIL-SEABI in a single pass of the long pipeline, without any intermediate caching/delays. The architecture features 100% utilization and, at any time instant, it processes concurrently hundreds of samples throughout its length (within the fine-grain pipelined PUs of the five engines). At the first stage (figure 11), we perform an initial upsampling of the image according to *L-SEABI*'s con-

struction phase; we employ a serial-to-parallel buffer (B) to forward 4x4 low-resolution pixels per cycle to two processing parts, i.e., to the parallel FIRs doing adaptive upsampling (PUs) and to a smaller pipe accumulating image derivatives and adjusting *L-SEABI*'s threshold according to the total variation of the image (we use the total variation of an image stripe to predict the total variation of the next stripe, on-the-fly). The threshold is returned to the main engine, which outputs a local region of 2x2 high-resolution pixels per cycle. The purpose of increasing the pipeline paths to 4 is to avoid multiple clock domains (we now operate in 1/4 clock frequency with enough slack for our critical paths) and also to exploit the parallelization capabilities of HW design. The four remaining stages perform SIL-SEABI's refinement phase. More specifically, at stage 2, we perform low-pass filtering and decimation of the HR image to output one LR pixel per cycle. Notice that the quadruplet input to stage 2 is given to a serial-to-parallel buffer sliding quadrupled words and providing a 3x3 quadruplet output, which contains the 5x5 pixel region to be blurred; due to this technique, our window slides by two pixels per cycle facilitating the decimation of the image by 2 without decreasing the engine's output rate in half (we achieve 100% utilization). The error of the reconstructed pixel is forwarded to stage 3, which performs adaptive upsampling similarly to stage 1, however, according to the CxScale rules. The HR results are forwarded to stage 4 in a 2x2 format via 4 parallel paths. Stage 4 employs a serial-to-buffer providing 3x3 quadruplets per cycle, i.e., a local region of 6x6 samples, which itself contains four regions of 5x5 samples. In parallel, the four regions are multiplied with a 5x5 Laplacian kernel, each, such that the engine will output 4 HR sharpened samples per cycle. At the final stage, we add the 4 HR samples to the 4 HR pixels delayed after stage 1 to refine the HR image and complete the SIL-SEABI algorithm. Notice that, depending on the application, the 2x2 pixel output of the architecture can be easily transformed to a single raster scan port (with 4x faster clock rate) by employing a RAM buffer to temporarily store two HR image rows. Also notice that the above described architecture can be easily modified to support more iterations of L-SEABI; we can employ an external memory to store the entire image  ${}^{i}Y_{HR}$  output from the pipeline after each iteration *i*, such that we can bypass stage 1 and feed  ${}^{i}Y_{HR}$  back to the pipeline, together with  $Y_{LR}$ .

#### 5.2 Design exploration and implementation results

The proposed architecture was developed in parametric VHDL to allow the straightforward deployment of L-SEABI on various diverse FPGA devices and adaptation

Fig. 11: Architecture of an L-SEABI super-resolution engine with 5 fine-grained pipelines including serial-to-parallel buffers (B) and processing parts with parallel units (PUs). The rate varies from 1 to 4 samples/cycle depending on spatial resolution.

to distinct application requirements. The parameters include the datapath widths, image size, kernel sizes, and moreover, the parallelization factor P of L-SEABI on image level. Parallelization on image level is yet another capability of HW design, besides those described in the previous subsection, which refers to the number of images or image stripes being processed concurrently. That is, we deploy P individual *L-SEABI* pipelines on the FPGA and we feed them with distinct horizontal stripes of the image. Each stripe has height H/P + Opixel rows, where H is the input image height and O is the number of rows used to overlap successive stripes (in order to make the parallel algorithm functionally equivalent to the original execution, we must extend the borders of each stripe to slide the convolution kernels seamlessly between stripes). In the current paper we assume 8-bit pixels, input image resolution 1920x1080, overlapping O = 9 due to the size of *L-SEABI*'s kernels, and also, we abstract away the I/O functions of the FPGA to focus on the cost of the actual algorithm in terms of resource utilization (we assume that I/O is handled externally, depending on the application). We show how multiple pipelines can fit in various FPGA devices (with some slack in the utilization, e.g., 100 RAMBs, for other hypothetical components of the application, e.g., the I/O controller). For this purpose, we implement the architecture on 10 FPGA devices representing four technology generations (Xilinx Virtex 5, Virtex 6, Artix and Virtex 7, as well as Ultrascale) and we explore the performance of *L*-SEABI by varying the parallelization factor P from 1 to 29 depending on the size of the underlying FPGA device.

Implementation results are summarized in Table 4, which includes the number of LUTs and RAMB18s as a metric for evaluating the FPGA resources, as well as the total execution time and power required to upsample a 1920x1080 image to 3840x2160 pixels with the maximum achievable clock frequency. In the upper part of Table 4, we report absolute numbers for a single *L-SEABI* pipeline implemented on low-range low-price devices representing 4 FPGA families/generations (Virtex 5,

Table 4: FPGA resources vs. execution time (a 1920x1080 image is input to various devices with various parallelization factors P and f = 2.)

| device     | P  | LUT  | RAMB18 | power            | time                |

|------------|----|------|--------|------------------|---------------------|

| xc5vlx30t  | 1  | 3753 | 64     | $0.9 \mathrm{W}$ | $8.3 \mathrm{ms}$   |

| xc6vlx75t  | 1  | 3493 | 64     | $2.3 \mathrm{W}$ | $6.8 \mathrm{ms}$   |

| xc7a100t   | 1  | 3501 | 64     | $0.5 \mathrm{W}$ | 8.2  ms             |

| xcku035    | 1  | 3637 | 64     | $1 \mathrm{W}$   | $5 \mathrm{ms}$     |

| xc5vlx110t | 4  | 22%  | 89%    | 3 W              | $2.7 \mathrm{ms}$   |

| xc5vlx330t | 8  | 15%  | 79%    | $7.5 \mathrm{W}$ | 1.5  ms             |

| xc6vlx75t  | 3  | 22%  | 61%    | $3 \mathrm{W}$   | 3  ms               |

| xc6vlx240t | 11 | 26%  | 85%    | $7.8 \mathrm{W}$ | 1  ms               |

| xc6vlx550t | 18 | 18%  | 91%    | $11 \mathrm{W}$  | $.71 \mathrm{ms}$   |

| xc7a100t   | 3  | 16%  | 71%    | $1 \mathrm{W}$   | 3.5  ms             |

| xc7vx485t  | 16 | 19%  | 49%    | $5.5 \mathrm{W}$ | $.70 \mathrm{\ ms}$ |

| xc7v2000t  | 29 | 9%   | 71%    | $11 \mathrm{W}$  | $.48 \mathrm{\ ms}$ |

| xcku035    | 12 | 24%  | 68%    | $6.2 \mathrm{W}$ | $.65~\mathrm{ms}$   |

6, 7, and Ultrascale). These implementations achieve 120-200 fps while dissipating only 0.5-2.3 Watts (estimated with the XPower Analyzer tool of Xilinx). The power dissipation for each device depends on its technology node and die size (static power), as well as on the operating frequency and utilization ratio (dynamic power). The maximum frequency for the single-pipeline implementation ranges in 250–420 MHz among devices and decreases to 185–300MHz when placing/routing multiple pipelines in each device (most often decreases to 200-220 MHz). The lower part of Table 4 shows how multiple pipelines can fit in each device. Column 2 reports the maximum pipelines fitted in the device, while columns 3 and 4 report the utilization of the device's LUTs and RAMBs. We note that the bottleneck is usually in the on-chip RAM (except for the large devices, which run out of IOBs).

According to the above results, when increasing the parallelization factor P in each FPGA family we achieve an almost linear acceleration of L-SEABI; we pay a time penalty due to the lower achievable frequency (due to the high utilization ratio of the device) and due to the overhead of overlapping the image stripes to achieve

functionally equivalent super-resolution (the neighboring pipelines process partially common inputs). Roughly, for small to large factors P, the acceleration ranges from  $\frac{3}{4}P$  to  $\frac{1}{2}P$ . In the most expensive FPGA device, Virtex7 2000T, the architecture achieves 2083 fps for P = 29 (the time overhead of the image level parallelization increases at around 25% due to the extensive overlapping of the 29 stripes). In these multi-pipeline implementations, the power dissipation ranges from 1 to 11 Watts, while the energy per image decreases roughly in half when using newer generation FPGAs (e.g., Virtex7 versus Virtex5/Virtex6). Overall, by using a mid-price xc6vlx240t FPGA we can achieve 1000 fps with less than 8 Watts, whereas a low-price xc7a100t FPGA will provide 285 fps for only 1 Watt. Hence, the proposed acceleration can support a plethora of applications, single- or multi-view, high- or ultra-high definition, achieving real-time and low-power processing.

Compared to other super-resolution implementations on FPGA in the literature, the proposed single-pipeline implementation on xc6vlx240t requires almost 5x fewer logic resources than the similar module in [18]. The proposed 3-pipeline implementation requires similar resources with [19] to achieve one order of magnitude faster execution on the same xc6vlx75t FPGA device. The proposed 11-pipeline implementation on xc6vlx240t consumes a similar number of LUTs with that of the 4-core UHDTV case of [20] to achieve one order of magnitude faster execution than [20] running on Altera Aria II FPGA. Finally, when comparing to more demanding motion-estimation based SR implementations, the proposed FPGA design proves to be significantly faster and considerably cheaper: for QCIF image upsampling, a single-pipeline on Virtex5 provides up to 400x more fps with around 3x less LUTs than [49] (note however that, in general, motion-estimation based SR provides higher quality results).

# 6 Application of the proposed acceleration techniques to Stereo Correspondence algorithms

To improve our evaluation study and support the conclusions drawn from the analysis performed on L-SEABI regarding the efficiency of our acceleration techniques and the comparison of the computational platforms, we extend our work to consider a distinct type of image processing scenario: the stereo correspondence problem which, in general, requires more intensive computations compared to super-resolution. Most often, the dense stereo correspondence algorithms base their execution on intensive block-wise comparisons between two images by following an iterative full-search approach. This distinctive feature will allow us to evaluate our parallelization techniques and HW platforms in a algorithmic case that requires increased data caching and data reuse, while it offers fewer opportunities to do calculations onthe-fly due to limited spatial localities. In the current section, we consider the most representative and wellknown algorithm of its category [50], the Disparity.