# MAPPING SIGNAL PROCESSING ALGORITHMS ON PARALLEL ARCHITECTURES

$\mathbf{B}\mathbf{y}$

## NIDAL M. SAMMUR

Bachelor of Science The University of Tulsa Tulsa, Oklahoma 1984

Master of Science The University of Tulsa Tulsa, Oklahoma 1986

Submitted to the Faculty of the Graduate College of the Oklahoma State University in partial fulfillment of the requirements for the Degree of DOCTOR OF PHILOSOPHY

July, 1992

Thesis 1992D 5189m

# MAPPING SIGNAL PROCESSING ALGORITHMS ON PARALLEL ARCHITECTURES

Thesis Approved:

Mart. T Hayan

Thesis Advisor

M. Baran

Huizhu Lu

Thomas C. Collins

Dean of the Graduate College

#### **ACKNOWLEDGMENTS**

I thank God for the persistence, determination, and faith He gave throughout my years of study. Like everyone who has reached this point in his education, I could not have gotten here without the help, encouragement, and support of a lot of people.

My deepest love, thankfulness and appreciation goes to my mother. She always stood by me, supported me, and inspired me. I dedicate this dissertation to her. The most important contributor to my success, however, did not live to see me complete my education - my father. He always stressed the value of education and hard work - this dissertation could not have been done without that example. My sincere love and appreciation goes to my sisters and my brother and the rest of my family.

I would like to express my appreciation to my adviser and friend Dr. Martin Hagan for the guidance and insight he provided me throughout my study. His delightful and informative discussions, his views, and his approaches added a depth to my understanding which could not have been obtained elsewhere. I have known Dr. Hagan for more than ten years and he never stopped amazing me. He is so knowledgeable, friendly, honest, and yet humble. Thank you Dr. Hagan for being such a wonderful friend and teacher. You are simply the best.

I would like to thank Dr. Bacon, Dr. Teague, Dr Baker, and Dr. Lu for serving on my committee.

I would like to acknowledge the machine time, technical support, and encouragement given by NASA/Goddard Space Flight Center and various members of its staff, including James Fischer and Judy Devaney. I would like to acknowledge the National Center for Supercomputing Applications and the Los Alamos National Laboratory for allowing us time on their machines.

Finally, I would like to thank all my wonderful friends in Stillwater and Tulsa for all their help, encouragement, and support.

# TABLE OF CONTENTS

| Chapter | 1                                                                                                                                                                                                                                   | Page                                                 |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| I.      | INTRODUCTION                                                                                                                                                                                                                        | 1                                                    |

|         | Inverse Filtering                                                                                                                                                                                                                   | 3                                                    |

| II.     | BATCH INVERSE FILTERING ALGORITHMS                                                                                                                                                                                                  | 8                                                    |

|         | The Levinson Algorithm The Burg Algorithm The Method of Least Squares The Lp Techniques Selection of a Representative Algorithm                                                                                                     | 13<br>16<br>22                                       |

| III.    | PARALLEL PROCESSING COMPUTER ARCHITECTURES                                                                                                                                                                                          | 28                                                   |

|         | Computer Architecture Classification Scheme Description of Selected Advanced                                                                                                                                                        | 29                                                   |

|         | Computer Systems The Heterogeneous Element Processor The Cray X-MP/48 The Intel iPSC/2 Hypercube The Alliant FX/8 The Massively Parallel Processor (MPP) The Connection Machine Model CM-2 The Cray-2 Supercomputer Chapter Summary | 3 4<br>3 9<br>4 3<br>4 7<br>5 0<br>6 5<br>7 3<br>7 5 |

| IV.     | IMPLEMENTATIONS OF THE BURG ALGORITHM                                                                                                                                                                                               | 77                                                   |

|         | Sequential Implementation Parallel Implementations  MPP Implementation Hypercube Implementation Cray X-MP/48 Implementation HEP Implementation Alliant FX/8 Implementation                                                          | 79<br>80<br>86<br>89<br>90                           |

| Chapter | Page                                           |

|---------|------------------------------------------------|

|         | Connection Machine Model CM-2 Implementation   |

| V.      | PERFORMANCE ANALYSIS                           |

|         | Timing Equations                               |

| VI.     | SUMMARY AND CONCLUSION                         |

| REFEREN | NCES                                           |

| APPEND  | IXES130                                        |

|         | APPENDIX A - SEQUENTIAL BURG LISTINGS 131      |

|         | APPENDIX B - GENERATE WHITE NOISE LISTINGS 133 |

|         | APPENDIX C - SIMULATE ARMA LISTINGS135         |

|         | APPENDIX D - HEP LISTINGS                      |

|         | APPENDIX E - iPSC/2 LISTINGS141                |

|         | APPENDIX F - ALLIANT FX/8 LISTINGS148          |

|         | APPENDIX G - MPP LISTINGS                      |

|         | APPENDIX H - CM-2 LISTINGS                     |

|         | APPENDIX I - CRAY X-MP/48 LISTINGS             |

|         | APPENDIX J - CRAY-2 LISTINGS                   |

# LIST OF TABLES

| Table | Page                                                       |

|-------|------------------------------------------------------------|

| 3.1   | Reduction Functions                                        |

| 3.2   | Permutation Functions                                      |

| 3.3   | Comparison of Cray Supercomputers 74                       |

| 4.1   | Summary of Parallel Burg Algorithm on the MPP 85           |

| 4.2   | Burg Implementation on the FX/8 (no FX/Fortran Constructs) |

| 4.3   | Burg Implementation on the FX/8 (FX/Fortran constructs)    |

| 4.4   | Comparison of Burg Execution Time 98                       |

| 5.1   | iPSC/2 Deviation Term                                      |

| 5.2   | iPSC/2 Actual and Predicted Times                          |

| 5.3   | Comparative Figures for the Computers Used110              |

| 5.4   | Comparative Figures in Terms of the Four Factors           |

| 5.5   | The Six Measures                                           |

| 5.6   | Results of Applying the Six Measures (All Machines) 113    |

| 5.7   | The Ranking Results (All Machines)                         |

| 5.8   | Comparative Figures (without HEP)115                       |

| 5.9   | Results of the Six Measures (without HEP)115               |

| 5.10  | The Ranking Results (without HEP)                          |

# LIST OF FIGURES

| Figure | F                                                       | age |

|--------|---------------------------------------------------------|-----|

| 1.1    | Autoregressive Process of Order p                       | 5   |

| 2.1    | Lattice Filter Implementation of a 2nd Order AR Process | 13  |

| 3.1    | Flynn's Classification of Computer Architectures        | 3 1 |

| 3.2    | Organizational Space of Parallel Computer Systems       | 3 4 |

| 3.3    | Four-Processor HEP System                               | 36  |

| 3.4    | Routing Control in the 3-ported Switch Node             | 3 7 |

| 3.5    | HEP Position in the Organizational Space                | 39  |

| 3.6    | The Cray X-MP/48 Overall System Organization            | 4 1 |

| 3.7    | Cray Position in the Organizational Space               | 43  |

| 3.8    | The Hypercube Topology                                  | 44  |

| 3.9    | Hypercube Position in the Organizational Space          | 47  |

| 3.10   | The Architecture of the Alliant FX/8                    | 48  |

| 3.11   | Alliant Position in the Organizational Space            | 50  |

| 3.12   | Overall Block Diagram of the MPP                        | 5 2 |

| 3.13   | The ARU                                                 | 53  |

| 3.14   | Topologies Available on the MPP's ARU                   | 5 5 |

| 3.15   | The Processing Element                                  | 56  |

| 3.16   | The Array Control Unit                                  | 58  |

| 3.17   | MPP Position in the Organizational Space                | 61  |

| 3.18   | Example of MPP Pascal Code and Storage                  | 63  |

| Figure | Pag                                                   | ţе |

|--------|-------------------------------------------------------|----|

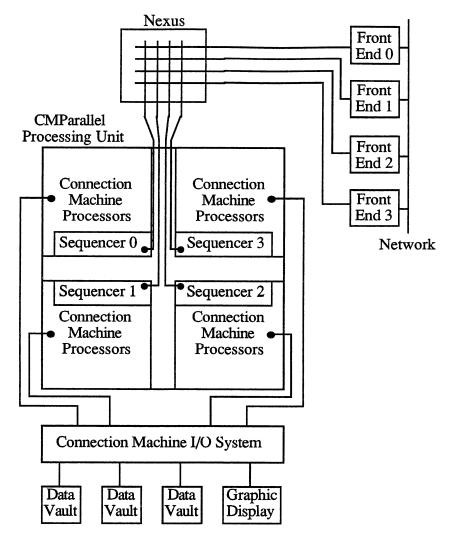

| 3.19   | The Connection Machine CM-2 Overall Block Diagram     | 6  |

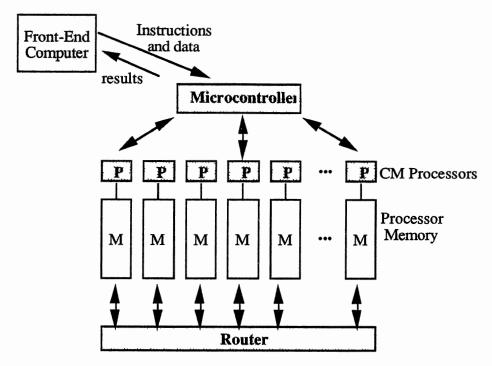

| 3.20   | The Architecture of a Sequencer 6                     | 8  |

| 3.21   | CM-2 Position in the Organizational Space 7           | 3  |

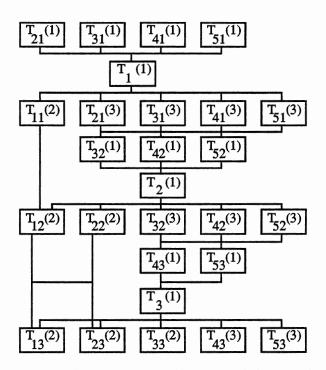

| 4.1    | Sequential Implementation of the Burg Algorithm 7     | 9  |

| 4.2    | Maximally Parallel Graph for M=5 and MAX=3 8          | 0  |

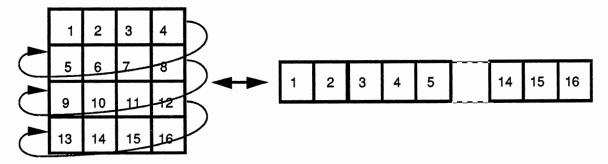

| 4.3    | Mapping a Linear Array on a Mesh 8                    | 1  |

| 4.4    | Data Movement for the Burg Filter in a Linear Array 8 | 3  |

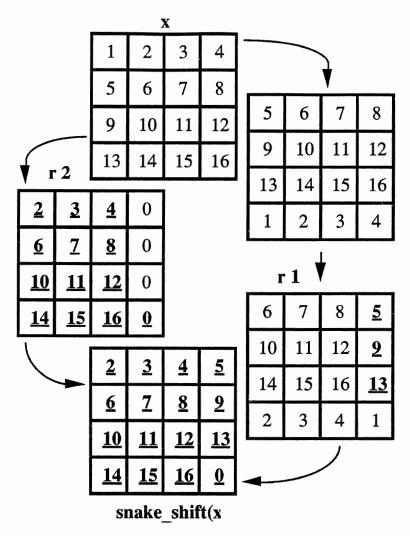

| 4.5    | Procedure Snake_shift (x) 8                           | 5  |

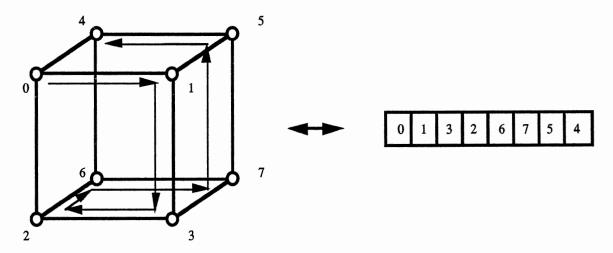

| 4.6    | Mapping a Linear Array on a 3-D Hypercube 8           | 6  |

| 4.7    | Data Movement for the Burg Filter in a Linear Array   | 8  |

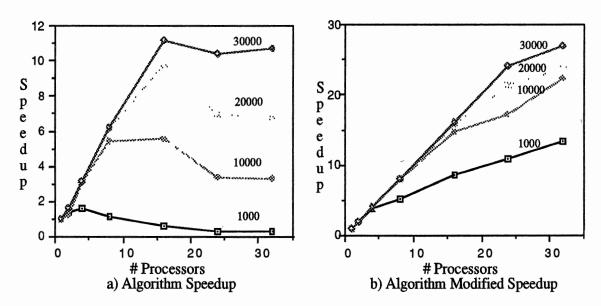

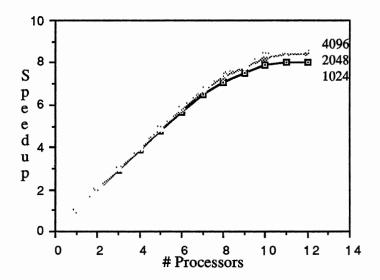

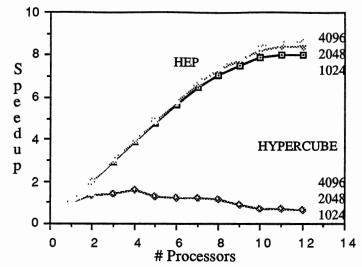

| 4.8    | Speedup on the Hypercube 8                            | 9  |

| 4.9    | Algorithm Speedup on the HEP 9                        | 2  |

| 4.10   | Comparison of HEP and Hypercube Speedups 10           | 00 |

#### CHAPTER I

#### INTRODUCTION

Digital signal processing is a field of study concerned with the processing of information represented in digital form. Certain techniques in the field can be traced back to numerical algorithms performed in the seventeenth and eighteenth century. However, the advent of modern high-speed digital computing devices has caused a revolution in applications of the theory to a variety of problems. Signal processing is used in such areas as biomedical data processing [1], sonar and radar processing [2], speech processing [3], data communication [4], seismic signal processing [5], adaptive system identification [6], adaptive control applications [7], and a host of other applications [8-11]. One of the most interesting aspects of digital signal processing is this wide variety of applications. This has served to create a vitality in the field that is often missing in other scientific fields of study.

Digital signal processing has become an increasingly significant field because of the technology associated with digital computers. A digital computer used to process signals offers a tremendous advantage in flexibility. The emergence of parallel processing and very large scale integration (VLSI) motivated the researchers in the field of digital signal processing to find and explore new ways to

implement and design efficient and highly parallel algorithms [11-18].

The conventional sequential digital computers suffer from one serious drawback: the von Neumann bottleneck. This phenomenon accounts for the sometimes slow and inefficient use of conventional serial processor resources. In a sequential computer, a single memory buffer serves as the only gate between the high-speed memory and the central processing unit (CPU). This makes it necessary to organize all computational tasks in a strictly sequential fashion. Processing speed is limited not by the speed of the CPU but the narrow pathway between the CPU and memory. Parallelism is one of the major innovations in the hardware design of digital computers that have permitted the circumventing of the von Neumann bottleneck so as to attain high speeds [19-20].

A parallel processing computer, simply defined, is one that can perform operations using more than one processor simultaneously. The central problem parallel processing systems face is how to effectively and efficiently use more than one processor at the same time. The effectiveness of the system depends on whether one can identify a problem that lends itself to parallelism, determine the algorithm, and map it onto a suitable architecture. There are no established principles revealing how to automate the arduous manual task of partitioning any real-world problem so that it can be parcelled out to many processors simultaneously [21-22].

The main objective of this research is to explore the different techniques of mapping digital signal processing algorithms onto advanced computer architectures. It is impossible to cover all algorithms and all architectures. The spectrum of the algorithms covered was limited to those which can be characterized as one dimensional, batch, and time domain. As for the architectures, the availability of such systems was the major limitation. The goal of this research is to discover the types of computer architectures which are best suited for signal processing.

This dissertation contains six chapters each of which is dedicated to present a concise set of ideas. The rest of this chapter concentrates on presenting a preliminary system identification theory that sets the stage for the second chapter. Chapter II discusses the batch algorithms that are used for inverse filtering and concentrates on the similarities between these algorithms. algorithm is selected for parallel implementation since it is a good representative of this group of algorithms. Chapter III presents the different advanced computer architectures and discusses in detail those architectures that are used in this research. Chapter IV discusses the implementations of the algorithm chosen on a selected number of advanced computer architectures. Chapter V contains the performance analysis performed on the results obtained in chapter IV. A ranking of the machines is presented. Finally, chapter VI summarizes the main ideas presented in this work followed by some general conclusions.

## Inverse Filtering

A problem of great importance is determining the parameters of a model given observations of the physical process being modeled [23]. In control theory this problem is often called the system identification problem [6]; one of the most important applications of identification methods is adaptive estimation and control. Parameter identification problems also arise in several digital signal processing algorithms; applications include seismic signal processing and the analysis, coding, and synthesis of speech. In seismic signal processing the problem is termed deconvolution [3], while it is termed linear prediction in speech processing [5]. Other names have been used like parameteric spectrum analysis and inverse scattering [8-9]. Inverse filtering is a more natural term to use and is adopted throughout this report.

In this report we address the problem of inverse filtering for a particular underlying time series model, namely the autoregressive (AR) process. The general form for an AR process of order p is given by equation (1-1).

$$z_t = \phi_1 \ z_{t-1} + ... + \phi_p \ z_{t-p} + e_t$$

(1-1)

The current value of the process  $z_t$  is expressed as a weighted sum of past values plus a random white noise  $e_t$  with a variance of  $\sigma_e^2$ . Thus  $z_t$  can be considered to be regressed on the p previous z's, hence the name. The weights on the previous z's are called the AR parameters. The right hand side of equation (1-1), excluding the white noise, is called the prediction of  $z_t$  based on  $z_{t-1}$  thru  $z_{t-p}$ , and the white noise is termed the prediction error. The inverse filtering problem is summarized as follows: given the set of

observations for the process, or the time series  $z_t$ , find the underlying AR parameters that best characterize the process.

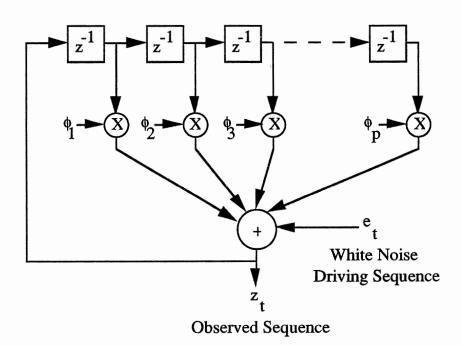

The AR process given by equation (1-1) can be represented in a block diagram form as shown in Figure 1.1. The blocks with z<sup>-1</sup> indicate unit delay. The structure depicted here is sometimes referred to as a tapped delay line or direct form I implementation.

Figure 1.1 Autoregressive Process of Order p

It should be noted that an AR process has an all-pole transfer function given by equation (1-2). This property justifies the use of AR processes to model spectra with sharp peaks.

$$H(z) = \frac{1}{1 + \phi_1 z^{-1} + \phi_2 z^{-2} + \dots + \phi_p z^{-p}}$$

(1-2)

A plethora of inverse filtering methods are discussed in the literature which are based on the autocorrelation function, the partial autocorrelation function, and the generalized partial autocorrelation function [24-25]. The methods based on the first two functions are of major interest in this research.

The autocorrelation function of the AR process given by equation (1-1) can be determined by first multiplying equation (1-1) by  $z_{t-k}$  to get equation (1-3), then taking the expected values to get equation (1-4).

$$z_{t-k}z_t = \phi_1 z_{t-k} z_{t-1} + \dots + \phi_p z_{t-k} z_{t-p} + z_{t-k}e_t$$

(1-3)

$$\gamma_{k} = \phi_{1} \gamma_{k-1} + \phi_{2} \gamma_{k-1} + ... + \phi_{p} \gamma_{k-p} + \begin{cases} \sigma_{e}^{2} & , k=0 \\ 0 & , k>0 \end{cases}$$

(1-4)

If the estimated order of the process is denoted by m we can rewrite equation (1-4) with an extra index for the  $\phi$ 's as shown in equation (1-5).

$$\gamma_{k} = \phi_{m1} \gamma_{k-1} + \phi_{m2} \gamma_{k-1} + \dots + \phi_{mm} \gamma_{k-m} + \begin{cases} \sigma_{e}^{2} & , k=0 \\ 0 & , k>0 \end{cases}$$

(1-5)

The parameter  $\phi_{mm}$  is called the partial autocorrelation function at lag m. If we let k vary from 0 to m in equation (1-5) we get a set of

linear equations for the  $\phi$ 's in terms of the  $\gamma$ 's. Equation (1-6) shows the resulting equations organized within matrices.

$$\begin{bmatrix} \gamma_0 & \gamma_1 & \dots & \gamma_m \\ \gamma_1 & \gamma_0 & \dots & \gamma_{m-1} \\ \vdots & \vdots & & \vdots \\ \gamma_m & \gamma_{m-1} & \dots & \gamma_0 \end{bmatrix} \begin{bmatrix} 1 \\ \phi_{m1} \\ \vdots \\ \vdots \\ \phi_{mm} \end{bmatrix} = \begin{bmatrix} \sigma_e^2 \\ 0 \\ \vdots \\ \vdots \\ 0 \end{bmatrix}$$

$$(1-6)$$

Equation (1-6) is called the Yule-Walker or normal equation [23]. The matrix that contains the autocorrelations is called the autocorrelation matrix. This matrix is both symmetric and Toeplitz.

If m is the true order of the AR process (i.e., m=p) then  $\phi_{m1}=\phi_{1},...,\phi_{mm}=\phi_{m}$ . Therefore one technique for inverse filtering is to substitute estimated values for the autocorrelation function in equation (1-6) and to solve for  $\phi_{m1},...,\phi_{mm}$  and  $\sigma_{e}^{2}$ .

In chapter II, we explore several algorithms for inverse filtering. We will be investigating these algorithms looking for the commonality among them and choosing an algorithm that represents this class of algorithms.

#### CHAPTER II

#### **BATCH INVERSE FILTERING ALGORITHMS**

The previous chapter presented the problem of inverse filtering and the Yule-Walker or normal equation was discussed. This chapter presents some batch algorithms that solve the normal equation efficiently. By solving the normal equation, an estimate of the AR process parameters can be obtained thus achieving the goal of the inverse filtering problem.

The objective of this chapter is to study the batch algorithms, identify their similarities and differences, and finally, choose one algorithm that is representative of this class of algorithms. The selected algorithm will be the one to be implemented on advanced computer architectures. The results of implementing the selected algorithm on the different machines will be applicable to other batch algorithms.

## The Levinson Algorithm

The Levinson algorithm is an efficient algorithm for solving the normal equation without inverting the autocorrelation matrix.

Instead of solving the normal equation directly, the Levinson algorithm imbeds this problem into a whole class of similar problems; namely, of determining the best linear predictors of

ascending orders. The name linear prediction originate from the formulation of the model; the basic assumption is that the next sample in a sequence can be estimated from a linearly weighted sum of previous samples [26-28].

The solution is obtained in an iterative manner, by solving a family of matrix equations of lower dimensionality. Starting at the upper left corner of the autocorrelation matrix (the first element in the first row), i.e. first order equation, and successively increasing the order until the desired dimension is reached. The solution of each problem is obtained in terms of the solution of the previous one. In this manner, the final solution is gradually built up. In the process, one also finds all the lower order prediction error filters. Order determination is inherently performed by the Levinson algorithm.

The iteration is based on two key properties of the autocorrelation matrix: first, the autocorrelation matrix of a given size contains as subblocks all the lower order autocorrelation matrices; and second, the autocorrelation matrix is symmetric and Toeplitz, i.e., it is reflection invariant [29].

Equation (2-1) is the AR process of m<sup>th</sup> order discussed in the previous chapter [30].

$$x_n + a_1^m x_{n-1} + \cdots + a_m^m x_{n-m} = e_n^m$$

(2-1)

Using the approach followed in the previous chapter, the normal equation can be rewritten as shown in equation (2-2). This equation is equivalent to equation (1-6) but uses different variable names.

R(k) is the autocorrelation function, the a's are the AR parameters, and  $P_m$  is the variance of the white noise  $e_n^m$ .

$$\begin{bmatrix} R(0) & R(-1) & \cdots & R(-m) \\ R(1) & R(0) & \cdots & R(1-m) \\ \vdots & \vdots & \ddots & \vdots \\ R(m) & R(m-1) & \cdots & R(0) \end{bmatrix} \begin{bmatrix} 1 \\ a_1^m \\ \vdots \\ a_m^m \end{bmatrix} = \begin{bmatrix} P_m \\ 0 \\ \vdots \\ 0 \end{bmatrix}$$

(2-2)

Consider the case of having solved equation (2-2) and wanting to increase the order of the model. Equation (2-3) shows the AR process of increased order, namely, m+1.

$$x_n + a_1^{m+1} x_{n-1} + \cdots + a_m^{m+1} x_{n-m} + a_{m+1}^{m+1} x_{n-m-1} = e_n^{m+1}$$

(2-3)

Using equation (2-3) the new normal equation is shown by equation (2-4).

$$\begin{bmatrix} R(0) & R(-1) & \cdots & R(-m) & R(-m-1) \\ R(1) & R(0) & \cdots & R(1-m) & R(-m) \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ R(m) & R(m-1) & \cdots & R(0) & R(-1) \\ R(m+1) & R(m) & \cdots & R(1) & R(0) \end{bmatrix} \begin{bmatrix} 1 \\ a_1^{m+1} \\ \vdots \\ a_{m+1}^{m+1} \\ a_{m+1}^{m+1} \end{bmatrix} = \begin{bmatrix} P_{m+1} \\ 0 \\ \vdots \\ 0 \\ 0 \end{bmatrix}$$

(2-4)

Comparing equations (2-2) and (2-4) it is clear that the new autocorrelation matrix consists of the old matrix plus an extra row and column. Equation (2-4) can be rewritten as shown in equation (2-5). This expression is valid since the first and last rows of the autocorrelation matrix are reverses, the second and next to last rows are reverses, etc. (R(k) = R(-k)).

$$\begin{bmatrix} R(0) & R(-1) & \cdots & R(-m) & R(-m-1) \\ R(1) & R(0) & \cdots & R(1-m) & R(-m) \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ R(m) & R(m-1) & \cdots & R(0) & R(-1) \\ R(m+1) & R(m) & \cdots & R(1) & R(0) \end{bmatrix} \begin{bmatrix} 1 \\ a_1^m \\ \vdots \\ a_m^m \\ 0 \end{bmatrix} + c_{m+1} \begin{bmatrix} 0 \\ a_m^m \\ \vdots \\ a_1^m \\ 1 \end{bmatrix}$$

$$= \begin{bmatrix} P_m \\ 0 \\ \vdots \\ 0 \\ Q_{m+1} \end{bmatrix} + c_{m+1} \begin{bmatrix} Q_{m+1} \\ 0 \\ \vdots \\ 0 \\ P_m \end{bmatrix}$$

(2-5)

By inspection of equation (2-5) the following equation can be written:

$$Q_{m+1} = \sum_{n=0}^{m} R(m+1-n) a_n^m$$

(2-6)

Now let

$$c_{m+1} = -\frac{Q_{m+1}}{P_m}$$

or  $Q_{m+1} + c_{m+1} P_m = 0$  (2-7)

Equation (2-5) will have the same form as equation (2-4), in which the first element of the left hand column vector is unity and the last m+1 elements of the right hand column vector are zero. We have thus found a solution to equation (2-4), and if we assume that the autocorrelation matrix is positive definite the solution must be unique [30]. The solution is given by equation (2-8):

l

$$\begin{bmatrix} 1 \\ a_{1}^{m+1} \\ \vdots \\ a_{m+1}^{m+1} \\ a_{m+1}^{m+1} \end{bmatrix} = \begin{bmatrix} 1 \\ a_{1}^{m} \\ \vdots \\ a_{m}^{m} \\ 0 \end{bmatrix} + c_{m+1} \begin{bmatrix} 0 \\ a_{m}^{m} \\ \vdots \\ a_{1}^{m} \\ 1 \end{bmatrix}$$

(2-8)

where  $c_{m+1}$  is obtained from equation (2-7). By comparing equations (2-4) and (2-5) we can also see that:

$$P_{m+1} = P_m + c_{m+1} Q_{m+1} = P_m + c_{m+1} (-c_{m+1} P_m) = P_m (1 - c_{m+1}^2)$$

(2-9)

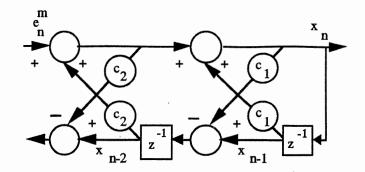

The parameter c<sub>m+1</sub> is called the reflection coefficient or the partial autocorrelation function. Equation (2-8) indicates the relationship of the reflection coefficients to the AR parameters. If the reflection coefficients are used instead of the AR parameters to realize an AR process, an interesting filter structure results as shown in Figure 2.1. Figure 2.1 is the lattice form realization of the AR process as opposed to Figure 1.1 that illustrates the direct form I realization. The lattice filter is an important structure in signal processing due to its modular structure and special features. The derivation of the Burg algorithm in the next section describes the equations that result in this interesting filter structure.

To summarize, the Levinson algorithm consists of equations (2-6), (2-7), (2-8), and (2-9). It is a recursive algorithm for estimating the coefficients of an AR process without a-priori knowledge of the process order. At the k-th iteration of the algorithm we obtain the AR coefficients of the k-th order model:  $a_1^k, a_2^k, \dots, a_k^k$ .

Figure 2.1 Lattice Filter Implementation of a 2nd Order AR process

#### The Burg Algorithm

The Burg algorithm is similar to the Levinson algorithm in that it estimates the coefficients of an AR process which are updated recursively using equation (2-8). The Burg differs from the Levinson algorithm in the way it calculates the reflection coefficients [30-31].

To derive the Burg algorithm, first consider the forward prediction error of the m+1<sup>th</sup> order AR model: (the prediction is forward in the sense that the prediction for the current data sample is a weighted sum of previous samples)

$$e_n^{m+1} = x_n + a_1^{m+1} x_{n-1} + \cdots + a_m^{m+1} x_{n-m} + a_{m+1}^{m+1} x_{n-m-1}$$

(2-10)

If equation (2-8) is used to obtain the coefficients, equation (2-10) can be rewritten as:

$$e_n^{m+1} = x_n + \left(a_1^m + c_{m+1} \ a_m^m\right) x_{n-1} + \cdots + \left(a_m^m + c_{m+1} \ a_1^m\right) x_{n-m} + c_{m+1} x_{n-m-1}$$

(2-11)

Now consider the forward prediction error of the mth order model:

$$e_n^m = x_n + a_1^m x_{n-1} + \cdots + a_m^m x_{n-m}$$

(2-12)

There is an equivalent backward prediction model: ( the prediction is backward in the sense that the prediction for the current data sample is a weighted sum of future samples)

$$b_{n-m-1}^{m} = x_{n-m-1} + a_1^{m} x_{n-m} + \cdots + a_m^{m} x_{n-1}$$

(2-13)

It can be shown that the statistics of this model are equivalent to those of the forward prediction model.

By comparing equation (2-11) with equations (2-12) and (2-13), we can see that:

$$e_n^{m+1} = c_{m+1} b_{n-m-1}^m + e_n^m$$

(2-14)

Likewise, we could show:

$$b_{n-m-1}^{m+1} = b_{n-m-1}^{m} + c_{m+1} e_{n}^{m}$$

(2-15)

The Burg algorithm chooses  $c_{m+1}$  so as to minimize the sum of squares of the forward and backward prediction errors:

$$J = \sum_{n=m+2}^{M} (e_n^{m+1})^2 + (b_{n-m-1}^{m+1})^2$$

(2-16)

If equations (2-14) and (2-15) are used in equation (2-16) we can rewrite the latter as:

$$J = \sum_{n=m+2}^{M} (e_n^m + c_{m+1} b_{n-m-1}^m)^2 + (b_{n-m-1}^m + c_{m+1} e_n^m)^2$$

(2-17)

To minimize equation (2-17) we take its derivative with respect to  $c_{m+1}$ , set it equal to zero, and solve for  $c_{m+1}$ . The derivative is given by:

$$2\sum \left(e_{n}^{m}+c_{m+1}\ b_{n-m-1}^{m}\right)b_{n-m-1}^{m}+2\sum \left(b_{n-m-1}^{m}+c_{m+1}\ e_{n}^{m}\right)e_{n}^{m} \tag{2-18}$$

Rearranging equation (2-18) and setting it equal to zero result in equation (2-19).

$$\sum \left( e_n^m b_{n-m-1}^m + b_{n-m-1}^m e_n^m \right) + c_{m+1} \sum \left( \left( b_{n-m-1}^m \right)^2 + \left( e_n^m \right)^2 \right) = 0$$

(2-19)

Solving for  $c_{m+1}$  result in the reflection coefficients that minimize the sum of squares of the forward and backward errors:

$$c_{m+1} = \frac{-2\sum_{n=m+2}^{M} e_n^m b_{n-m-1}^m}{\sum_{n=m+2}^{M} \left(e_n^m\right)^2 + \left(b_{n-m-1}^m\right)^2}$$

(2-20)

To summarize, the Burg algorithm consists of two steps: 1) update the forward and backward prediction errors using equations (2-14) and (2-15); 2) calculate the reflection coefficient using equation (2-20) and then repeat step 1). If the AR parameters are desired they are calculated using equation (2-8), as in the Levinson algorithm. This implies that the lattice filter implementation of the AR process is valid when the Burg algorithm is used. In fact, the forward and backward prediction errors given by equations (2-14) and (2-15) constitute the lattice structure shown in Figure 2.1.

The Burg algorithm uses equation (2-8) from the Levinson algorithm to update the coefficients of the AR model, but it differs from the Levinson algorithm in that it chooses the reflection coefficient,  $c_{m+1}$ , so as to minimize the sum of squares of the forward and backward prediction errors.

Notice that equations (2-14) and (2-15) involve a time shift of the b sequence relative to the e sequence, and that equation (2-20) involves three inner product operations. This combination of operations is found in all algorithms which use convolution or correlation.

### The Method of Least Squares

The least squares method is one of the most popular and useful techniques for obtaining parameter estimates of an unknown system or signal model. The convergence properties of least squares estimates have been well established [23].

We begin by discussing the general problem and the proposed solution. Consider the problem of finding a vector  $x \in \mathbb{R}^n$  such that Ax=b where  $A \in \mathbb{R}^{m \times n}$  and  $b \in \mathbb{R}^m$  are given and m>n. When there are more equations than unknowns, we say that the system Ax=b is overdetermined. Usually an overdetermined system has no exact solution.

This suggests that we strive to minimize  $|Ax-b|_p$  for some suitable choice of p. Different norms render different optimum solutions. Minimization in the 1-norm and  $\infty$ -norm is complicated by the fact that the function  $|Ax-b|_p$  is not differentiable for those values of p. However, the next section discuss the case where  $1 \le p < 2$  and present efficient techniques to solve the problem. On the other hand,  $|Ax-b|_2$  is a continuously differentiable function of x [32].

The least squares formulation can be applied to the problem of estimating the parameters of an autoregressive process. Assume the data sequence  $x_0, ..., x_{N-1}$  is used to find the  $m^{th}$  order AR parameter estimates. Recall equation (2-1) that describes an  $m^{th}$  order AR process. Equation (2-21) is equivalent to equation (2-1) rewritten to express the output in terms of the weighted sum of the previous output values and the white noise process.

$$x_n = -a_1^m x_{n-1} - \cdots - a_m^m x_{n-m} + e_n^m$$

(2-21)

We can evaluate  $e_n^m$  in equation (2-21) for n=1 to n=N+m-2 if one assumes the terms outside the measurements are zero, i.e.,  $x_n=0$  for n<0 and n>N-1. Notice the existence of an implied

windowing of the data sequence in order to extend the index range from 1 to N+m-2. Using a matrix formulation we can rewrite equation (2-21) for the specified range as shown in equation (2-22).

Recall that the forward linear predictor will have the usual form:

$$\hat{x}_{n} = -(a_{1}^{m} x_{n-1} + \cdots + a_{m}^{m} x_{n-m}) = -\sum_{i=1}^{m} a_{i}^{m} x_{n-i}$$

(2-23)

and the forward linear predictor error or residual is given by:

$$e_n^m = x_n - \hat{x}_n = -\sum_{i=0}^m a_i^m x_{n-i}$$

; where  $a_0^m = 1$  (2-24)

Notice that the forward linear predictor error is equivalent to the white process, i.e. the E vector in equation (2-22), given that the process is autoregressive.

Using equation (2-22), we can solve for the residual vector:

$$E=Y-XA (2-25)$$

Notice that  $E^TE$  is simply the sum of squares of the residuals or errors. In the least squares method the objective is to minimize the sum of squares of the errors, i.e.  $E^TE$ . Thus the cost function to be minimized is given by:

$$J = E^{T}E = (Y-XA)^{T}(Y-XA) = Y^{T}Y-Y^{T}XA-A^{T}X^{T}Y+A^{T}X^{T}XA$$

(2-26)

Differentiating J with respect to the vector A, setting it to zero, and rearranging will give the following system of normal equations:

$$(X_k^T X_k) A = X_k^T Y (2-27)$$

The subscript k indicates which data matrix is used. There are four different possibilities, illustrated in equation (2-22), for the selection of the data matrix [28]. Hence, k takes on the values 1, 2, 3, or 4 depending on our windowing choice to indicate the selection of the covariance, the autocorrelation, the prewindowed, or the postwindowed formulation, respectively. Solving for A in equation (2-27) will result in the least squares solution given by:

$$A = (X^T X)^{-1} X^T Y$$

(2-28)

In practice, the vector A is not computed using equation (2-28) since the computation of the inverse is fraught with numerical difficulties. Instead, the normal equation (2-27) is solved using numerically stable algorithms that involve orthogonal transformations. Hence, equation (2-28) is a useful "theoretical" formula but is not a useful computational formula [23].

Equation (2-27) has the same structure as the Yule-Walker equations; however, the data matrix product  $(X_k^T X_k)$  is not necessarily Toeplitz as are the Yule-Walker equations [32]. Notice that the subscript k is used to indicate the data matrix selected as mentioned earlier.

If the data matrix  $X_1$  is selected, the normal equations are termed the covariance equations or formulation, often encountered in linear predictive coding (LPC) of speech [28]. The  $(X_1^TX_1)$  matrix is symmetric but not Toeplitz. The square root method or Cholesky decomposition is used in this case for computing the A vector [33]. The Cholesky decomposition factors the data matrix product, which has the properties of a covariance matrix, to solve the system given by equation (2-22). Cholesky decomposition states that: if a matrix A is symmetric positive definite, then there exists a lower triangular matrix G with positive diagonal entries such that [32]:

$$A = L D L^{T} = (L D^{1/2}) (D^{1/2} L^{T}) = G G^{T}$$

(2-29)

To avoid square root computations, the factors L and D are computed rather than the factor G. L is a unit lower triangular and D is a diagonal matrix with positive elements. The elements of L and D can be determined by equating the elements of both sides in equation (2-29). If the first i-1 columns of L and D have been determined then the i-th column can be determined as:

$$d_i = a_{ii} - \sum_{k=1}^{i-1} d_k l_{ik}^2$$

(2-30)

$$I_{ji} = (a_{ji} - \sum_{k=1}^{i-1} d_k I_{jk} I_{ik}) / d_i \qquad i < j \le n$$

(2-31)

The Cholesky decomposition requires  $n^3/6$  operations which is more than required by the Levinson algorithm, namely,  $2n^2$  operations [32].

If the data matrix  $X_2$  is selected, the normal equations are called the autocorrelation equation or formulation since the product matrix  $(X_2^TX_2)/N$  reduces exactly to the Yule-Walker equations, for which the biased autocorrelation estimator has been used instead of the known autocorrelation function [28]. Notice that a data window has been assumed for this case. In this case, the  $(X_2^TX_2)$  matrix is Toeplitz and the A vector can be solved for using the Levinson algorithm discussed in section 2.1.

If the data matrix  $X_3$  is selected, the normal equations are termed the prewindowed normal equations due to the zero value assumptions made for the missing data prior to  $x_0$ .

If the data matrix X4 is selected, the normal equations are termed the postwindowed normal equations since a zero data assumption is made for the data beyond xN-1.

It would appear that only the data matrix X<sub>2</sub> will yield normal equations with Toeplitz structure to permit an efficient recursive solution (namely, the Levinson algorithm). However, even though

the product matrix  $(X_k^T X_k)$  may not be Toeplitz, each of the four matrices  $X_k$  have Toeplitz structure.

## The LP Techniques

In the previous section the least squares method was investigated to explore the possibilities of using such method in inverse filtering. The main idea in setting up the least squares formulation is to minimize the sum of squared residuals or errors. The residuals are the difference between the actual data and the model. The solution obtained is the least squares solution which can be termed the L2 solution. The number 2 indicates the residual terms are raised to the second power before summing.

In the previous section it was indicated that in general, one could raise the residual terms to some arbitrary p<sup>th</sup> power and perform the minimization to get the L<sub>p</sub> solution. In L<sub>p</sub> techniques, the values of p other than two may offer some advantages in a number of ways. For example, the L<sub>1</sub> (absolute value) solution tends to ignore outliers while the L<sub>2</sub> solution tries to satisfy all points as best it can. In general, values of p between one and two blend these characteristics somewhat [34-39].

Other values for p, such as p<1 and even negative p, can be considered but unfortunately the results obtained for this range do not have a mathematical basis, as L<sub>p</sub> is not a normed linear space. The solutions for p>2 are more sensitive to aberrant noise. The parameter p controls the trade-off between emphasizing and

deemphasizing aberrant noise. The L<sub>1</sub> solution is considered to be robust for its low sensitivity to aberrant noise [38].

The previous section described some of the algorithms to get the least squares solution efficiently. Unfortunately there is no simple solution for the L<sub>p</sub> case but special iterative algorithms were developed to efficiently obtain the solution. Linear programming was used to get the L<sub>1</sub> solution but could not be used to obtain the general L<sub>p</sub> solution. The iterative reweighted least squares (IRLS) algorithm can be used to get the L<sub>p</sub> solution, but in general, the pnormed solution can be efficiently solved by using the residual steepest descent (RSD) algorithm which is a steepest descent method with an adaptive stepsize [34,37,39].

Linear programming formulations have two drawbacks: for a large data set linear programming requires an excessive amount of memory, in addition, it does not guarantee selection of a reasonable prediction error filter from the several possible solutions. By contrast, the IRLS algorithm starts from the least squares solution and iterate toward a solution from there. Each iteration solves a new L2 problem by employing the weighted residuals of the previous iteration in the current one [34, 37, 39]. The rest of this section will describe the IRLS and the RSD algorithms.

The IRLS algorithm is based on the least squares solution. It is an iterative algorithm that uses a weighted least squares to solve the Lp formulation. The equation (2-22), used in the previous section to set up the least squares problem, is also used here as the basis to set up the formulation. Equation (2-32) is equivalent to equation (2-22) repeated here in matrix notation.

$$Y = XA + E \tag{2-32}$$

The problem again is to estimate the A vector. The IRLS algorithm estimates the A vector for a selected p value iteratively. The first step in the IRLS is to compute [34,37,39]:

$$A(k+1) = (X^{T} W(k) X^{T})^{-1} X^{T} W(k) Y$$

(2-33)

where W(k) is a diagonal matrix with its diagonal entries,  $W_{ii}(k)$ , given by:

$$W_{ii}(k) = \begin{cases} \left| r_i(k) \right|^{p-2}, & \left| r_i(k) \right| > \epsilon \\ \epsilon^{p-2}, & \left| r_i(k) \right| \le \epsilon \end{cases}$$

(2-34)

where  $r_i(k)$ , the residual, is given by:

$$r_i(k) = (Y - X A(k))_i$$

(2-35)

and  $\epsilon$  is some small positive number. Notice that if p=2, the W matrix will be equivalent to the identity matrix and equation (2-33) will be equivalent to the least squares solution given by equation (2-28). In fact the least squares solution can be used as an initial vector to solve for an arbitrary  $L_p$  solution.

Although the IRLS is a fast convergent algorithm, it still requires the computation of an inverse for a matrix at each stage k. Fast IRLS algorithms, based on fast Fourier transforms, were

developed to reduce the number of computations where the matrix X takes a special form [34].

The RSD algorithm uses fewer number of operations per iteration than the IRLS algorithm. The RSD solves the problem iteratively by the recursion [34,37,39]:

$$A(k+1) = A(k) - \Delta_k (X^T X)^{-1} X^T v(k)$$

(2-36)

where

$$v(k) = col [v_1(k) v_2(k) ... v_{N+m-2}(k)]$$

(2-37)

with

$$v_i(k) = |(X A(k) - Y)_i|^{p-1} sgn(X A(k) - Y)_i$$

(2-38)

where sgn(t)=+1 (-1) if t>0 (t<0). When t=0, one can arbitrarily choose sgn(t) to be either +1 or -1. The step size or the scale factor  $\Delta_k$  is determined by minimizing:

$$\| -Y + X A(k) - \Delta_k X (X^T X)^{-1} X^T v(k) \|_p$$

(2-39)

with respect to  $\Delta_k$  in the  $L_p$  sense. In equation (2-39), since the only unknown is  $\Delta_k$  and it is a scalar, we can use the IRLS algorithm to solve for  $\Delta_k$ . Notice that in the RSD algorithm we need to compute the matrix inverse only once, thus, reducing dramatically the number of computations required when compared to the IRLS algorithm.

### Selection of a Representative Algorithm

In this chapter a description of the various batch inverse filtering algorithms was presented. The algorithms were derived to study their computational structure to select the algorithm that best represents this class of algorithms.

The algorithms seem to have a common computational structure, namely, a time shift/inner product operation. In fact, this operation is a key step in performing all signal processing algorithms which involve convolution or correlation.

The Burg algorithm is selected to represent this class of algorithms for several reasons. The time shift/inner product operation constitutes a large portion of the algorithm. The Burg algorithm generates models that are always stable and yield a solution in terms of reflection coefficients. The lattice structure embedded in the Burg algorithm makes it modular and stable.

The Levinson recursion was shown to be embedded in the Burg algorithm. The least squares solution using the autocorrelation formulation can be solved efficiently using the Levinson algorithm. Notice that the least squares autocorrelation formulation is always guaranteed to yield a stable filter, by contrast, the covariance formulation does not.

In the general  $L_p$  problem, no formulation mentioned so far can assure stability except for the autocorrelation form with p=2; other values of p may yield unstable models, no matter which method is used. In particular, the autocorrelation model is always stable for p less than three and greater or equal to two, but there may exist

some  $p_0$  in the interval  $1 < p_0 < 2$  for which the prediction filter may not be stable. In that case, stability is not assured for any model generated in the range 1 [37,38]. Filter stability can be assured by using a different formulation of the linear prediction problem, namely, the lattice or Burg algorithm. In fact, generalized Burg algorithms which ensure filter stability for the L<sub>1</sub> solution were investigated in the literature [37,40].

#### CHAPTER III

# PARALLEL PROCESSING COMPUTER ARCHITECTURES

The basic definition of parallelism is the ability to do more than one activity at once. Doing n different activities at once; doing one activity in n simultaneous parts; doing n activities staggered in time; using k resources for n jobs; and k resources for one job - all of the above represent instances of parallelism. The common thread that runs through these examples is the utilization of multiple resources in an instance of time to increase the amount of work performed per unit of time.

Despite early intellectual flirtations with parallelism, until recently it has remained largely a concept. During the past two decades, several parallel processor prototypes have been built. One of particular note was the ILLIAC IV, conceived at the University of Illinois by Daniel Slotnick in 1966 as quadrants of 64 processing elements, but reduced down to one by 1972 because of technical difficulties. Recently, we are starting to see more and more parallel designs successfully executed and commercially available.

This chapter describes a classification scheme for computers and selectively describes, in detail, seven advanced computer systems.

The seven computer systems described represent different architectures: the Denelcor HEP, a shared memory (tightly coupled)

multiple-instruction stream multiple-data stream (MIMD) machine with switch network interconnect architecture; the Cray X-MP/48, a shared memory (tightly coupled) MIMD supercomputer with direct connect interconnect architecture; the Intel iPSC/2 hypercube computer, a distributed memory (loosely coupled) MIMD machine; the Alliant FX/8, a shared memory (tightly coupled) MIMD machine with a bus interconnect architecture; the NASA/Goodyear MPP, a massively parallel SIMD machine with mesh interconnect architecture; the Connection Machine model CM-2, a massively parallel SIMD machine with hypercube interconnect architecture; and the Cray-2 supercomputer, a tightly coupled MIMD machine with direct connect interconnect architecture and is the latest Cray to be produced. These architectures are considered to be representative of the commercially available parallel computer architectures. The selected algorithm was implemented on these machines and the results are reported in chapter IV.

All of the architectures described in this chapter have one goal, to increase computational power by using replicated processing elements that are connected to and can communicate over some type of network. This goal results from the bounds on performance in traditional von Neumann architectures.

# Computer Architecture Classification Scheme

One of the oldest and still most widely used methods of classifying computer systems was developed by Flynn in 1966[19].

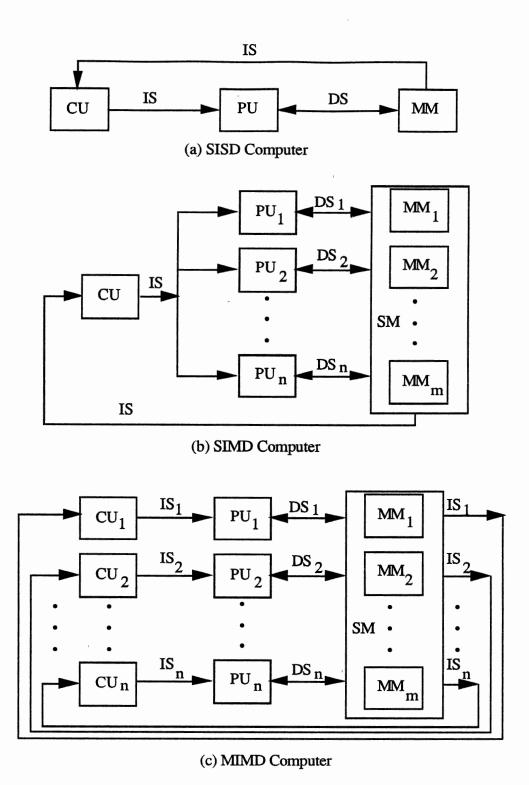

Figure 3.1 illustrates Flynn's classification which is based on program and data parallelism, i.e. the multiplicity of instruction streams and data streams in a computer system. In a conventional sequential computer, at any instant of time, there can be but a single command in the command register, and this command can effect an arithmetic or logical operation upon a single datum stored in the accumulator. Such a machine organization is termed single-instruction stream, single-data stream, or SISD [19]. Most SISD machines are pipelined and can have more than one functional unit under the supervision of one control unit.

In one widely used approach to parallelism, a multiplicity of concurrently operating processing elements is provided, where each processing element consists of an ALU and a memory unit. The arithmetic and memory units are interconnected to form a network or an array. The system contains only one program control unit which can activate any or all of the arithmetic units. Each active element of the array performs the same arithmetic or logic operation under command of the control unit. Each arithmetic element may be operating on different data in executing the instruction resident in the control unit. For this reason, this type of structure is termed single-instruction stream, multiple-data stream, or SIMD. SIMD machines are also called array processors [19].

Figure 3.1 Flynn's Classification of Computer Architectures

In the third approach, each processing element contains a control unit as well as an ALU and memory unit. The elements of the network can therefore function as full-fledged independent digital computers, and during any instruction cycle each processing element can carry out a different arithmetic or logic operation. For this reason systems of this type are termed multiple-instruction stream, multiple-data stream, or MIMD. Most multiprocessor systems and multiple computer systems can be classified in this category. MIMD machines are considered tightly coupled if there is a shared memory and the degree of interactions among the processors is high, otherwise, they are considered loosely coupled. Loosely coupled systems employ distributed memory with a low degree of interactions among the processors.

Since Flynn published his classification scheme, new parallel computer architectures have emerged which incorporated a variety of new architectural concepts. Currently, Flynn's classification scheme is still used but other classification schemes were developed mainly to augment Flynn's classification scheme making it more complete and accurate when used to classify new architectures. Some of the classification schemes are based on data sharing mechanism, synchronicity of operation, or granularity of computations [41]. Other schemes have emphasized a particular class of machines, like MIMD machines categorizing them as either switched systems or networks [42-43].

The aforementioned classification schemes of advanced computer architectures are only a few of the currently existing schemes. A variety of other classification schemes exist that adds to

the complexity of placing a given computer system within a definite class. The science of computer classification schemes is by no means complete and the necessity for a more clear and accurate scheme still exists.

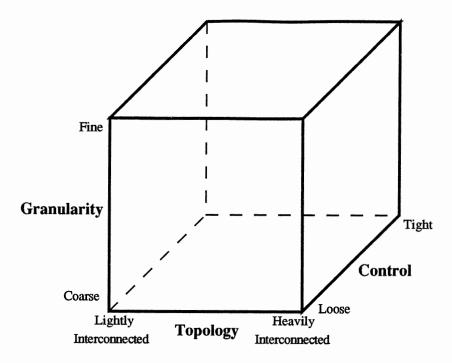

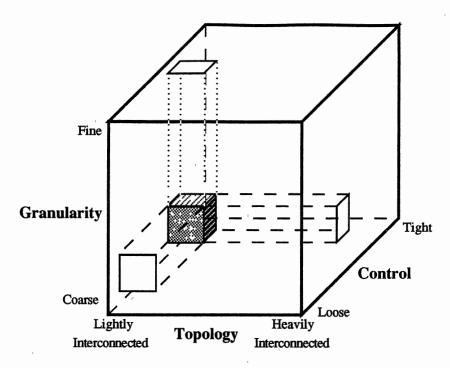

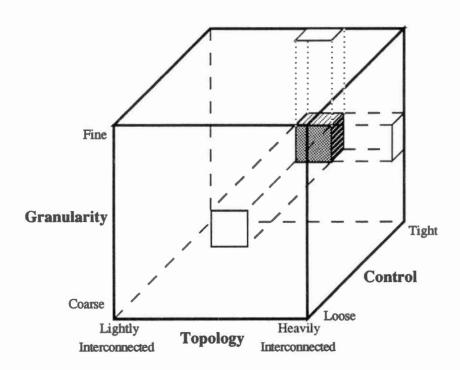

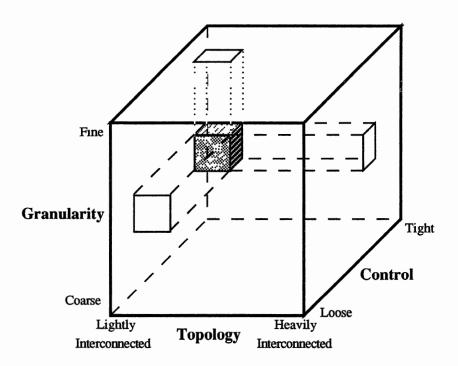

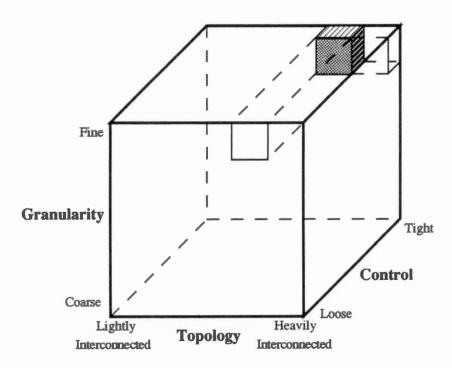

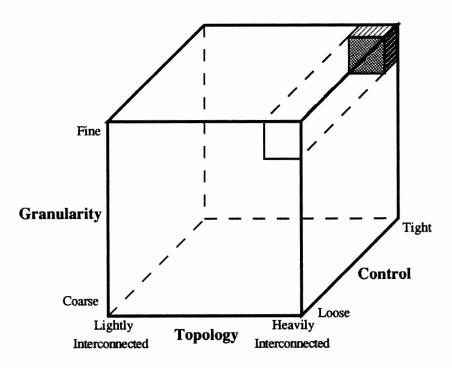

In this research, Flynn's classification is used along with a new classification scheme [21]. The classification scheme is based on three essential issues that must be considered for a parallel architecture: the granularity of the processing elements; the topology of the interconnections between processing elements; and the distribution of control across the processing elements.

Granularity refers to the power of each processing element in the architecture ranging from many single-bit processors to a few powerful general purpose ones. Topology refers to the pattern and density of the connections that exist between the processing elements. Control distribution is concerned with allocating tasks to the processing elements and synchronizing their interactions. Figure 3.2 illustrates the so called organizational space of parallel computer systems with these three variables as the axes.

In describing each computer architecture in this chapter, an attempt is made to place each system in relative perspective by illustrating their approximate position within the space. The criteria used in placing these systems are somewhat subjective and qualitative. The architectures described are so different in their structure and operations that it is virtually impossible to establish a one-to-one comparison of their features. It should be emphasized that the placing criteria largely depend on the way each machine is used in this research.

Figure 3.2 Organizational Space of Parallel Computer Systems

# Description of Selected Advanced Computer Systems

In this section a selected group of advanced computer architectures are described in detail. The hardware, software, and classification of each system are discussed in detail. The computer systems described here represent a variety of interesting architectures.

## The Heterogeneous Element Processor (HEP)

The Heterogeneous Element Processor (HEP) was first developed for the Army Ballistic Research Laboratories at Aberdeen by

Denelcor, Inc. The HEP is a large scale scientific parallel computer employing shared resource (tightly coupled) MIMD architecture. The processors used in the HEP are pipelined to support many concurrent processes, with each pipeline segment responsible for a different phase of instruction interpretation. Each processor has its own program memory, general purpose registers, and functional units; a number of these processors are connected to shared data memory modules by means of a very high speed pipelined packet switching network [19,44].

The extensive use of pipelining in conjunction with the shared resource idea result in a flexible and effective architecture. For example, the switch used to interconnect processors and memories is modular, and is designed to allow a given system to be expanded as needed. The increased memory access times that result from greater physical distances can be compensated for by using more processes in each processor because the switch is pipelined.

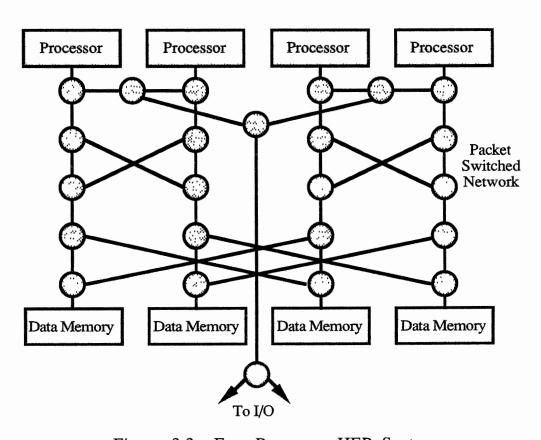

An overall block diagram of a typical HEP configuration is shown in Figure 3.3. The switch network shown has 28 nodes; it interconnects four processors, four data memory modules, and I/O processor and devices. Systems of this kind can be built to include as many as 16 processors and 128 data memory modules. Each processor performs 10 million instructions per second (MIPS), and the switch bandwidth is 10 million 64 bit words per second per network link. All instructions and data words in the HEP are 64 bits wide, although data references within each processor can access halfword, quarterword, and bytes [19,44].

Parallel processing and MIMD architecture, as implemented in HEP, allow up to 100 independent (or cooperating) instruction streams executing in parallel at any given time. In the HEP, these instructions are called processes, and 50 processes can be active at one time in a single processor. Each process can have its own unique data stream. With a number of processes executing concurrently, it is practical to separate an application problem into its component parts and execute the parts in parallel, with intermediate results passed between the cooperating processes as necessary [19,44,45].

Figure 3.3 Four-Processor HEP System

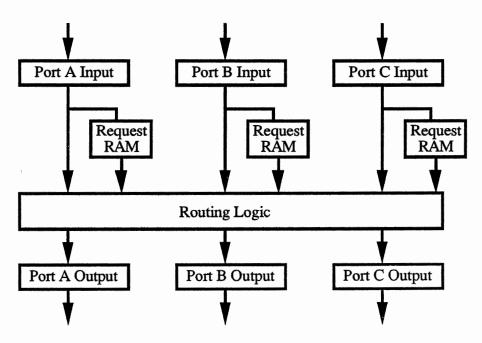

Figure 3.4 illustrates the routing control in the bidirectional 3-ported switch node. The switch is synchronous and modular employing packet switching. Each node is connected by three full duplex ports. Each node receives three message every 100ns and route them for optimal destination, i.e. with minimal delay. Each node has three routing tables, one per port; tables are indexed by destination address and contain the identification of the preferred port out of which the packet should be sent [19,44].

A unique feature of each switching node is it does not enqueue messages in case a conflict for a port occurs; instead, it routes all messages immediately to output ports. It is the responsibility of the neighbors of the node to make sure that incorrectly routed messages eventually reach their correct destinations.

Figure 3.4 Routing Control in the 3-ported Switch Node

The HEP main programming language is HEP/UPX FORTRAN 77 which incorporates two kinds of extensions to FORTRAN 77: CREATE and RESUME statements which are syntactically equivalent to CALL and RETURN statements in FORTRAN 77 but used here for the creation and termination of processes, and access states of the asynchronous variables for synchronization between processes. Synchronization is required for handling data dependencies among user-created instruction streams. The user is responsible for establishing proper synchronization within his program using asynchronous variables that can be set to an access state, namely full or empty. PURGE statement is used to unconditionally set the access state of a synchronous variable to empty. Reading and writing to a synchronous variable will set it empty and full respectively. HEP read and write instructions are controlled by these access states. By manipulating the access states, multiple instruction streams can be synchronized to access common memory locations [45].

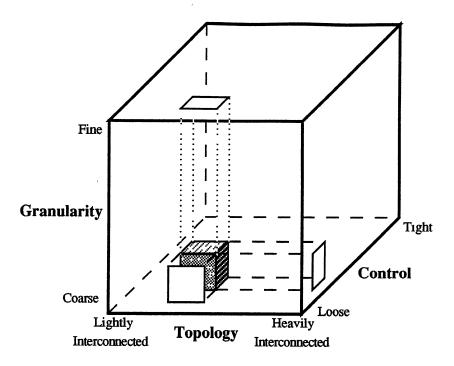

Figure 3.5 illustrates the position of the HEP system in the organizational space. The packet switched network connecting the processors and the resources is considered to be lightly interconnected while the granularity of the HEP is relatively coarse since each 64 bit processor is general purpose. The resources within the system are shared making the control of communications among resources relatively tight.

Figure 3.5 HEP Position in the Organizational Space

## The Cray X-MP/48

The Cray-1 computer was first delivered in 1976 to Los Alamos National Laboratory and since then it has been the industry standard in very high-speed computing. The success of the Cray-1 can be attributed to its innovative vector architecture, dense packaging, and advanced cooling technology [19-22,46].

The Cray-1 design employs many state-of-the-art architectural features such as: pipelining in memory access and function units, utilization of vector registers and operations chaining, concurrent execution of multiple functional units, interleaved memory, instruction cache and lookahead, and massive use of parallel logic to shorten the execution time of functional units.

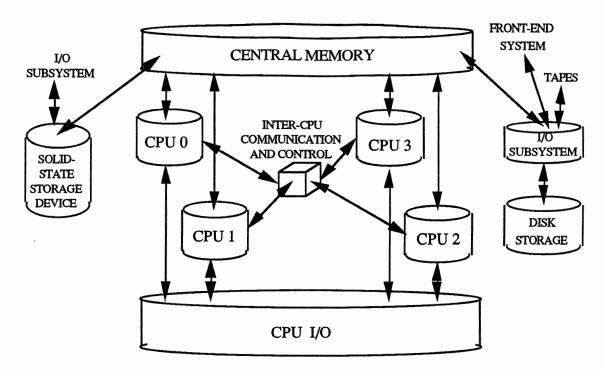

The Cray X-MP/48 or Experimental Multi-Processor is a multiprocessor extension of the Cray-1 that was completed in 1983. The Cray X-MP/48 is a tightly coupled MIMD supercomputer. It contains four Cray-1 like processors that share memory and I/O subsystems and has a clock cycle of about 9.5 nanoseconds (vs. 12.5 nanoseconds of Cray-1). Most often the four CPU's function independently, but their instruction streams can be synchronized.

Figure 3.6 illustrates the overall system of the X-MP/48.

Although built upon the basic architecture of the Cray-1, the X-MP/48 processor is totally redesigned. All processors share a central memory of 8 million (64-bit) words, organized in interleaved memory banks. All banks can be accessed independently and in parallel during each machine clock period. Each processor has four parallel memory ports (four times that of Cray-1) connected to the central memory: two for memory loads, one for memory stores, and one for independent I/O operations.

The multiport memory has built-in conflict resolution hardware to minimize access delay and to maintain the integrity of all memory references from different ports to the same bank at the same time. The multiport memory design, coupled with a shorter memory cycle time, provides a high performance memory organization with up to 16 times the memory bandwidth of a Cray-1. The improved memory bandwidth balances the multiple-pipelined computing power of the CPU and the data streaming ability of the memory. For each processor, this capability, coupled with reduced clock period, gives a performance speedup over the Cray-1 of up to 4 [19-22,46].

Figure 3.6 The Cray X-MP/48 Overall System Organization

The processors, which share the I/O ports, are controlled synchronously by a central clock. The scalar performance of each processor is improved through faster machine clock, shorter memory access, larger instruction buffers ( twice that of the Cray-1), multiple data paths, and multiple processors. The vector performance of each processor is improved through faster machine clock, parallel memory ports, and a hardware automatic flexible chaining feature. The machine allows simultaneous memory fetches, a sequence of computations, and memory store in a series of related vector operations.

The Cray X-MP/48, like the Cray-1, achieves low-level parallelism through vectorization. The Cray FORTRAN compiler (CFT)

analyzes innermost DO loops to detect vectorizable sequences and then generates code to take advantage of the processor organization. The vectorization performed by the compiler is automatic, providing increased performance without restructuring or handcoding. In addition, the Cray X-MP/48 can achieve high-level parallelism via multitasking. All of the processors can cooperate to solve a problem by running separate tasks in parallel.

Any required synchronization must be specified by the programmer via calls to the multitasking library. Multitasking requires careful consideration of the algorithm at hand and data dependencies that may exist. A variety of facilities are provided to support multitasking: compiler linkage protocols, utilities, memory management facilities, and multitasking synchronization routines.

A task is defined as a program unit capable of being independently assigned a processor. All tasks of a program share the same FORTRAN common memory area, but each task is allocated a private environment for its local variables. All programs consist initially of one task. Any task can create a number of other tasks. All tasks created as descendants of the initial task run logically in parallel, but actual parallel processing across the two processors depends on instantaneous machine loading and available resources. Hence, it is not possible to easily determine for a particular run whether separate tasks actually ran in parallel.

Finally, Figure 3.7 illustrates the position of the Cray X-MP/48 in the organizational space. Low-level parallelism is used in determining the approximate placement location. The processors are of fine granularity because they operate on multibit elements. The

topology is fairly heavily interconnected, because communication is performed at a low level and without the need for contention to access a communication path. The operation of the X-MP/48 is tightly coupled.

Figure 3.7 Cray Position in the Organizational Space

## The Intel iPSC/2 Hypercube

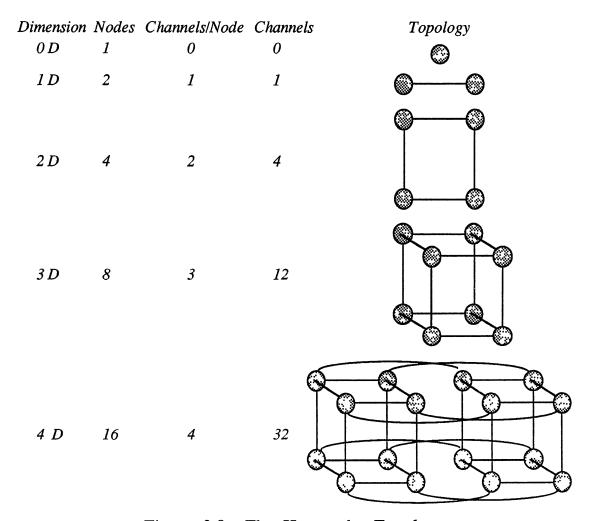

A cube is defined as a set of n processors, where n is a power of two, that are interconnected in such a way that the processors are located at the corners of a cube and the interconnections form the cube edges. There are several types of cubes, all variations on the basic architecture, called the Boolean n cube, or binary cube. Each of the n nodes contains log n connections to its neighbor nodes. Each node is numbered in such a way that there is one binary digit difference between any node and its log n neighbors.

Cubes with dimensions greater than three are generally called hypercubes. Higher dimension cubes/hypercubes are constructed using lower dimension cubes/hypercubes as shown in Figure 3.8.

Figure 3.8 The Hypercube Topology

The basic concept for the Intel iPSC computer was proposed by and developed at the California Institute of Technology, under a project called the Cosmic Cube [47]. The project was sponsored by the United States Department of Energy and DARPA. Under a license from Caltech, Intel developed its own hypercube-based architecture, utilizing existing Intel microcomputer and communication components.

The Intel iPSC/2 computer consists of a hypercube based architecture along with an associated host processor called the cube manager. The iPSC/2 used in this research is a five dimensional hypercube. The iPSC/2 is expandable to a seven dimensional hypercube. The connection scheme of the hypercube is robust since there are several different paths that exist between any two nodes in the cube [21].

Each iPSC/2 node contains a 32-bit microcomputer based on the Intel 80386 processor with a fast scalar floating-point unit. Each node has its own memory and therefore the iPSC/2 is considered to be loosely coupled MIMD machine.

Nodes communicate with other nodes by sending and receiving messages. Message passing is the only means available for internode communication and synchronization, since the iPSC/2 has no shared memory. A Direct-Connect routing module is present in each node for high-speed message passing within the system's hypercube communication network. Each routing module provides an eighth channel for high-speed external communication (only seven are needed to connect up to 128 nodes). Messages on the iPSC/2 can either be synchronous or asynchronous. A call to the synchronous

message passing routines blocks until the message is sent or received before returning and allowing program execution to continue. On the other hand, a call to the asynchronous message passing routines returns immediately and does not block until the message is sent or received. The user has complete control over message passing using FORTRAN or C language extensions.

Figure 3.9 places the iPSC/2 hypercube architecture in the organizational space. The node processors are capable of performing a full range of operations since they incorporate general-purpose 32-bit microprocessors. For this reason, the iPSC/2 is considered to be fairly coarse grained. Since the complexity of the interconnection at each node is a maximum of five channels (for the 5-dimensional hypercube), and the communication between nodes does not have to be synchronized, the topology of the hypercube is of medium interconnection complexity. The iPSC/2 is an MIMD machine with each node having its own local instruction stream and communication is locally controlled making the overall system loosely coupled.

Figure 3.9 Hypercube Position in the Organizational Space

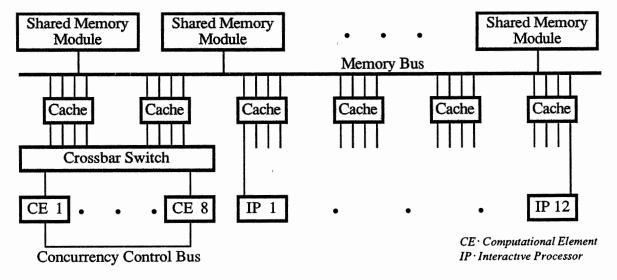

### The Alliant FX/8

The Alliant FX/8 was designed to exploit parallelism found in scientific programs automatically. The intent was to allow parallel processing on existing FORTRAN programs with minimal or no changes to the source code. Figure 3.10 illustrates the hardware architecture of the Alliant FX/8. It consists of eight processors called Computational Elements (CEs), and 12 Interactive Processors (IPs). A common memory bus is employed for communication among resources. The CEs are connected via a crossbar switch to the cache modules attached to the memory bus. All access by the CEs and IPs to the bus occurs through cache memory modules. The CEs are also

connected directly to each other via a concurrency control bus. The Alliant FX/8 is a tightly coupled MIMD machine.

The CE is the computational building block of the Alliant FX/8 system. Each CE is a microprogrammed pipelined processor (compatible with MC68000 architecture) with integrated floating point and vector instruction sets. In general, the CEs are used to perform computation-intensive processes that can benefit from vectorization or loop-level concurrency, whereas the IPs are used to perform interactive processes and handle I/O between the memory and peripherals. The CEs are referred to as the computational complex and can be devoted to the execution of a single program.

Figure 3.10 The Architecture of the Alliant FX/8

FORTRAN, C, and Pascal are supported on the FX/8 but only the FX/FORTRAN compiler provides optimization for concurrency and vectorization. Concurrency refers to the concurrent execution of loops and array operations by more than one CE. Vector operations are distributed across the CEs for concurrent execution in the same way as scalar operations.

When the FX/FORTRAN compiler recognizes an opportunity for concurrency, it generates concurrent code only as long as it can guarantee that this will not change the outcome of the program. In most cases, the compiler is very conservative in this regard. It bases its decision on the type of statements within a loop and the way variables are used, since the latter often affects the degree to which the iterations of the loop can be overlapped.

Concurrency is applied to DO loops by executing the different iterations on different CEs. Since there are eight processors, up to eight iterations can be active at one time. If necessary, the compiler inserts synchronization points into the object code to ensure that variables within a loop are updated and accessed in the correct order and to guarantee that the program statements following a loop do not execute until all iterations of the loop are finished.

Figure 3.11 illustrates the position of the Alliant FX/8 in the organizational space. The computer is a tightly coupled MIMD machine. The CEs are powerful processors that employ pipelining and vectorization suggesting that the FX/8 is of medium granularity. The interconnection between the CEs is simply a bus (concurrency bus). The CEs are connected via a crossbar switch to the cache memory modules which in turn connected to the shared memory via

a bus. For these reasons, the FX/8 is considered to be lightly connected. The control is fairly tight since a shared memory is used.

Figure 3.11 Alliant Position in the Organizational Space

### The Massively Parallel Processor (MPP)

Among the experimental machines successfully built is the massively parallel processor (MPP) which was designed to process satellite imagery at high rates. In 1971, NASA Goddard Flight Center in Greenbelt,Md., initiated research for a high speed computer to process the data generated by orbital imaging sensors. Data rates of

1013 bits/day is expected to result in 109-1010 operations/sec workload. Designed and built for \$6.7 million by the Goodyear Aerospace Corp. in Akron, Ohio, the MPP was delivered to NASA in May 1983.

One of MPP's first tests involved analyzing data from the "thematic mapper" aboard Landsat 4. By studying the million or so pixels making up a typical image, the MPP automatically finds out whether each spot represents water or land, forest or field, stream or street - all in 20 seconds. A conventional computer would take hours to analyze the same picture and produce a similar classification scheme.

## The MPP Architecture [48]

The MPP owes its speed to the unusual way in which the machine's parts are organized. Its network of 16384 simple processors allows a problem to be divided up so that each processor performs the same operation on different pieces of data at the same time (SIMD architecture).

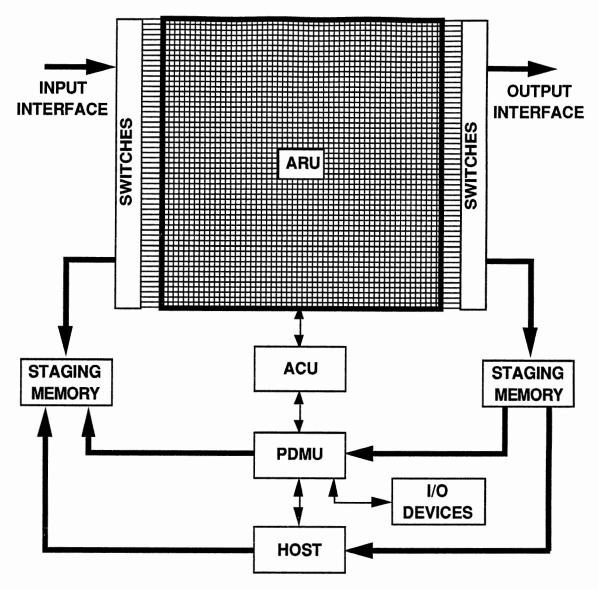

Figure 3.12 depicts the overall system block diagram. There are five main subsystems: The array unit (ARU), the array control unit (ACU), the program and data management unit (PDMU), the staging memories (SM), and the host computer.

Figure 3.12 Overall Block Diagram of the MPP

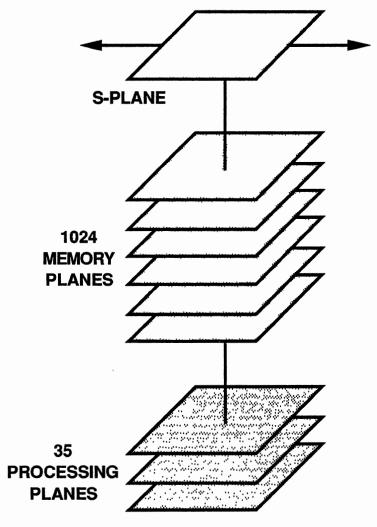

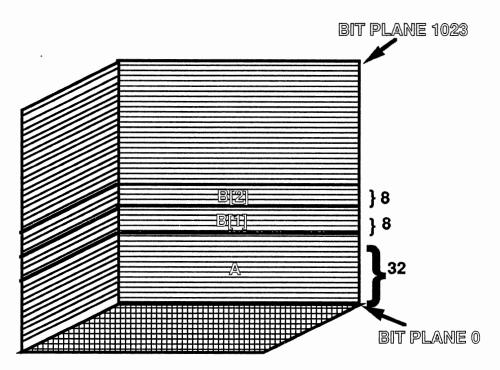

The Array Unit. The ARU of the MPP is organized with a number of 16384 -element planes to handle the two-dimensional data processing at high speed. Each plane is a square with 128 rows and 128 columns. Figure 3.13 shows 1 column of the ARU. The ARU contains one S-plane (used to handle data input and output for the

ARU), 1024 memory planes, and 35 processing planes for a total of 1060 planes. Each plane also has 4 spare columns to bypass faulty hardware.

Figure 3.13 The ARU

Instructions operate on a whole plane of data in parallel. The ARU can treat data of arbitrary precision since the processing is bit-serial. Black-white images are stored and processed as arrays of single-bit pixels, images with 256 grey levels are stored and processed as arrays of 8-bit pixels.

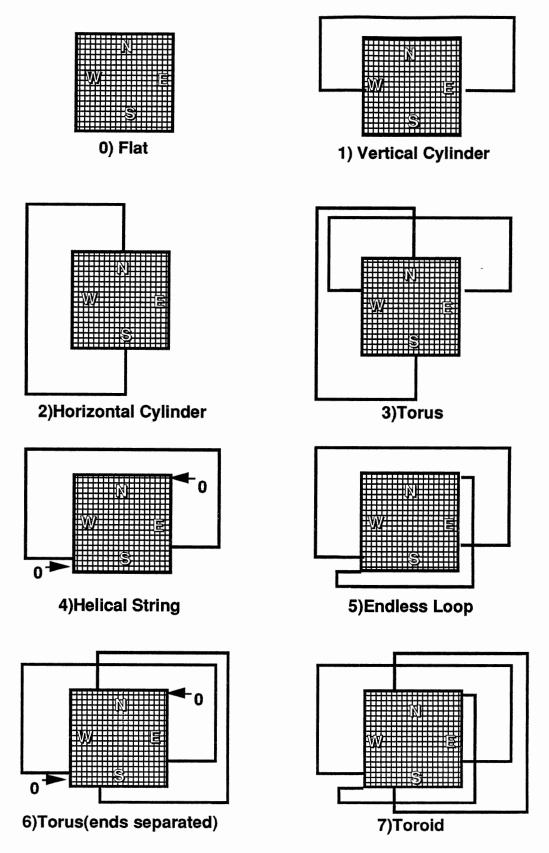

Each plane is organized in a mesh with nearest neighbor communication between the elements in that plane. This architecture facilitates data accessability and is easy to implement in hardware. The edge connectivity is programmable offering the user eight different topologies. Figure 3.14 illustrates these topologies. For the East-West edges there are 4 possible options: open, cylindrical, open spiral, or closed spiral. For the North-South edges there are 2 possible options: open or connected.

Programmability is achieved using the topology register in the ACU. Note that topologies 4-7 convert the two-dimensional ARU into one-dimensional structure that can be used for one-dimensional signal processing problems.

Processing elements in the ARU are designed with two-row by four-column custom made VLSI chips (HCMOS technology). The processing element array has 128 rows and 132 columns that are divided into 33 groups, each of which consists of 128 rows by 4 columns. Each of the 33 groups has an independent group-disable control line from the ACU that is activated if a faulty processing element is detected. Arbitrary disable is used if no fault is detected. The programmer does not need to alter the program when the disabled group is changed since logical addresses are used.

Figure 3.14 Topologies Available on the MPP's ARU

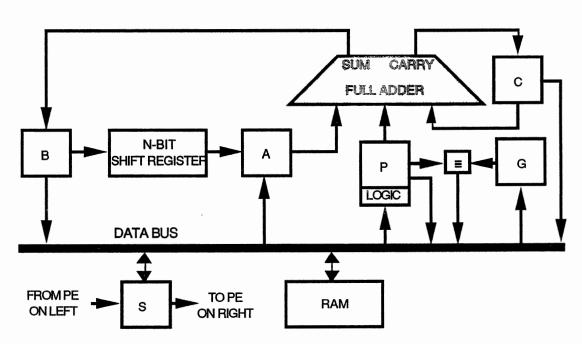

Figure 3.15 shows one processing element (PE) in the ARU. The PE has six 1-bit registers (A,B,C,G,P,and S), a planar shift register with a programmable length (2,6,10,14,18,23,26,or 30), RAM, data bus, full adder, and some logic circuits. The S-register is part of the S-plane that handles data input and output for the ARU. On input, the S-plane accumulates a plane of data, column by column and then transfers the data plane to a memory plane. On output, the S-plane receives the contents of a memory plane and then transfers the plane out column by column. Input and output can be handled simultaneously.

Figure 3.15 The Processing Element

The A-register is part of the A-plane that receives the output of the planar shift register. It can be considered to be a one-plane extension to the depth of the planar shift register. The B-plane is the sum plane in arithmetic operations, while the C-plane is the carry plane. The G-plane is used to mask activity in the other processing planes, while the P-plane is used for logic and routing operations.

The RAM stores 1024 bits per PE with addresses in the range 0 to 1023. The ACU generates 16-bit addresses so that ARU storage can be expanded to 65536 bits per PE. Memory faults are detected using parity check that sets an error flip-flop associated with the 2 by 4 subarray.

The S-plane and the processing planes are implemented with 2112 custom VLSI circuits. The memory planes are implemented with 4752 standard bipolar RAM integrated circuits- each RAM circuit contains 4 data bits or 4 parity bits of all 1024 memory planes. Twenty four VLSI circuits and 54 RAM circuits are packaged on one printed-circuit board to make up a 16 row by 12 column section of the ARU planes. The 128 row by 132 column ARU requires 88 printed-circuit boards. Another 8-boards are used for the topology switches around the edges of the P-plane and to distribute the control signals from the ACU.

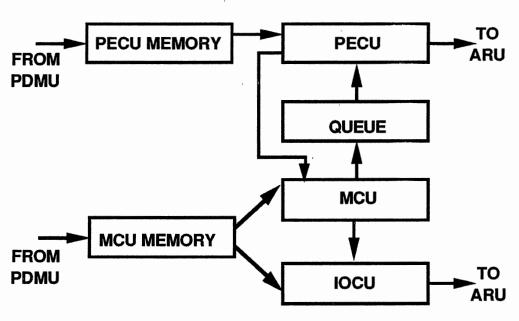

The Array Control Unit. The ACU controls the operations in the ARU and performs the arithmetic on any scalars required to support operations on data arrays in the ARU. Figure 3.16 shows a block diagram of the ARU that consists of: the processing element control

unit (PECU), the input/output control unit (IOCU), the main control unit(MCU), a queue, and memory for both the PECU and the MCU.

Figure 3.16 The Array Control Unit

The PECU controls operations in the processing planes of the ARU. It generates all ARU instructions except those pertaining to the S-register. It executes microcoded routines stored in its program memory to perform all array operations required by application programs. The PECU contains 8 index registers, a 64 bit common register for scalar data, a topology register, a program counter, a subroutine stack, and an instruction register.

The IOCU controls the shifting of I/O data through the ARU S-registers as well as the transfer of I/O data between the S-registers

and the ARU memory. It executes I/O channel control programs stored in the MCU program memory.

The MCU executes the application program stored in its program memory. It performs the scalar arithmetic operations required, calls the PECU for all array logic and arithmetic operations. Both sets of calls are queued to await execution while the MCU moves on to generate other calls.

The queue holds calls to the array processing routines until they are executed by the PECU. A call enters the queue when inserted by the MCU and remains there until the PECU has executed all previously called routines, then the PECU jumps to the called routine. Up to 16 calls can be held in the queue at one time.

The Program and Data Management Unit. The PDMU is a DEC PDP11/34A minicomputer. It controls the overall flow of programmed data in the system and it has the RSX-11M real time multiprogramming operating system. The PDMU executes the program development software package written in FORTRAN. This package includes the main assembler, the PE control assembler, a linker, and a control and debug module.