|                         | GaN-based LSK demodulators for wireless data receivers in high-<br>temperature applications                                                                                                                                                                                               |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Auteurs:<br>Authors:    | Ahmad Hassan, Mohamed Ali, Yvon Savaria, & Mohamad Sawan                                                                                                                                                                                                                                  |

| Date:                   | 2019                                                                                                                                                                                                                                                                                      |

| Type:                   | Article de revue / Article                                                                                                                                                                                                                                                                |

| Référence:<br>Citation: | Hassan, A., Ali, M., Savaria, Y., & Sawan, M. (2019). GaN-based LSK demodulators for wireless data receivers in high-temperature applications. Microelectronics Journal, 84, 129-135. <a href="https://doi.org/10.1016/j.mejo.2019.01.006">https://doi.org/10.1016/j.mejo.2019.01.006</a> |

# Document en libre accès dans PolyPublie Open Access document in PolyPublie

| URL de PolyPublie:<br>PolyPublie URL:      | https://publications.polymtl.ca/41945/                                                 |

|--------------------------------------------|----------------------------------------------------------------------------------------|

| Version:                                   | Version finale avant publication / Accepted version<br>Révisé par les pairs / Refereed |

| Conditions d'utilisation:<br>Terms of Use: | CC BY-NC-ND                                                                            |

# Document publié chez l'éditeur officiel Document issued by the official publisher

| <b>Titre de la revue:</b> Journal Title: | Microelectronics Journal (vol. 84)         |

|------------------------------------------|--------------------------------------------|

| <b>Maison d'édition:</b><br>Publisher:   | Elsevier                                   |

| <b>URL officiel:</b><br>Official URL:    | https://doi.org/10.1016/j.mejo.2019.01.006 |

| <b>Mention légale:</b><br>Legal notice:  |                                            |

## GaN-Based LSK Demodulators for Wireless Data Receivers in High-Temperature Applications

Ahmad Hassan, Student member, IEEE, Mohamed Ali, Yvon Savaria, Fellow, IEEE, and Mohamad Sawan, Fellow, IEEE

Abstract— GaN (gallium nitride)-based fully-integrated demodulators are presented. These modules, intended for wireless applications, target high-temperature (HT) environments including monitoring devices in aerospace. The presented demodulators are dedicated to recover Load-shift keying signals modulating a low carrier frequency to maximize power transfer efficiency and increase data transmission rate through metallic barriers. Logic gates are implemented and successfully tested at HT exceeding 400°C. Proposed demodulators are built from half and full bridge rectifiers, comparators, voltage references and inverters, and operate at a minimum carrier frequency (fc) of 50 kHz. A demodulator based on a digital topology is proposed to cover MHz range fc. A complementary ± 14V supply voltage is required to operate the circuits. Reported post-layout simulation results validate the functionality and performance offered by the proposed demodulators over the 25°C to 400°C temperature range. Also, a complete chip layout has been done, where the introduced demodulators occupy 10 mm<sup>2</sup> of a GaN die area.

Index Terms—High-temperature applications, wireless data transmission, GaN HEMT, integrated circuits, demodulation system.

#### I. INTRODUCTION

MPLEMENTING electronics that can operate in harsh environments, including high temperature (HT), is needed by many industries such as downhole oil and gas, aerospace and automotive. Cooling solutions for conventional electronics are not always possible and may have negative impact on system reliability and cost. For instance, during well logging, a failed electronics assembly on a drill string operating at deep underground level can take more than a day to retrieve and replace. In parallel, the cost for operating a complex deep-water offshore is around \$1M per day [1]. Further, influential corporations like AIRBUS, SAFRAN, and THALES are seeking alternative microelectronic technologies aiming for complete wirelessly controlled systems that can harvest power from the surrounding HT environment, exchange data through wireless links under HT conditions and be integrated in critical

This work was supported in part by the Natural Sciences and Engineering Research Council of Canada (STPGP463394), CMC Microsystems, National Research Council of Canada (NRC), SAFRAN and AIRBUS DEFENCE AND SPACE.

A. Hassan, M. Ali (is in leave of absence from Microelectronics Department, Electronics Research Institute, Cairo 12622, Egypt), Y. Savaria, and M. Sawan are with Department of Electrical Engineering, Polytechnique Montréal, QC H3T 1J4, Canada (e-mail: ahmad.hassan@polymtl.ca).

high-risk areas.

Among the available semiconductors dedicated for HT applications, wide bandgap (WBG) semiconductors are the main candidates in the foreseeable future to overcome the fundamental physical limits of the other electronics such as silicon on insulator (SOI), gallium arsenide (GaAs) and silicon germanium (SiGe), which are serving a relatively short range of temperature not exceeding 300°C and for limited operation time [2-4]. Silicon carbide (SiC) and gallium nitride (GaN) are the best-known WBG devices that offer attractive features suitable for HT conditions. These features include wide bandgap (3eV), high-drift saturation velocity, high-thermal conductivity, and low-intrinsic carrier concentration [5].

Several studies have been done recently for SiC semiconductors at HT [6-9]. However, the HT measurements are performed only for devices [7] and circuits [8]. Even in [9], the proposed system represents only the RF transmitter part, where the receiver is a Tektronix RSA3303B real-time spectrum analyzer. In addition, no commercially available SiC integrated devices and circuits operating at temperature higher than 300°C were found [10]. Moreover, the direct temperature dependence of carrier concentration, due to the bulk nature of the active region in SiC devices, is considered as a common shortcoming [11] in addition to the crystal dislocation disorders which degrade junction leakage, particularly at the highest temperatures.

III-Nitride and primarily GaN technologies exhibit substantial performance improvement over SiC semiconductor with respect to response speed and operating temperature limits [12]. In addition, the temperature stability of electron concentration in the HEMT channel makes GaN devices more stable with respect to temperature. Despite considerable efforts to develop GaN devices dedicated to HT applications [12-13], few researches are directed toward the development of integrated microelectronic circuits and systems based on GaN devices. Nowadays, the reported works show the implementation of simple circuits like inverter, comparator, ring oscillator, and one stage differential amplifier [11,14-15].

In our group, the HT characterization of AlGaN/GaN HEMT devices was successfully performed over a 25°C to 400°C temperature range as a first step to ensure the ability of using them in circuits and systems design dedicated to HT applications. All information regarding the fabrication process,

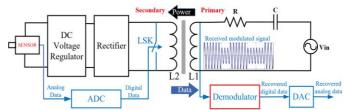

Fig. 1. Block diagram of the proposed power and data transmission system.

materials of the characterized GaN devices and performed HT characterizations were reported in [16]. This GaN-based epitaxial layer Heterojunction FET technology is provided by the Canadian Photonics Fabrication Center of the Canadian National Research Council (NRC). This technology called (GaN500) offers 500nm gate length transistors fabricated on 3-inch SiC wafers. The SiC substrate offers high-thermal conductivity and low-lattice mismatch to the GaN layer, which is compatible with HT applications. In addition to the active devices, the available technology allows the integration of some passive components (resistors, inductors, and capacitors).

In this paper, we present the design and implementation of three complete demodulation systems based on GaN500 technology. These proposed circuits demodulate LSK modulated signals for wireless monitoring applications operating in HT environment. We provide in Section II the main considerations about the adopted GaN technology and circuit design, in addition to the circuit level validation at 400°C of GaN-based digital circuits. The building blocks, circuits and functionality of the proposed demodulators are discussed in section III, along with the impact of HT on them. Conclusions are the subject of section IV where our contributions are summarized.

### II. DESIGN CONSIDERATIONS AND DIGITAL CIRCUITS VALIDATION

Figure 1 shows a wireless power and data transmission system based on an inductive link. The power transfer path provides the supply voltage to a sensing device (pressure, temperature) located in a harsh environment. The data transmission path is based on the LSK modulation technique to reduce the complexity of the whole wireless power and data transmission system that operates through a single inductive coupling interface. In the transmitting side (secondary), the analog signal of the sensor is converted into digital data modulating the signal through a controllable switch.

The demodulator, located on the receiving side (primary), detects the received modulated signal and recovers the expected digital data. The modulated signal (Fig. 1) consists of two different amplitude voltage levels; high-level (data-on) and low-level (data-off). The voltage difference between data-on and data-off levels is strongly recommended to be as small as possible to maintain the highest power transfer efficiency during the data transmission process.

#### A. Design and technology considerations

The harsh environment condition of the targeted industrial applications is not only the high-temperature but also the

metallic barrier between primary and secondary coils. That metallic barrier is an enclosure encapsulating hot high pressure gases. This metallic barrier (hard steel that can sustain high pressure and high temperature) obviously has fairly high-electrical conductivity and high-magnetic permeability that induce high Eddy current losses and form a shielding zone for inductive fields, respectively. Therefore, the carrier frequency of the applied power signal should be relatively low to obtain enough power transfer efficiency while being sufficiently high to allow an adequate data transfer rate [17].

To endure the HT environment, a GaN500 technology is adopted to build the proposed demodulation system. In this implementation technology transistors are normally-on and they operate as depletion mode devices with a threshold voltage of -4V. This imposes significant design constraints, in particular when the system specifications include limited power budget, and small-system geometry. Thus, it becomes a serious challenge to design a complete demodulation system based on this technology.

Considering the specifications and system constraints we based the circuit design on WBG normally-on devices [9, 15]. Then, a minimum number of transistors was used to obtain the desired functions and for better miniaturization of the complete system. Since GaN500 cells require VGS= -5V to completely switch off the established channel, a negative input logic level is needed to drive the circuits which leads to the necessity of matching the input-output controlling signals. Level shifters are added to solve the incompatibility between the input and output levels and three supply voltage levels are used (VDD = +14V, VSS = -14V, and Gnd).

Despite the promising performance of GaN500 devices at HT, there is still an effective impact of environmental temperature on the active devices [16] and passive components (resistors). For this reason, the proposed design must consider the temperature induced parametric variations of the available components (active and passive) over the expected temperature range that spans from 25°C to 400°C. The Keysight Advanced Design System (ADS) kit was used to perform the design and simulation of proposed system where the transistor model (Angelov model configured with several parameters not visible to the user) includes the effects of self-heating and external applied temperature giving the opportunity to simulate the temperature impact on the circuits and system behavior. Similarly, based on the provided Thermal Coefficient of Resistance (TCR) of the integrated resistors (200 ppm/°C), equation (1) describes the change of resistance values over the temperature range

$$R_t = R_0 (1 + 2 \text{ T} 10^{-4}) \tag{1}$$

where  $R_t$  is the actual resistance,  $R_0$  is the resistance value at room temperature and T is the actual temperature ( ${}^{\circ}C$ ).

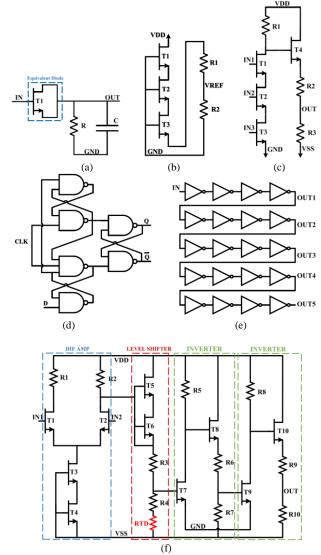

#### B. Digital circuits validation at HT

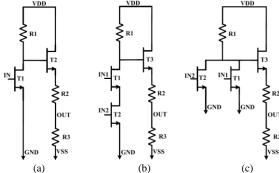

To validate the concept, several GaN500-based logic gates were implemented and tested at several temperatures between  $25^{\circ}$ C and  $400^{\circ}$ C. The schematics of the implemented logic gates

Fig. 2. Circuits of digital logic gates: (a) NOT, (b) NAND, and (c) NOR.

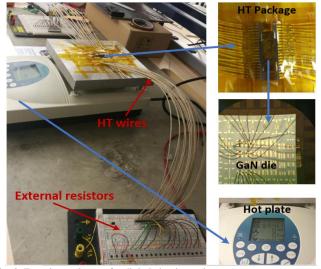

Fig. 3. Experimental setup for digital circuits testing.

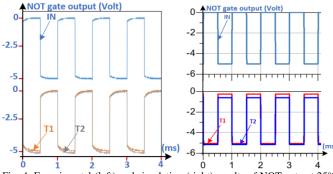

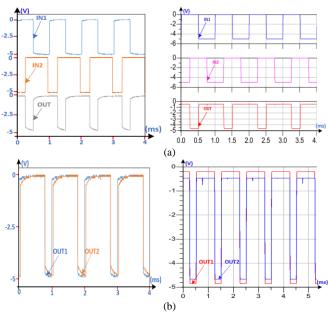

Fig. 4. Experimental (left) and simulation (right) results of NOT gate at 25  $^{\circ}$ C (T1) and 400  $^{\circ}$ C (T2).

are shown in Fig. 2. The experimental setup is depicted in Fig. 3 where the GaN500 devices are wire-bonded to the pads of a ceramic HT package and HT wires are used to connect the package to the measurement devices.

It is important to note that the GaN die that was used in those experiments comprises independent devices without resistors. Thus, external resistors were added to the test setup. Consequently, to perform a proper comparison between the experimental and simulation results, the temperature impact is applied only on GaN devices of the simulation kit, keeping the resistors at constant values. The measurements and simulation results are almost equal, thus showing the robustness and functionality over the wide temperature range tested for NOT,

Fig. 5. Experimental (left) and simulation (right) results of NAND gate: (a) at  $400^{\circ}$ C, (b) at  $25^{\circ}$ C (OUT1) and  $400^{\circ}$ C (OUT2).

Fig. 6. Experimental (left) and simulation (right) results of NOR gate at: (a)  $400^{\circ}$ C, (b)  $25^{\circ}$ C (OUT1) and  $400^{\circ}$ C (OUT2)).

TABLE I

GAN-BASED CIRCUITS FOR HT APPLICATIONS

|            | This work | [11]      | [14]      | [15]       |

|------------|-----------|-----------|-----------|------------|

| Circuit    | NOT,      | Dif. Amp. | NOT gate  | NOT gate   |

|            | NAND and  | and NOT   |           | and ring   |

|            | NOR gates | gate      |           | oscillator |

| Tech.      | AlGaN/GaN | AlInN/GaN | AlGaN/GaN | AlGaN/GaN  |

| Foundry    | NRC       | Inhouse   | Inhouse   | Inhouse    |

| Temp. (°C) | 400°C     | 500°C     | 300°C     | 256°C      |

NAND and NOR gates as shown in Figs. 4, 5 and 6 respectively.

Table I summarizes features of the implemented circuits based on GaN technology targeting HT applications, and it compares them with the only three published works that were found [11, 14-15]. To the best of our knowledge, none of these teams have reported system level design or implementation.

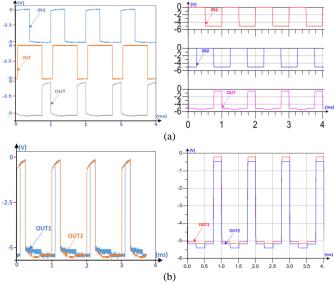

Fig. 7. Block diagrams of the proposed demodulators: (a) Half-bridge rectifier, (b) Full-bridge rectifier, and (c) Digital based.

Fig. 8. Building circuits: (a) Half bridge rectifier, (b) Voltage reference, (c) NAND (3IN), (d) D-Flip Flop, (e) Delay, and (f) Comparator.

#### III. PROPOSED DEMODULATION SYSTEMS

#### A. Building blocks and functionality

Figure 7 presents the block diagram of the three proposed demodulation systems. The first demodulator is presented in

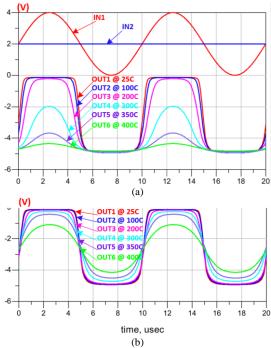

Fig. 9. Comparator simulations at different temperatures: (a) Without adaptation, and (b) With adaptation.

Fig. 7(a) where the modulated signal (IN) is applied to a half-bridge rectifier (HBR) followed by a bank of RC circuits that play the role of envelope detector and that shape the modulating signal (M1). The latter is compared to a reference voltage (VREF=2.6V) using a comparator block. Three inverters (INV1, INV2 and INV3) are used to sharpen the comparator output signal and to generate the initial digital data (Q) along with its complementary signal (QB). Q and QB are needed by a DAC block (Fig. 1) to recover the initial analog signal. The building circuit schematics of the half bridge rectifier (HBR) demodulator are provided in Fig. 2(b) (2IN-NAND) and Fig. 8(a) (half bridge rectifier), (b) (voltage reference) and (f) (comparator).

The minimum carrier frequency that could be handled by the HBR demodulation system is 60 kHz. Lower than this limit, the difference between data-on and data-off signals provided by the HBR could not be sensed by the comparator. To go beyond this limit, a full bridge rectifier (FBR) is utilized instead of the HBR keeping the remaining building circuits without any change (Fig. 7(b)). The FBR demodulation system operated properly at a carrier frequency as low as 50 kHz.

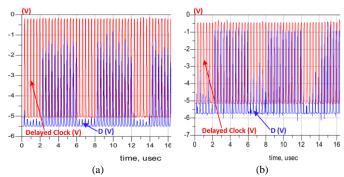

Another demodulator is fully based on digital circuits and is proposed for high carrier frequency applications (in the range of MHz). The block diagram of this digital demodulator is presented in Fig. 7(c). The novel idea of this demodulator is to use an inverter (INV4) which is carefully designed to detect only the data-on (high-amplitude voltage) and discard the data-off (low-amplitude voltage) of modulated signal. On the other hand, INV5 is used to switch continuously in both data-on and data-off cases to generate the clock signal of D-Flip Flop. This clock signal is delayed by the DELAY block to ensure matching with the detected data signal. For lower carrier frequency operation (range of kHz), a longer delay should be designed.

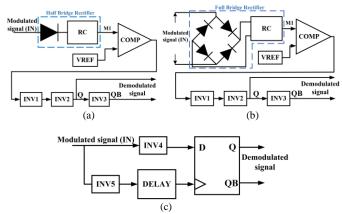

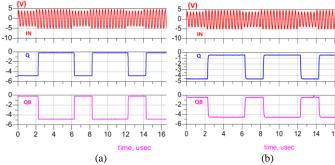

Fig. 10. HBR demodulator simulation results at: (a)  $25^{\rm o}{\rm C},$  and (b)  $400^{\rm o}{\rm C}.$

Figure 2(a) (2IN-NAND) combined with Fig. 8(d) (D-Flip Flop) and (e) (delay) shows the building circuit schematics of the digital demodulator. A long chain of inverters (20 stages) is utilized to design the DELAY block (Fig. 8(e)) and the D-Flip Flop design is based on five 2-input and one 3-input NAND logic gates, where the corresponding schematic design is shown in Fig. 2(b) and Fig. 8(c), respectively.

#### B. Simulation results

During the investigation of HT impact on the performance of each building circuit, we noticed that the comparator is the block most affected by HT operation, much more than the other circuits. As can be seen in Fig. 9(a), the comparator output fails dramatically after 250°C. The circuit analysis shows the sensitivity of the comparator performance with the value of R4 (Fig. 8(f)). A resistive temperature detector (RTD) [9] is added in series to R4 to compensate the temperature impact. Due to its high-temperature coefficient and very linear temperature response from room temperature up to 500°C, the RTD made of platinum is an ideal candidate for our case. The new performance of the adapted comparator is presented in Fig. 9(b).

To validate the three proposed demodulators, a modulated signal (IN) is applied to retrieve the demodulated signal (Q) and its complement (QB). The system analysis shows that the minimum amplitude of the data-on signal is +-5V. This means that, to reach a higher power transfer efficiency, the amplitude of the data-on signal could be increased more than +-5V as

Fig. 11: Digital demodulator simulation results at: (a) 25°C, and (b) 400°C.

Fig. 12: Delayed clock and detected data intersection at: (a) 25°C, and (b) 400°C.

much as needed until reaching the required power transfer efficiency, without applying any change on the proposed demodulators.

In parallel, the maximum amplitude of the data-off signal is +-4V and it could be less than that, but it would reduce the power transfer efficiency. Therefore, the modulated signal (IN) is selected with high-amplitude of +-5V (minimum data-on) and low-amplitude of +-4V (maximum data-off) to show the performance of modulators at the critical case. Consequently, a 1.0V amplitude difference (20% of the maximum amplitude) reached between the high-amplitude (data-on) and low-amplitude (data-of) of the modulated signal (IN) with the proposed demodulators.

Figure 10(a) presents the transient performance of the HBR demodulator at 25°C. To ensure the reliability of the proposed demodulation system, simulations were repeated after applying the HT GaN500 model (Angelov model) and resistor values (using equation 1). At carrier frequency 60kHz, the simulation results at 400°C shown in Fig. 10(b) are compatible with the results at 25°C in Fig. 10(a) except for the ripples in the recovered signal (Q). These ripples could be easily solved by adding a small capacitor (C=10pF) at the output of INV2. Similar simulation results were obtained with the FBR demodulation system at a carrier frequency of 50kHz. In parallel, the simulation results of the digital demodulator with carrier frequency of 4MHz are presented at 25°C and 400°C in Figs. 11(a) and (b) respectively, where an excellent stability is shown. The detected data (D) of inverter (INV4) is presented in Fig. 12(a) and (b) at 25°C and 400°C respectively, along with the delayed clock signal generated from inverter (INV5).

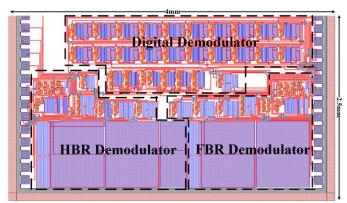

A complete chip layout (Fig. 13) for the three proposed demodulators was performed. The overall area of the chip is

Fig. 13: Chip layout view of the proposed data transmission systems.

TABLE II

POWER CONSUMPTION AND AREA OF PROPOSED DEMODULATORS

| Demodulator | Frequency<br>(MHz) | Power (W) @<br>25°C/400°C | Area<br>(mm²) |

|-------------|--------------------|---------------------------|---------------|

| HBR         | >0.06              | 0.77/0.42                 | 2.24          |

| FBR         | >0.05              | 0.84/0.46                 | 1.9           |

| Digital     | >1                 | 4.3/4                     | 2             |

4.0mm x 2.5mm. Table II summarizes the operating frequency, power consumption and occupied area of each module. The high-power consumption and large area of the digital demodulator are due to the Delay block which should be optimized in future work. As shown in Table II, the HT has a positive impact on power consumption especially for HBR and FBR demodulators with power reduction of more than 40% at 400°C.

#### IV. CONCLUSION AND FUTURE WORK

The design and implementation of three different demodulators based on GaN500 devices are described. The introduced building blocks are designed to fit into wireless power and data transmission systems based on the LSK modulation technique targeting harsh environments and high temperature application HT environment. The design considerations of the proposed modules are discussed considering the specific requirements of the targeted applications and the limitations of adopted technology. Circuit validation of GaN-based logic gates was performed at 400°C. Simulation results of proposed systems were performed to ensure their functionality over wide temperature range between 25°C and 400°C. Future work includes circuit design optimization to reduce the power consumption.

#### REFERENCES

- Watson, J., & Castro, G. (2012). High-temperature electronics pose design and reliability challenges. Analog Dialogue, 46(2), 3-9.

- [2] Thornton, T. J., Lepkowski, W., Wilk, S. J., Ghajar, M. R., Balijepalli, A., & Ervin, J. (2012). CMOS-Compatible Silicon-on-Insulator MESFETs for Extreme Environments. In Extreme Environment Electronics (pp. 253-261). CRC Press.

- [3] England, T.D., Diestelhorst, R.M., Kenyon, E.W., Cressler, J.D., Ramachandran, V., Alles, M., Reed, R., Berger, R., Garbos, R., Blalock, B., & Mantooth, A. (2012). A new approach to designing electronic systems for operation in extreme environments: Part II-The SiGe remote electronics unit. IEEE Aerospace and Electronic Systems Magazine, 27(7), pp. 29-41.

- [4] Sissons, B., Mantooth, A., Di, J., Holmes, J. A., & Francis, A. M. (2015, March). SiGe BiCMOS comparator for extreme environment applications. In 2015 IEEE Aerospace Conference (pp. 1-8).

- [5] Mantooth, H. A., & Cressler, J. D. (2013). Power device platforms. In H. A. Mantooth (Ed.), Extreme Environment Electronics (p. 243). Boca Raton, FL: CRC Press.

- [6] Hassan, A., Savaria, Y., & Sawan, M. (2018). Electronics and Packaging Intended for Emerging Harsh Environment Applications: A Review. In IEEE Transactions on Very Large Scale Integration (VLSI) Systems.

- [7] Lien, W. C., Damrongplasit, N., Paredes, J. H., Senesky, D. G., Liu, T. J. K., & Pisano, A. P. (2014). 4H-SiC N-Channel JFET for Operation in High-Temperature Environments. *IEEE Journal of the Electron Devices Society*, 2(6), 164-167.

- [8] Rahman, A., Roy, S., Murphree, R., Kotecha, R., Addington, K., Abbasi, A., Mantooth, H.A., Francis, A.M., Holmes, J., & Di, J. (2016). High-Temperature SiC CMOS Comparator and op-amp for Protection Circuits in Voltage Regulators and Switch-Mode Converters. IEEE Journal of Emerging and Selected Topics in Power Electronics, 4(3), 935-945.

- [9] Yang, J. (2013). A harsh environment wireless pressure sensing solution utilizing high temperature electronics. *Sensors*, 13(3), 2719-2734.

- [10] Neudeck, P. G. (2013). SiC Integrated Circuit Platforms for High-Temperature Applications. In Extreme Environment Electronics (p. 225-232). CRC Press.

- [11] Gaska, R., Gaevski, M., Jain, R., Deng, J., Islam, M., Simin, G., & Shur, M. (2015). Novel AlInN/GaN integrated circuits operating up to 500°C. Solid-State Electronics, 113, 22-27

- [12] Herfurth, P., Maier, D., Men, Y., Rösch, R., Lugani, L., Carlin, J. F., Grandjean, N. & Kohn, E. (2013). GaN-on-insulator technology for high-temperature electronics beyond 400° C. Semiconductor Science and Technology, 28(7), 074026.

- [13] Germain, M., Derluyn, J., Van Hove, M., Medjdoub, F., Das, J., Cheng, S. D. K., Leys, M., Visalli, D., Marcon, D., Geens, K. & Viaene, J. (2010, April). GaN-on-Si power field effect transistors. In VLSI Technology Systems and Applications (VLSI-TSA), 2010 International Symposium on (pp. 171-172). IEEE.

- [14] Xu, Z., Wang, J., Cai, Y., Liu, J., Yang, Z., Li, X., Wang, M., Yu, M., Xie, B., Wu, W. & Ma, X. (2014). High temperature characteristics of GaN-based inverter integrated with enhancement-mode (E-Mode) MOSFET and depletion-mode (D-Mode) HEMT. IEEE Electron Device Letters, 35(1), 33-35.

- [15] Hussain, T., Micovic, M., Tsen, T., Delaney, M., Chow, D., Schmitz, A., Hashimoto, P., Wong, D., Moon, J.S., Hu, M., Duvall, J. & McLaughlin, D. (2003). GaN HFET digital circuit technology. Electron. Lett., 2003, 39, pp. 1708–1709.

- [16] Hassan, A., Ali, M., Trigui, A., Hached, S., Savaria, Y., & Sawan, M. (2017, June). Stability of GaN150-based HEMT in high temperature up to 400° C. In New Circuits and Systems Conference (NEWCAS), 2017 15th IEEE International (pp. 133-136). IEEE.

- [17] Hassan, A., Trigui, A., Shafique, U., Savaria, Y., & Sawan, M. (2016, May). Wireless power transfer through metallic barriers enclosing a harsh environment; feasibility and preliminary results. In Circuits and Systems (ISCAS), 2016 IEEE International Symposium on (pp. 2391-2394). IEEE.