# ResearchOnline@JCU

This is the author-created version of the following work:

Nguyen, Cong Dao, El Kass, Abdallah, Rahimi Azghadi, Mostafa, Jin, Craig T., Scott, Jonathan, and Leong, Philip H.W. (2017) *An enhanced MOSFET threshold voltage model for the 6–300 K temperature range*. Microelectronics Reliability, 69 pp. 36-39.

Access to this file is available from:

https://researchonline.jcu.edu.au/47976/

Please refer to the original source for the final version of this work:

http://dx.doi.org/10.1016/j.microrel.2016.12.007

# An Enhanced Threshold Voltage Model of MOSFETs for the 6-300 K Temperature Range

Nguyen Cong Dao<sup>a</sup>, Abdallah El Kass<sup>a</sup>, Mostafa Rahimi Azghadi<sup>a</sup>, Craig T. Jin<sup>a</sup>, Jonathan Scott<sup>b</sup>, and Philip H.W. Leong<sup>a</sup>

<sup>a</sup>School of Electrical and Information Engineering, The University of Sydney, NSW, Australia. E-mail: nguyen.dao@sydney.edu.au <sup>b</sup>School of Engineering, The University of Waikato, Hamilton, New Zealand

#### Abstract

An enhanced threshold voltage model for MOSFETs over a wide range of temperature from 6 K to 300 K is presented. The model takes into account the carrier freeze-out effect and the external field-assisted ionization to address the temperature dependence of MOS transistors. For simplicity, an empirical function is incorporated to predict short channel effects over the temperature range. The results from the proposed model demonstrate good agreement with NMOS and PMOS transistors measured from fabricated chips.

Keywords: Cryogenic Electronics, Threshold Voltage, MOSFETs.

#### 1. Introduction

The demand for deploying MOS circuits in extreme environments has recently increased with the inevitability of low temperature applications such as space exploration and quantum computing [1]. Devices operating at reduced temperatures show abnormal behaviour caused by effects such as carrier freeze-out, which strongly impact circuit performance [2, 3].

One of the key parameters in conventional MOSFET models is the threshold voltage, which is an essential quantity in MOSFET circuit design and an effective quality control indicator when evaluating device reliability [4]. Several works have mentioned the increase of the threshold voltage when temperature decreases mainly due to the change of Fermi potential [2, 3, 5–11]. Some attempts have been made to create low temperature MOS models, in which the threshold voltage at room temperature is replaced by its cold value [6, 7], or by polynomial fitting functions [8, 10]. Models devised for a specific temperature may need to be characterized at that temperature, and might not provide insight into the device behaviour over a wide temperature range. In addition, the complexity of the fitting function needs to be considered to achieve high computational efficiency. Therefore, a simplified threshold voltage model that faithfully accounts for wide changes in the temperature should be developed.

This work presents the first threshold voltage model for bulk CMOS transistors over the 6–300 K temperature range. We propose a simplified Fermi potential formula, which takes into account the freeze-out effect and the external field-assisted ionization. The short channel effect as a function of temperature is also presented.

#### 2. Temperature dependencies of Threshold voltage

# 2.1. N-channel devices

Threshold voltage is defined as a value of the gate voltage when the substrate immediately underneath starts to be in-

verted, forming a carrier channel between the source and drain. In a long N-channel device at zero substrate bias, the threshold voltage is given as [11]

$$V_{th0} = V_{FB} + \phi_0 + \gamma \sqrt{\phi_0} , \qquad (1)$$

where  $V_{FB}$  is the flat-band voltage,  $\gamma$  is the body-effect coefficient, and  $\phi_0$  is the surface potential. Also,  $V_{FB} = -|\phi_F| - \phi_{gate} - \frac{Q'_o}{C'_{ox}}$ , where  $|\phi_F|$  is the Fermi potential,  $\phi_{gate}$  is the work function of the gate,  $Q'_o$  represents the effective oxide charge per unit area, and  $C'_{ox}$  is the gate capacitance per unit area. In strong inversion  $\phi_0 \approx 2|\phi_F|$ , thus Eq. (1) becomes

$$V_{th0} = |\phi_F| - \phi_{gate} - \frac{Q'_o}{C'_{or}} + \gamma \sqrt{2|\phi_F|}$$

(2)

In Eq. (2),  $\phi_{gate}$  has almost no temperature dependence due to the gate being degenerately doped [2], and  $\frac{Q'_o}{C'_{ox}}$  can be assumed constant in strong inversion [7].

The conventional formula used to calculate the Fermi potential is  $\phi_F = \frac{k_B T}{q} \ln(\frac{N_A}{n_i})$ , where  $k_B$  is Boltzmann's constant, q is the elementary charge,  $n_i$  is the intrinsic concentration and  $N_A$  is the substrate doping concentration which is assumed equal to the ionized acceptor concentration  $N_A^-$  at room temperature. However, for a wide temperature range and especially at low temperatures where  $N_A^-$  is no longer equal to  $N_A$  due to the freeze-out effect,  $N_A^-$  is modelled as  $N_A^- = \frac{N_A}{1+4e^{(E_A-E_F)/k_BT}}$  (Fig. 1(a)) [12].

In this paper, the Fermi potential  $\phi_F$ , used in Fermi-Dirac statistics, is derived from the Fermi energy instead of carrier concentrations as  $\phi_F = \frac{E_F - E_i}{q}$ , where  $E_i$  is the intrinsic energy and  $E_F$  is the Fermi energy [11]. Taking into account the freezeout of acceptors and solving for the Fermi energy in the charge neutrality condition for p-type material [2], the Fermi potential

Figure 1: (a) Ionized Acceptor concentration  $N_A^-$ , (b) Ionized Donor concentration  $N_D^+$ , and (c) Simplified model of Fermi energy  $E_F$ .

$\phi_F$  is expressed as

$$\phi_{F} = \frac{E_{A} + E_{V}}{2q} - \frac{k_{B}T}{2q} ln \left(\frac{N_{A}}{4N_{V}}\right) - \frac{k_{B}T}{q} sinh^{-1} \left(\sqrt{\frac{N_{V}}{16N_{A}}} e^{-(E_{A} - E_{V})/2k_{B}T}\right),$$

(3)

where  $N_V \approx 2.0015 \times 10^{15} \times T^{3/2}$  is the effective density of states in the valence band for Si, and  $E_A$  and  $E_V$  are the energy level of acceptor and valence band, respectively [12]. Note that all energy levels are referenced to the intrinsic energy. Eq. (3) can be simplified by introducing the fitting parameter,  $\eta$ , and neglecting the inverse hyperbolic sine term to obtain

$$\phi_F \cong \frac{E_A + E_V}{2q} - \frac{\eta k_B T}{2q} ln \left(\frac{N_A}{4N_V}\right) \,. \tag{4}$$

This simplification makes  $\phi_F$  less computationally expensive and facilitates incorporating it into SPICE models. The difference between the simplified  $\phi_F$  in Eq. (4) versus the one in Eq. (3) is less than one percent. A plot of  $\phi_F$  or  $E_F$  referenced to  $E_i = 0$  is shown in Fig. 1(c).

The other factor that must be taken into account at low temperatures is field-assisted or Poole-Frenkel ionization [13]. This mechanism reveals that when a field is applied, the potential barrier moves lower meaning that the field assists carrier ionization. The reduction of the potential barrier due to an applied field can be determined as  $\Delta U = 2\sqrt{\frac{qF}{\varepsilon_{Si}}}$ , where F is the field strength, and  $\varepsilon_{Si}$  is the permittivity of silicon [13]. Based

on the Poole-Frenkel theory, we define  $\Delta\phi_G$  as the potential reduction caused by the external field or the gate voltage  $\Delta V_G$ . Therefore,  $\Delta\phi_G$  can be given as

$$\Delta \phi_G = 2\sqrt{\frac{q\Delta V_G}{\varepsilon_{Si} T_{ox}}},\tag{5}$$

where  $T_{ox}$  is the gate oxide thickness.

Since low temperatures lead to freeze-out of carriers, a sufficient field is required to assist the ionization of trapped carriers, depletion region formation, and channel formation. We propose a formula to calculate the potential change required to ionize and form the channel as follows

$$\frac{\Delta\phi_G}{k_BT} = \beta \left( \frac{\phi_{AF0}}{k_BT_0} - \frac{\phi_{AF}}{k_BT} \right) , \tag{6}$$

where  $\beta$  is an empirical constant which is proportional to the amount of potential reduction. Here,  $\phi_{AF}$  is the activation potential for acceptors defined as

$$\phi_{AF} = \frac{E_A - mE_F}{q} \,, \tag{7}$$

where m is a freeze-out coefficient corresponding to the strong freeze-out effect (this point will be discussed later). Also,  $\phi_{AF0}$  is the activation potential at room temperature  $T_0$ . Eq. (6) shows the amount of potential required to assist carrier ionization, and form the channel at the level of carrier concentration for room temperature.

From (5) and (6),  $\Delta V_G$  corresponding to the potential reduction  $\Delta \phi_G$  can be determined as

$$\Delta V_G = \frac{\varepsilon_{Si} T_{ox}}{4a} \beta^2 \left( \phi_{AF0} \frac{T}{T_0} - \phi_{AF} \right)^2 . \tag{8}$$

Therefore, the threshold voltage formula for a wide range of temperatures can be rewritten as

$$V_{th0} = |\phi_F| - \phi_{gate} - \frac{Q'_o}{C'_{ox}} + \gamma \sqrt{2|\phi_F|} + \Delta V_G$$

(9)

#### 2.2. P-channel devices

Similar to the N-channel devices, the threshold voltage model of P-channel devices over 6-300 K temperature range can be written as

$$V_{th0} = \phi_F - \phi_{gate} - \frac{Q_o'}{C_{ox}'} + \gamma \sqrt{2\phi_F} + \Delta V_G,$$

(10)

where

$$\phi_F \cong \frac{E_D + E_C}{2q} + \frac{\eta k_B T}{2q} ln \left(\frac{N_D}{2N_C}\right). \tag{11}$$

In Eq. (11),  $E_D$  and  $E_C$  are the energy levels of donors and conduction band, respectively [12].  $N_C \approx 5.4078 \times 10^{15} \times T^{3/2}$  is the effective density of states in the conduction band for Si. The ionized donors are given as  $N_D^+ = \frac{N_D}{1+2e^{(E_F-E_D)/k_BT}}$  [12], where  $N_D$  is the donor concentration (Fig. 1(b)).

The additional field-assisted ionization  $\Delta V_G$  for the P-channel devices also follows the proposed formula in Eq. (8) with the activation potential  $\phi_{AF}$  given as

$$\phi_{AF} = \frac{E_D - mE_F}{q} \ . \tag{12}$$

Note that the values of  $\eta$ ,  $\beta$ , and m for P-type and N-type are different (see Results section).

#### 3. Short channel effects

It is well known that the threshold voltage changes as the device scales down due to several phenomena such as the charge sharing effect, the lateral non-uniform doping effect, and the Drain Induced Barrier Lowering (DIBL) effect [11]. The short channel effect at room temperature, which is effectively modelled in the BSIM model, is given by [14]

$$V_{th} = V_{th0} + \Delta V th , \qquad (13)$$

where

$$\Delta V t h = \Delta V_{LD} - \Delta V_{SC} - \Delta V_{DIBL} . \tag{14}$$

Here,  $\Delta V_{LD}$  is the lateral non-uniform doping effect,  $\Delta V_{SC}$  is the short channel effect, and  $\Delta V_{DIBL}$  accounts for the DIBL effect (see [14] for detailed formula).

At low temperature, these effects are still present and must be modelled. For example, the charge sharing effect, which depends essentially on the depletion layer width, weakly varies when temperature down to 77 K [3] but it may strongly impact the threshold voltage once the substrate suffers strong freezeout at very low temperature [13]. For simplicity, we have devised an empirical function  $f_{SC}(T)$  to fit the geometry effects on the threshold voltage over a wide temperature range:

$$f_{SC}(T) = \left(1 + sgn(\phi_F(T))\frac{\phi_F(T)}{\phi_F(T_c)}\right)\delta_{Vth}, \qquad (15)$$

where  $\phi_F$  is the Fermi potential (positive for PMOS - Eq. (11), negative for NMOS - Eq. (4)), and  $\delta_{Vth}$  is a fitting parameter.  $T_C$  -the critical temperature (100 K), is empirically chosen at a point when the short channel effects are negligible. An extensive study on short channel effects at very low temperature is required to fully understand this phenomenon. Nevertheless, the presented fitting function Eq. (15) calculated from the proposed  $\phi_F$  and the short channel effects at room temperature can predict the impact of short channel effects with temperature.

The threshold voltage with short channel effects is therefore given as

$$V_{th} = V_{th0} + \Delta V th \times f_{SC}(T) . \tag{16}$$

# 4. Experimental setup

The NMOS and PMOS transistors used in this study were fabricated in the Austrian MicroSystems 0.35  $\mu m$  CMOS (C35) p-substrate mixed signal process. The device geometries vary from 0.35 to 10  $\mu m$ . The devices (64 transistors for each size)

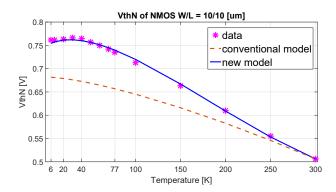

Figure 2: The temperature dependence of  $V_{th0}$  of NMOS: new model (Eq. (9)), conventional model (Eq. (1)) vs. experimental data (symbol)

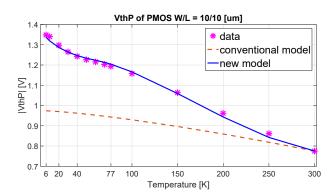

Figure 3: The temperature dependence of  $V_{th0}$  of PMOS: new model (Eq. (10)), conventional model (Eq. (1)) vs. experimental data (symbol)

were measured using a Keysight B1500A semiconductor analyzer with four Source Measurement Units (SMUs). The test chip was mounted in a Closed Cycle Refrigerator-based (CCR) cryogenic probe station (LakeShore CRX-4K) fitted with temperature controllers (LakeShore TC336). I-V curves were taken using pulsed measurement (duty cycle is 10% out of a 5 ms period) to minimize the self-heating effect. We used the Gm-Max method to extract the threshold voltage from Id-Vg measurements. This method eliminates the effect of series resistance which varies with temperature [4]. The mean value of the threshold voltage was taken from 64 extracted data with the maximum standard deviation is less than 10 mV.

## 5. Results and Discussions

The variation of the threshold voltage of a long channel NMOS as a function of temperature is shown in Fig. 2. The fitting parameter  $\eta$  in the Fermi potential model is 1.29,  $\beta$  = 10.365, and the freeze-out coefficient m in Eq. 7 is 1 over the 6-300 K temperature range. The other parameters such as  $T_{ox}$ ,  $C_{ox}$ ,  $\phi_{gate}$ ,  $Q'_{o}$  etc. are taken from AMS C35 process parameter [15] and calculated from extraction at room temperature. It is clear that the proposed model  $V_{th0}$  (Eq. 9) provides a better fit to the experimental data than the conventional model (Eq. 1) which is only valid at room temperatures.

The parameters  $\eta$  and  $\beta$  in the threshold voltage model for PMOS are 1.45 and 17.15, respectively. Unlike the NMOS, the

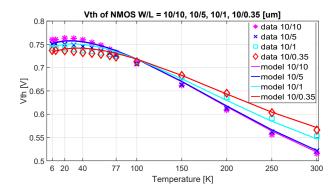

Figure 4: The short channel effects of NMOS  $V_{th}$ : model (–) vs. experimental data (symbol)

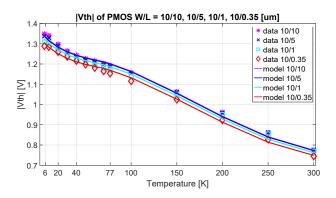

Figure 5: The short channel effects of PMOS  $V_{th}$ : model (–) vs. experimental data (symbol)

threshold voltage of PMOS does not saturate with decreasing temperature, rather it increases below 50 K as demonstrated in Fig. 3. The reason for this phenomenon could be due to the donors in P-channel suffer strong freeze-out. Consequently, further field-assisted ionization is required or the activation potential  $\phi_{AF}$  must be greater at very low temperatures. To model this effect, the freeze-out coefficient m for PMOS (Eq. 12) is chosen as 0.9 for temperature below 50 K and 1.0 for above 50 K.

The  $V_{th}$  model of NMOS ( $\delta_{Vth}$  = 4.3) and PMOS ( $\delta_{Vth}$  = 0.075) with the short channel effects are depicted in Fig. 4 and Fig. 5, respectively. The data indicates that our equations model the temperature dependence of the threshold voltage for the long and short channel MOS over the 6–300 K temperature range. The maximum error between the proposed model and experiment is less than three percent.

#### 6. Conclusion

We presented an enhanced threshold voltage model of NMOS and PMOS transistors for temperatures from 6 K to 300 K. The model is derived from the simplified Fermi potential which takes into account the carrier freeze-out effect. External field-assisted ionization is proposed and incorporated into the model to correct the threshold voltage. In addition, an empirical function that can be employed to estimate the short channel effects on the threshold voltage is also presented. The results

from the proposed model demonstrate good agreement with data measured from fabricated chips. This model can also be adapted to fit with other technologies since it is derived from the physics of the bulk CMOS and process dependent parameters.

#### Acknowledgement

The authors would like to thank Yuanyuan Yang, Kushal Das, and Prof. David Reilly for their support and advice. This work has been supported by the University of Sydney, Australian Institute for Nanoscale Science and Technology Accelerator Scheme.

#### References

- J. Hornibrook, J. Colless, I. C. Lamb, S. Pauka, H. Lu, A. Gossard, J. Watson, G. Gardner, S. Fallahi, M. Manfra, et al., Cryogenic control architecture for large-scale quantum computing, Physical Review Applied 3 (2) (2015) 024010.

- [2] E. A. Gutierrez-D, J. Deen, C. Claeys, Low temperature electronics: physics, devices, circuits, and applications, Academic Press, 2000.

- [3] G. Ghibaudo, F. Balestra, Low temperature characterization of silicon CMOS devices, Microelectronics Reliability 37 (9) (1997) 1353–1366.

- [4] A. Ortiz-Conde, F. J. García-Sánchez, J. Muci, A. T. Barrios, J. J. Liou, C.-S. Ho, Revisiting mosfet threshold voltage extraction methods, Microelectronics Reliability 53 (1) (2013) 90–104.

- [5] F. Balestra, G. Ghibaudo, Brief review of the MOS device physics for low temperature electronics, Solid-state electronics 37 (12) (1994) 1967– 1975.

- [6] Y. Feng, P. Zhou, H. Liu, J. Sun, T. Jiang, Characterization and modelling of MOSFET operating at cryogenic temperature for hybrid superconductor-CMOS circuits, Semiconductor science and technology 19 (12) (2004) 1381.

- [7] N. Yoshikawa, T. Tomida, M. Tokuda, Q. Liu, X. Meng, S. Whiteley, T. Van Duzer, Characterization of 4 K CMOS devices and circuits for hybrid Josephson-CMOS systems, IEEE Transactions on Applied Superconductivity 15 (2) (2005) 267–271.

- [8] H. Zhao, X. Liu, A low-power cryogenic analog to digital converter in standard CMOS technology, Cryogenics 55 (2013) 79–83.

- [9] H. Zhao, X. Liu, Modeling of a standard 0.35 μm CMOS technology operating from 77 K to 300 K, Cryogenics 59 (2014) 49–59.

- [10] A. Akturk, M. Holloway, S. Potbhare, D. Gundlach, B. Li, N. Goldsman, M. Peckerar, K. Cheung, Compact and distributed modeling of cryogenic bulk MOSFET operation, IEEE Transactions on Electron Devices 57 (6) (2010) 1334–1342.

- [11] Y. Tsividis, Operation and modeling of the MOS transistor.

- [12] S. M. Sze, K. K. Ng, Physics of semiconductor devices, John wiley & sons, 2006.

- [13] D. P. Foty, Impurity ionization in MOSFETs at very low temperatures, Cryogenics 30 (12) (1990) 1056–1063.

- [14] Y. Cheng, M. Chan, K. Hui, M.-c. Jeng, Z. Liu, J. Huang, K. Chen, J. Chen, R. Tu, P. K. Ko, et al., BSIM3v3 manual, University of California, Berkeley.

- [15] 0.35µm CMOS process (C35), accessed: 2016-11-09.

URL http://ams.com/eng/Products/Full-Service-Foundry/Process-Technology/CMOS/0.35-m-CMOS-process