# Parallel Graph Component Labelling with GPUs and CUDA

K.A. Hawick<sup>☆</sup>, A. Leist and D.P. Playne

Institute of Information and Mathematical Sciences

Massey University – Albany, North Shore 102-904, Auckland, New Zealand

Email: { k.a.hawick, a.leist, d.p.playne }@massey.ac.nz

Tel: +64 9 414 0800 Fax: +64 9 441 8181

#### Abstract

Graph component labelling, which is a subset of the general graph colouring problem, is a computationally expensive operation that is of importance in many applications and simulations. A number of data-parallel algorithmic variations to the component labelling problem are possible and we explore their use with general purpose graphical processing units (GPGPUs) and with the CUDA GPU programming language. We discuss implementation issues and performance results on GPUs using CUDA. We present results for regular mesh graphs as well as arbitrary structured and topical graphs such as small-world and scale-free structures. We show how different algorithmic variations can be used to best effect depending upon the cluster structure of the graph being labelled and consider how features of the GPU architectures and host CPUs can be combined to best effect into a cluster component labelling algorithm for use in high performance simulations.

Key words: graph, component label, mesh, GPU, CUDA, data-parallel

#### 1. Introduction

Graph component labelling is an important algorithmic problem that occurs in many applications areas. Generally, the problem involves identifying which nodes in a graph belong to the same connected cluster or component. In many applications the graph of interest has undirected arcs and all nodes in a connected cluster are fully and mutually reachable. Some applications problems will give rise to structural graphs that are generated as a number of separate clusters, or break up into separate clusters or coagulate into larger super-clusters as a result of some dynamical process. In some cases the graph is simply a structural one and connectivity is determined entirely by the presence or absence of arcs between nodes.

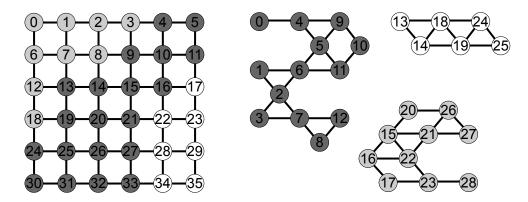

Many simulations problems are formulated in terms of a set of variables on a mesh and the value of the variables on the nodes can be used to differentiate between nodes that are connected or not. Figure 1 shows two examples of graph colouring and labelling applications problems. On the left a set of variables on a regular mesh graph have been coloured according to their similarity properties, whereas on the right a structural graph has been coloured according to its cluster components. Examples of the former case are the Ising model, Potts model, other lattice physics models and field models where the structural arcs are fixed - in a nearest neighbour pattern for example - but where some property of each node that can change dynamically, indicates whether two adjacent nodes are part of the same cluster or not. Examples of the latter case include analysis of computer networks; sociological networks; and other relationship network graphs.

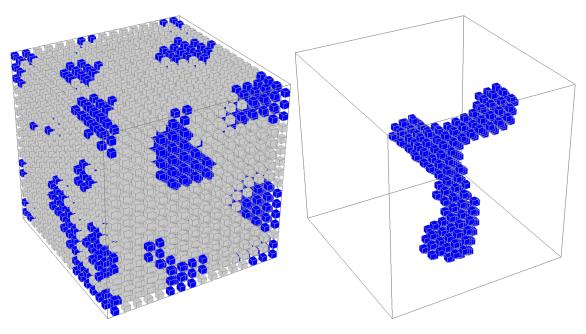

Figure 2 illustrates how component labelling can be used to analyse the results of a simulation. The figure shows a Kawasaki spin-exchange Ising model simulation[1] where a random mixture of spins (coloured dark blue and white) has been quenched to a low temperature and clusters or components have formed in the model system. Models such as these exhibit phase transitions and the component size distribution can be used to examine and identify the location and properties of the resulting phase transitions.

<sup>&</sup>lt;sup>☆</sup>Author for correspondence

Figure 1: Component labelling on a regular mesh (left) - where each site has a known number of neighbours but different properties - and on an arbitrary graph (right). Different colours (shades) denote different components. Mesh problems arise from simulations where each node has **different model specific properties**, eg spin, or velocity direction or some other model value that dictates whether two physically adjacent nodes are deemed to be part of the same "model component". The regular mesh has in this case 26 separate clusters, the largest with 3 nodes, the arbitrary graph has 3 separate components, the largest with 8 nodes.

Figure 2: The cubic system on the right is a body-centred cubic configuration of spins (blue and grey) of a Kawasaki spin-exchange Ising model that has been equilibrated below the critical temperature. The image on the right is the largest component of the blue minority (0.2 volume fraction) phase.

Until recently, use of component analysis was computationally expensive compared to the simulation update computational costs. It was therefore impractical as a metric of simulations except when used infrequently during model evolution – such as to analyse static model configuration dumps. Fast component labelling algorithms such as we describe here for use on a cheap accelerator platform such as a GPU, enable use of component labelling more frequently in simulations.

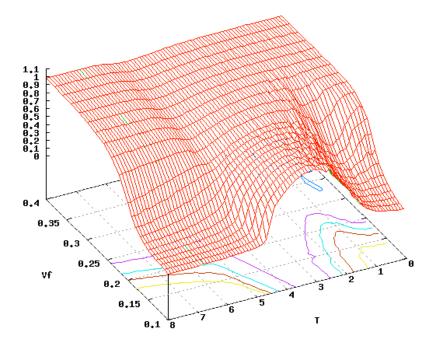

Figure 3 shows how the largest component measurements can be used to identify special properties of a model system such as the location in parameter space of a phase transition. The figure shows how the normalised fraction of the model system that is occupied by the giant largest component of the minority (dark spin) phase of the model shown in figure 2 varies with temperature and minority volume fraction. The crease in the surface locates the phase transition.

Graph colouring is of course not a new idea, although as mentioned it has previously been impractically expensive to compute regularly during a simulation. There are a number of well-known algorithms for graph colouring [2] including parallel algorithms for speeding up graph calculations [3] as well as those specifically on graph colouring such as [4, 5]. In addition, a number of parallel component labelling applications have been described in the applications literature, particularly for use in lattice physics simulation models [6, 7], studies of percolation [8], and studies of other phase transitions [9].

Figure 3: Largest component analysis of model system such as shown in figure 2. The normalised fraction occupied by the largest component cluster of the minority (blue) phase is plotted as a surface as it varies with the model temperature T and the minority volume fraction  $V_f$  (percentage of blue spins). The phase transition is revealed elegantly from the component labelling analysis and identification of the size of the largest cluster component. Measurements shown are averaged over 100 independent model runs on a  $32 \times 32 \times 32$  body centred cubic system.

Parallel graph colouring is a problem that tends to work well on data-parallel systems and during the last golden age of data parallelism, computers such as the Distributed Array Processor (DAP) [10] and the Connection Machine examples [11] had software libraries with built-in routines for component labelling on regular rectilinear data structures such as images.

Graphical Processing Units (GPUs) such as NVIDIA's GeForce series have revitalised interest in dataparallel computing since they offer dedicated data-parallel hardware on the graphics chip but are also readily integrated into a compute server and make the parallel capability accessible to the applications programmer through use of NVIDIA's Compute Unified Device Architecture (CUDA). While CUDA is presently specific to NVIDIA hardware, the Open Compute Language (OpenCL) has similar capabilities and programming interface.

In this article we describe how some of the well-known data-parallel graph component labelling algorithms can be adapted to make specific and optimal use of GPU hardware and how this can be expressed in a relatively high-level manner using programming languages like CUDA. We describe the component labelling problem in Section 2 and the CUDA GPU architecture in Section 3. Our experience has been that applications that require component labelling fall into major classes - firstly those that employ arbitrarily structured graphs such as random graphs or scale-free and Watts-Strogatz "small-world" graphs and secondly those that use regular rectilinear data such as images or hypercubic lattice data. There are quite different optimisations that can be made in the two cases. We describe parallel algorithms both for arbitrarily structured graphs (Section 4) and more symmetric mesh and lattice graphs (Section 5) and show how they can be implemented on GPUs with a data parallel language like CUDA. We present some performance results using NVIDIA GeForce 260 GPUs in Section 6 and in Section 7 we discuss the implications for component labelling applications and offer some conclusions and areas for future optimisation work.

GPUs are typically programmed using a conventional host calling program written in (for example) "C" that runs on the hosting CPU with specific fast 'kernel" programs that are called and which run on the GPU. A large part of our article describes these parallel kernel algorithms in detail. For clarity we refer to Kernels 1,2,3 that address the arbitrary graph component labelling problem and Kernels A,B,C,D which address hypercubic regular data component labelling.

# 2. Graph Component Labelling Algorithms

In the context of general graphs and graph theory [12] graph labelling is a well known problem with relatively easy to understand (serial) algorithms [13]. Generally graph component labelling is a subset problem of the wider colouring problems [14] with a number of known algorithmic variations [15].

One perspective on the problem is in terms of equivalence classes and the popular formulation in Numerical Recipes books [16] shows how a predicate function that specifies equivalence or "connected-ness" can be used to iteratively sweep across all pairs of graph nodes to identify clusters or equivalence classes. In the case of simulations or applications involving fixed graphs or meshes, we often know the adjacency lists in advance and it is not necessary to conduct sweeps over all-pairs of nodes. In our work, we assume this is the case, and that some data structure exists that specifies the subset of nodes that are considered adjacent to a particular node.

Figure 4: A  $12 \times 6$  periodic (opposite edges are connected) nearest-neighbour mesh where the cluster "sameness" also depends on the variables decorating the graph nodes. Graph node k=0 has exactly 4 nearest neighbouring nodes that it is adjacent to (1,11,12,60), but it has correctly been identified as the sole member of cluster j=5 where nodes "need to be green" and be "nearest-neighbour connected" to be part of the same cluster. There are thus 8 clusters in total found and we want them labelled accordingly.

Figure 2 illustrates the component labelling problem for a d-dimensional rectilinear image. It is required that each vertex be coloured or labelled with each component having a unique integer label. Arbitrary graph

vertices can be indexed explicitly by some integer k but even in the case of a hyper-cubic mesh, image or lattice, these indices can encode the spatial dimensions  $(x_1, x_2, ..., x_d)$  in some order of significance [17].

The initial labelling of individual vertices is often the slowest algorithmic component as it may involve sweeping through the adjacency information iteratively. To make use of the correctly labelled component information however, an application may need to carry out some "book-keeping" operations to tidy up the label information into a structure such as that shown on the right of Figure 2 - whereby subsequent iterations over each component cluster can be made - for example to compute cluster moments or average properties. It is also often desirable that the cluster structure be compactified, particularly where the number of components is relatively small compared to the total number of vertices.

In summary, starting from a graph, specified either as a mesh or as a set of adjacency information, we often want to: colour the vertices uniquely according to component; determine how many unique colours (components) we have used; gather pointers for each cluster to allow efficient subsequent iteration by cluster. In addition, depending upon the application we may also want to: compactify the colours to a contiguous and continuous integer list; sort the colours by cluster sizes; histogram the size distribution; apply some algorithm to one or more clusters, or remove them from the set.

Sequential algorithms for component labelling will typically be implemented as a sweep through all the graph nodes, adjusting their component "colours" according to adjacency information until each component has a single and unique colour - usually in the form of an integer label. The sweep is usually organised as a breadth first tree search, with various accelerating heuristics, depending upon properties of the data. Some formats lend themselves particularly well to various heuristics and also to parallel algorithms. The data-parallel GPU is well-suited to carrying out the data-parallel operations of component labelling and its host CPU can be employed fairly easily to carry out the book-keeping support operations serially, and usually with more ordinary or global memory available than the dedicated memory available on the GPU card itself.

### 3. GPU Architecture

In this section we give a brief summary of GPU-specific terms used in the rest of this article. Graphics Processing Units or GPUs provide a high computational throughput due to their large number of processor cores. GPUs contain multiprocessors (MPs) which each contain eight Scalar Processors (SPs) and additional memory. These architectures use the SIMT (Single Instruction Multiple Thread) parallel programming paradigm. The SPs within a single MP must execute the same instruction synchronously while the MPs in the GPU can execute instructions independently of each other.

A large number of threads is required to make full use of a GPUs computing capability. The GPU can manage, schedule and execute many threads in hardware to avoid high thread management overheads. These threads are organised as a large grid of blocks. Each block is a 3D structure that can contain up to 512 threads with maximum sizes of  $\{512, 512, 64\}$  and the grid is a 2D structure with maximum sizes of  $\{65535, 65535\}$ . The threads are executed by assigning thread blocks to MPs. The multiprocessors will split the thread blocks into sets of 32 threads known as warps. When executing instructions, the MP will select a warp that is ready to execute and issue it an instruction

Each thread has a unique id that it can work out from it's threadIdx and blockIdx. The blockIdx identifies which block the thread belongs to and the threadIdx defines the thread's position within the block.

There is no automatic memory caching on the GPU, instead a number of optimised memory types are made available to be explicitly used by the programmer. These memory types are:

Global Memory is the main device memory on the GPU. Any input/output to and from the GPU must be placed in global memory. This memory also has the slowest access time. The number of necessary global memory transactions can be reduced by a technique known as coalescing. When 16 sequential threads access 16 sequential and aligned values in memory, the GPU will automatically combine them into a single transaction.

**Shared Memory** is stored within the MPs and allows threads in the same block to share information. The main use of the memory is to act as an explicit access cache to allow the number of global memory transactions to be reduced by sharing common data between threads.

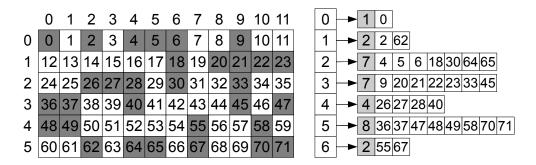

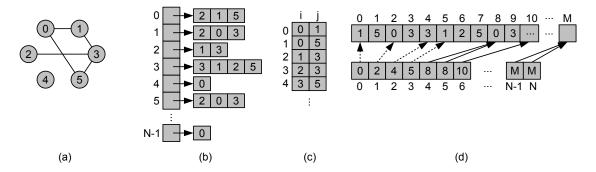

Figure 5: The data structures used to represent the graph by the CPU and GPU implementations. All three examples represent the same undirected graph shown by (a). (b) shows the adjacency-list representation used by the CPU algorithm. Every vertex  $v_i \in V$  stores a list of its neighbours at index i of the vertex array. The first element of each adjacency-list is its length  $|A_i|$ , also called its out-degree  $k_{i.out}$  or simply degree  $k_i$ . The following elements are the indices of the adjacent vertices, that is the arc set  $A_i \subseteq A$ . To represent an undirected edge, each one of its end points needs to store the respective neighbour. (c) illustrates the edge set E used by Kernel 1. Every edge  $e_{\{i,j\}} \in E$  is represented by a 2-tuple, which stores the IDs of the respective end points. (d) shows the vertex set V (bottom) and the arc set A (top) used by Kernels 2 and 3. Every vertex  $v_i \in V$  stores the start index of its adjacency-list  $A_i$  at index i of the vertex array. The adjacency-list length  $|A_i|$  can be calculated by looking at the adjacency-list start index of  $v_{i+1}$  (V[i+1]-V[i]). The vertex array contains |V|+1 elements so that this works for the last vertex too.

**Texture Memory** is a cached method of accessing a designated piece of global memory. The texture cache is located on the MPs. Textures can be created in 1-, 2- and 3-dimensions and will automatically cache values in the same spatial locality. This will improve performance when threads access values in some regular spatial neighbourhood.

**Constant Memory** is another cached method of accessing a small section of global memory. This cache is designed to allow multiple threads to access the same value out of the cache at once. This is very useful when all the threads in a block must access the same value from memory.

## 4. Arbitrarily Structured Graphs

This section describes our (serial) CPU and (parallel) GPU algorithms used to label the components of arbitrary graphs. Such graphs are arbitrary in the sense that their structure is not known beforehand. Examples are random graphs [18] and complex networks, such as metabolic networks [19, 20, 21], human collaboration networks [22, 23] and many other types of social networks [24, 25, 26], as well as computer networks like the World-Wide Web [27] to name but a few. These graphs require a data structure that has no built-in assumptions about graph structure and in particular, that supports arbitrarily long (and potentially widely differing) adjacency list lengths for each vertex node.

## 4.1. Data Structures

An arbitrary graph can be represented in different ways in memory. The data structure can have a critical impact on the performance of the labelling algorithm. Different hardware architectures with diverse memory hierarchies and processing models often require different data structures to achieve high performance. We restrict ourselves to undirected graphs for this article, but the data structures and algorithms described in this section can easily be adapted to work with directed graphs as well. Figure 5 illustrates the data structures used to represent an arbitrary graph in the main memory of the host system or the device memory of the graphics card.

The graph representations in device memory are designed so that the CUDA kernels can maximise the utilisation of the available memory bandwidth. One important way to do this is to reduce the number of non-coalesced memory transfers. Coalescing is a feature of CUDA devices that enables them to combine the global memory reads or writes of 16 sequential threads into a single memory transaction. The threads have to access addresses that lie in the same memory segment of size 32-, 64- or 128-bytes for coalescing to work

(CUDA compute capability 1.2 or higher). This memory block also needs to be aligned to the segment size. A more detailed description and analysis of coalescing and its performance implications can be found in the CUDA Programming Guide [28]. Trying to reduce the number of non-coalesced memory transactions and in general to optimise the device memory accesses is a challenge for arbitrary graphs on CUDA devices, as the structure of the graph is not known beforehand.

### 4.2. The CPU Reference Implementation

This section describes the single-threaded CPU implementation used as a comparison to the CUDA kernels. We realise, of course, that a multi-threaded implementation on a multi-core or multi-CPU system could achieve better performance than the serial one, but we do not intend to compare parallel-processing techniques on different architectures in this paper. We are merely interested in investigating the performance of graph labelling algorithms on CUDA devices and provide the CPU performance for comparison.

The algorithm (see Algorithm 1) initialises the colours of all vertices to distinct values. It then iterates over the vertex set V and starts the labelling procedure for all vertices  $v_i \in V$  that have not been labelled yet as indicated by the frontier array F. The labelling procedure iterates over the arc set  $A_i \subseteq A$  of vertex  $v_i$ , comparing its colour value  $c_i$  with that of its neighbours. If it finds that the colour value  $c_j$  of a neighbour  $v_j$  is greater than  $c_i$ , then it sets  $c_j$  to the value of  $c_i$  and recursively calls the labelling procedure for  $v_j$ . If, on the other hand, it finds a neighbour  $v_j$  with a lower colour value, it sets the colour  $c_i$  to the value  $c_j$  and starts iterating over the adjacency-list from the beginning again. This means that once the labelling procedure reaches the end of the adjacency-list of vertex  $v_i$ , all vertices that are reachable from  $v_i$  are labelled with the same colour value.

**Algorithm 1** The single-threaded CPU reference implementation of the component labelling algorithm for arbitrary graphs. Although the data structure used by this algorithm uses lists of directed arcs to represent the links between vertices, it assumes that if there is an arc (i, j) in the adjacency-list  $A_i \subseteq A$  of vertex  $v_i \in V$ , then there is also an arc (j, i) in the adjacency-list  $A_j \subseteq A$  of vertex  $v_j \in V$ . Thus, the algorithm essentially works on edges.

## function LABEL\_COMPONENTS\_CPU(G)

```

Input parameters: The graph G := (V, A) is an array of adjacency-lists, one for every vertex v \in V. The arc set A_i \subseteq A of a vertex v_i is stored in position V[i]. |V| is the number of vertices in G and |A_i| is the number of neighbours of v_i (i.e. its degree).

declare integer C[|V|] //C[i] stores the colour of vertex v_i

declare boolean F[|V|] //F[i] indicates if vertex v_i still needs to be processed

```

```

declare boolean F[|V|] //F[i] indicates if vertex v_i still needs to be processed for all v_i \in V do C[i] \leftarrow i //initialise every vertex to a unique colour value F[i] \leftarrow true end for for all v_i \in V do if F[i] = true then call PROCESS_CPU(G, C, F, v_i) end if end for return C //C now contains the component ID for every vertex v \in V.

```

# 4.3. The CUDA Implementations

The three CUDA kernels solve the task of labelling the components of an input graph in very different ways. As described in Figure 5, Kernel 1 uses a different data structure from Kernels 2 and 3. While Kernel 1 works on the edge set, executing one thread for every edge for a total of |E| threads, Kernels 2 and 3 operate on the vertex set, executing one thread for every vertex for a total of |V| threads. The kernels are described in the following paragraphs. As a convention for the pseudo-code, variables located in graphics device memory are identified with a subscript d (e.g.  $V_d$ ).

```

\begin{aligned} & \textbf{function} \ \mathsf{PROCESS\_CPU}(G,C,F,v_i) \\ & F[i] \leftarrow \mathsf{false} \\ & \textbf{for all} \ (i,j) \in A_i \ \textbf{do} \\ & \textbf{if} \ C[i] > C[j] \ \textbf{then} \\ & C[i] \leftarrow C[j] \\ & \text{re-run the for-loop from the beginning of the adjacency-list} \\ & \textbf{else if} \ C[i] < C[j] \ \textbf{then} \\ & C[j] \leftarrow C[i] \\ & \textbf{call} \ \mathsf{PROCESS\_CPU}(G,C,F,v_j) \\ & \textbf{end if} \\ & \textbf{end for} \end{aligned}

```

### 4.3.1. Edge-Based Kernel 1

In this approach, the colours array is initialised to a unique integer value for every vertex  $v \in V$ . Every thread loads one edge  $e := \{i, j\} \in E$  from the edge set and compares the colours  $c_i$  and  $c_j$  of the two vertices  $v_i$  and  $v_j$ . If one of the colour values is smaller than the other, then the colour of the vertex with the higher colour value is updated. An atomicMin operation is used for this to ensure that simultaneous updates by different threads do not interfere with each other and do not rely on a particular ordering. In addition to updating the colour, the thread also sets a flag that indicates that there are still changes being made to the vertex colours. This last operation can also cause simultaneous writes to the same address by multiple threads. However, CUDA guarantees that at least one of them will succeed, which is all that is needed here. The kernel is called until no more changes are being made. The pseudo-code of this kernel is given in Algorithm 2.

Performance: The performance of the algorithm depends strongly on the graph diameter d—that is, the longest of the shortest paths connecting any two vertices within the same component of the graph—since the colour needs d steps to propagate between all vertices. However, this does not mean that the kernel has to be called d times, as the |E| threads are not actually all executing at the same time. This means that the changes to the colour of a vertex  $v_i$  made while processing an edge  $\{i,j\}$  can already be visible when processing an edge  $\{i,k\}$  at a later time during the same kernel call. The diameter is thus the upper bound for the number of kernel calls. If the graph consists of more than one disjoint component, then the diameter of the component with the largest value for d is relevant.

CUDA specific optimisations: The kernel uses a boolean flag in shared memory to indicate if any changes have been made by one or more threads in this block. If this flag is set to true once all threads in the block have completed their work, then the first thread in the block sets the respective flag in global memory to true. This optimisation reduces the number of global memory writes and replaces them with much faster writes to shared memory.

# 4.3.2. Vertex-Based Kernel 2

Kernel 2, just like Kernel 1, initialises the colours array to a unique integer value for every vertex  $v \in V$ . Every thread  $t_i$  then loads the adjacency-list start index of vertex  $v_i$  into shared memory. This allows all but the last thread in the block to calculate the adjacency-list length  $|A_i|$  of their vertex without another read from global memory. Every thread then checks if its vertex is flagged as active in the frontier array, which means that this is either the first kernel iteration (all vertices are flagged) or that its colour has changed in the previous kernel call and therefore needs to be compared to the colour values of its neighbours. The next step for all threads that are flagged is to load the current colour  $c_i$  of their vertex. Now they can iterate through their adjacency-lists, comparing  $c_i$  with the colour  $c_j$  of every one of their neighbours  $v_j$  and updating either one of the colours if its value is higher than that of the other vertex. The kernel is called until no more changes are being made. The pseudo-code of this kernel is given in Algorithm 3.

Performance: Just like with Kernel 1, the performance of this algorithm depends strongly on the graph diameter d, as the colour needs d steps to propagate between all vertices. Again, this does not mean that d iterations are needed for the colour to spread through the connected components.

**Algorithm 2** Kernel 1: The first approach to labelling the components of an arbitrary graph in parallel on a CUDA-enabled device. This kernel operates on the edge set E, running one thread for every edge for a total of |E| threads per kernel call.

```

function LABEL_COMPONENTS_KERNEL1_HOST(E, N)

```

```

Input parameters: E is the list of all edges in a graph G := (V, E). N = |V| is the number of vertices. declare {integer,integer} E_d[|E|] in device memory //C_d[i] stores the colour of vertex v_i copy E_d \leftarrow E //copy the edge list to the device do in parallel on the device using N threads: initialise C_d[1 \dots N] such that C_d[i] \leftarrow i declare boolean m //m indicates if the labels are still changing declare boolean m_d in device memory repeat copy m_d \leftarrow \text{false} do in parallel on the device using |E| threads: call LABEL_COMPONENTS_KERNEL1(E_d, C_d, m_d) copy m \leftarrow m_d until m = \text{false} //\text{repeat} until the colours are not changing any more declare integer C[N] copy the colours to the host return C //C now contains the component ID for every vertex v \in V.

```

```

function LABEL_COMPONENTS_KERNEL1(E_d, C_d, m_d)

declare integer t \leftarrow thread ID queried from the CUDA runtime

declare {integer,integer} e_t \leftarrow E_d[t] //read the edge e_t := \{i,j\} \in E_d from device memory

declare integer c_i \leftarrow C_d[i] //read the colour c_i of vertex v_i from device memory

declare integer c_j \leftarrow C_d[j] //read the colour c_j of vertex v_j from device memory

if c_i < c_j then

call atomicMin(C_d[j], c_i)

m_d \leftarrow true

else if c_j < c_i then

call atomicMin(C_d[i], c_j)

m_d \leftarrow true

end if

```

CUDA specific optimisations: In addition to the shared memory flag already used in Kernel 1, this kernel uses an array in shared memory to store the adjacency-list start indices of the threads within the same thread block as described before. Furthermore, it uses a one-dimensional texture reference to iterate over the arc set A. Texture fetches are cached and can potentially exhibit higher bandwidth as compared to non-coalesced global memory reads if there is locality in the texture fetches. And since a thread  $t_i$  iterates over  $|A_i|$  consecutive values and thread  $t_{i+1}$  iterates over the directly following  $|A_{i+1}|$  consecutive values and so on, this locality is given. The CUDA code for these optimisations is shown in Algorithm 4.

The implementation of Kernel 2 described in this article uses one texture reference for the arc set. As the maximum width for a texture reference bound to linear memory is  $2^{27}$  for all currently available CUDA devices (compute capabilities 1.0-1.3), it can only process graphs with up to  $2^{27}$  arcs or half as many edges (each edge is represented by two arcs). The maximum size of the arc set is thus 512MB (4 bytes per arc). As some graphics cards provide more device memory than 512MB, they could be used to process larger graphs if it was not for this limitation. In that case, two or more texture references could be used to access the arc set when necessary. It is important to ensure that the size of the arc set does not exceed this limit, as the CUDA libraries do not give any warning or failure message when trying to bind more elements than supported to the texture reference. The kernel executes as if everything was normal and only the incorrect results, if spotted, show that something went wrong. This is a commonly encountered problem when using

CUDA and requires particular care from the programmer.

Each thread in Kernel 2 iterates over the adjacency-lists of one vertex, which causes warp divergence if the degrees of the vertices that are being processed by the threads of the same warp are not the same. Due to the SIMD data model (or SIMT in CUDA terminology), all threads in a warp have to do  $k_{max}$  iterations, where  $k_{max}$  is the highest degree processed by this warp. This problem can be reduced by sorting the vertices by their degree. However, the time to sort the vertices on the CPU and the overhead in the CUDA kernel, which comes from the fact that the vertex ID is no longer equal to the thread ID and therefore has to be looked up from device memory, are considerable. Our experiments have showed that this technique can slightly improve the kernel execution time when processing scale-free graphs with their "fat tail" degree distributions, but the overall execution time, which includes the time required to sort the vertices by the CPU, increases considerably. These findings are in line with previous results reported in [29]. Consequently, the implementation of Kernel 2 reported here does not sort the vertices. Nevertheless, other graph algorithms may benefit from this technique, for example when they execute the same kernel multiple times without changes to the graph structure.

**Algorithm 3** Kernel 2: The second approach to labelling the components of an arbitrary graph in parallel on a CUDA-enabled device. This kernel operates on the vertex set V, running one thread for every vertex for a total of |V| threads per kernel call. Like in the CPU reference implementation described in Algorithm 1, the kernel operates on a set of arcs but assumes that for every arc (i, j) an arc (j, i) exists as well.

```

function LABEL_COMPONENTS_KERNEL2_HOST(V, A)

```

```

Input parameters: The vertex set V and the arc set A describe the structure of a graph G := (V, A).

Every vertex v_i \in V stores the index into the arc set at which its adjacency-list A_i begins in V[i]. The

adjacency-list length |A_i| is calculated from the adjacency-list start index of vertex v_{i+1} (V[i+1]-V[i]).

To make this work or the last vertex v_N \in V, the vertex array contains one additional element V[N+1].

This additional element is not included in the number of vertices |V|. |A| is the number of arcs in G.

declare integer V_d[|V|+1] in device memory //allocate memory for the vertex list V

declare integer A_d[|A|] in device memory //allocate memory for the arc list A

declare integer C_d[|V|] in device memory //C_d[i] stores the colour of vertex v_i

declare boolean F1_d[|V|], F2_d[|V|] in device memory //F1_d[i] indicates if a vertex v_i is to be processed

in the current iteration and F2_d[i] indicates if it is to be processed in the next iteration

copy V_d \leftarrow V //copy the vertex set to the device

copy A_d \leftarrow A //copy the arc set to the device

do in parallel on the device using |V| threads: init. C_d[1...|V|], F_{1d}[1...|V|], F_{2d}[1...|V|] such that:

C_d[i] \leftarrow i, F1_d[i] \leftarrow \text{true and } F2_d[i] \leftarrow \text{false}

declare boolean m / m indicates if the labels are still changing

declare boolean m_d in device memory

copy m_d \leftarrow \text{false}

do in parallel on the device using |V| threads:

call LABEL_COMPONENTS_KERNEL2(V_d, A_d, C_d, F1_d, F2_d, m_d)

F1_d \leftrightarrow F2_d //swap the frontier arrays for the next iteration

copy m \leftarrow m_d

until m = \text{false } //\text{repeat until the colours are not changing any more

declare integer C[N]

copy C \leftarrow C_d //copy the colours to the host

return C //C now contains the component ID for every vertex v \in V.

```

#### 4.3.3. Breadth-First-Search Kernel 3

This approach is based on the CUDA algorithm for a breadth-first search proposed by Harish and Narayanan [3]. Instead of calculating the cost to reach all vertices in the same component as a given source

```

function LABEL_COMPONENTS_KERNEL2(V_d, A_d, C_d, F1_d, F2_d, m_d)

declare integer i \leftarrow thread ID queried from the CUDA runtime //equal to the vertex ID of v_i

if F1_d[i] = \text{true then}

F1_d[i] \leftarrow \text{false}

declare integer idx_i \leftarrow V_d[i] //the start index of A_i \subseteq A in A_d

declare integer idx_{i+1} \leftarrow V_d[i+1] //the start index of A_{i+1} \subseteq A in A_d (the upper bound for v_i)

declare integer c_i, c_j //the colours of vertex v_i and v_j

c_i \leftarrow C_d[i] //read c_i from device memory

declare boolean c_{i(mod)} \leftarrow false //indicates if c_i has been changed

for all j \in A_i do

c_j \leftarrow C_d[j] //read the colour of the adjacent vertex j from device memory

if c_i < c_j then

call atomicMin(C_d[j], c_i)

F2_d[j] \leftarrow \text{true } //v_j \text{ will be processed in the next iteration}

m_d \leftarrow \text{true}

else if c_i > c_j then

c_i \leftarrow c_j

c_{i(mod)} \leftarrow \text{true}

end if

end for

if c_{i(mod)} = \text{true then}

call atomicMin(C_d[i], c_i) //c_i was changed and needs to be written to device memory

F2_d[i] \leftarrow \text{true } //v_i \text{ will be processed again in the next iteration}

m_d \leftarrow \text{true}

end if

end if

```

vertex, however, our implementation assigns the same colour label to all vertices in the same connected component for all components in the graph. Kernel 3 described here also avoids a race condition that can occur in Algorithm 2 of [3], where one thread can evaluate line 5 and therefore assume that the neighbour has not been processed yet before that vertex sets the evaluated flag to true in line 3. Our implementation uses two frontier arrays to solve this problem, one for the current iteration and one for the next iteration, which are swapped between kernel calls.

Kernel 3 initialises the colours array to 0, which indicates that the respective vertex has not been coloured yet. The breadth-first search starts from a source vertex  $v_{src} \in V$  with a new colour value  $c_{src}$  and spreads this colour further through the component  $C_i \subseteq V$ , where  $v_{src} \in C_i$ , until all reachable vertices have been labelled. During iteration  $s = \{1, 2, 3, ...\}$  all vertices that are connected to  $v_{src}$  through a shortest path of s-1 edges are coloured with the same colour  $c_{src}$  and the vertices at distance s are flagged as active in the frontier array. Only vertices that are flagged as active are processed during an iteration of the kernel. A new breadth-first search is started for every vertex that has not been coloured during one of the previous searches and is thus in a different, disjoint component.

Performance: It takes exactly d+1 iterations to label all vertices of a connected component, where d is the diameter of the component. Furthermore, it takes |C| breadth-first searches to label the whole graph, where |C| is the number of disjoint components. Because this kernel is based on a breadth-first search, it performs better when the number of components is low and the degree is uniformly high, as this means that the number of active vertices processed during an iteration increases more quickly than for a lower degree, utilising more of the processing units available in the CUDA device. However, it turns out that this kernel performs much worse than the other CUDA implementations for almost every type of graph as the results section shows. We will therefore not cover it in as much detail as the other kernels in this article.

The use of different data structures and optimisation techniques means that the resource usage differs

**Algorithm 4** The CUDA specific optimisation techniques used for Kernel 2. It shows the use of the shared memory and texture caches.

```

//the one-dimensional texture reference

texture < int , 1, cudaReadModeElementType> arcsTexRef;

cudaBindTexture(0, arcsTexRef, d_arcs, nArcs * sizeof(int));

_shared_ bool localChanges;

if (threadIdx.x == 0) { //the first thread in the block}

localChanges = false;

//load the start index of the adjacency-list into shared memory

_shared_ int arcListIndices[64]; //the block size is 64

if (tid \ll nVertices) { //tid is the unique thread ID

arcListIndices[threadIdx.x] = vertices[tid];

--syncthreads();

int arcListEndIdx;

if (threadIdx.x < blockDim.x - 1) { //all but the last thread in the block

arcListEndIdx = arcListIndices[threadIdx.x + 1]; //read from shared memory

arcListEndIdx = vertices [tid + 1]; //read from global memory

}

for (int arcIdx = arcListIndices[threadIdx.x];

arcIdx < arcListEndIdx; ++arcIdx) { //iterate over the adjacency-list

// do a texture fetch to get the ID of the neighbour

int nbrId = tex1Dfetch(arcsTexRef, arcIdx);

/\!/ compare the colours of this vertex and its neighbour

}

_syncthreads();

if (localChanges && threadIdx.x = 0) { //set the global flag if necessary

*globalChanges = true;

```

among the kernels. Table 1 lists these differences.

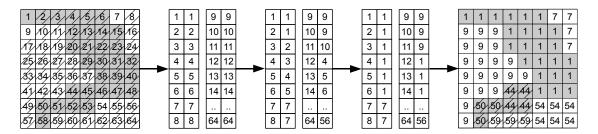

# 5. Hypercubic Mesh Graphs

A d-dimensional hypercubic mesh can be thought of as a graph with a very simple and regular structure where each vertex is connected to 2d neighbours. The data structure for storing such hypercubic meshes is usually a simple array and the connected neighbour addresses can be explicitly calculated rather than stored. Labelling these hypercubic meshes no longer takes the form of finding groups of vertices that are connected together (as all vertices in the mesh are ultimately connected) but instead finding connected groups of vertices that share some common property or fulfill some requirement. This subset of general graph labelling is applicable to any connected-component labelling (CCL) problem where the data conforms to a hypercubic mesh structure such as domain counting in field equation simulations and in the d=2 case can be used for image partitioning and computer vision.

As hypercubic meshes have a very regular and strict structure, labelling algorithms can be optimised to

Table 1: The resource usage of Kernels 1, 2 and 3 for arbitrary graphs (CUDA 2.1). None of the kernels uses any local memory or constant program variables. A link is either an undirected edge (Kernel 1) or a directed arc (Kernels 2 and 3), depending on the way the kernel represents the connections between vertices. The performance with different block sizes was measured for all multiples of 32 up to 512 and the best one was selected. This may be different on other hardware than our NVIDIA GTX260.

|                                          | Kernel 1 | Kernel 2 | Kernel 3 |

|------------------------------------------|----------|----------|----------|

| Global device mem. per vertex (Bytes)    | 4        | 10       | 10       |

| Global device mem. per link (Bytes)      | 8        | 4        | 4        |

| Other global device mem. (Bytes)         | 1        | 5        | 5        |

| Shared mem. per thread block (Bytes)     | 33       | 304      | 53       |

| Register usage per thread                | 4        | 9        | 5        |

| Compiler generated constant mem. (Bytes) | 8        | 12       | 12       |

| Thread block size                        | 32       | 64       | 192      |

take advantage of this structure. This is especially useful for GPU programs as their performance depends heavily on minimal branches and regular memory access. As the exact number of neighbours along with their position in memory is known, more efficient memory access patterns can be created allowing the speed of the labelling process to be greatly increased. We present, discuss and compare several hypercubic mesh labelling implementations on GPUs using NVIDIA's CUDA.

# 5.1. Connected-Component Labelling Hypercubic Meshes

Connected-component labelling algorithms in the 2-dimensional case have been widely studied for their use in image partitioning. Image partitioning is extremely useful in pattern recognition, computer vision and scientific simulation analysis. The real-time requirements of such applications continues to push the requirements for image partitioning algorithms to execute in the minimum time possible. Much of the research into two-dimensional CCL algorithms has been focused on optimising CPU CCL algorithms. Wu et al [30] present a detailed description of CPU CCL algorithms and their optimisations that allow for very fast labelling of images. These algorithms can easily be extended to find connected components in higher-dimension meshes. In general, CCL algorithms can be classified as: Multi-pass, Two-pass or One-pass [30].

Multi-Pass algorithms operate by labelling connected components over multiple iterations. These algorithms usually perform some local neighbour operations during scans through the mesh. The operations take the form of setting the label of the cell to the lowest label of the neighbours or record an equivalence between two labels. The performance of the multi-pass algorithms is highly dependent on the number of iterations through the data. However, some methods require very few iterations. The multi-pass method described in [31] has been shown to label 512x512 images in no more than four scans.

Two-Pass methods work by detecting equivalences, resolving equivalence chains and then assigning a final label to each cell. The Scanning phase performs a single iteration through the image examining the neighbouring cells and recording equivalences between labels. The Analysis phase resolves equivalence chains (sequences of equivalent labels) to find the correct final label for each label. The Labelling phase scans through the image looking up the current label in the equivalence table and assigning it the correct final label. These methods generally have very high performance as they must scan through the data only twice. However, the performance is very dependent on how quickly the Analysis phase can resolve the label equivalences. Storing an entire equivalence structure is also very memory consuming.

One-Pass is the last method of labelling. It works by scanning through the image until it finds a cell that does not yet have a label assigned to it. When one is discovered, it is assigned a new label and will then assign the same label to all the cells that are connected to it. This method has the advantage of only requiring one pass through the data, however, it does require irregular data access patterns to assign labels to connected cells (this is often performed recursively). This process of assigning label significantly reduces the performance of the algorithm and in general causes one-pass algorithms to be slower than the other two methods.

These classifications of CCL algorithms applies to both CPU and GPU implementations. We expect to find a difference in the optimal method for GPUs as compared to CPUs because the cost of parallel GPU iteration through the mesh should be less than a serial CPU iteration. Some implementations of CCL methods are also not possible on GPU due to the extra memory restrictions and parallel nature of GPU architectures. We have implemented and tested several GPU CCL algorithms to determine the optimal approach for GPU CCL.

### 5.2. CUDA Implementations

As many scientific applications are being moved onto the GPU, we wish to perform CCL on the GPU without having to copy it back to the CPU. Thus we wish to find the fastest CCL algorithm for GPUs. We expect that a multi-pass method such as the one described by Suzuki Et Al in [31] may execute faster on a GPU than a two-pass method because of the parallel nature of GPUs. Because an iteration through the data can be performed faster on a GPU than on a CPU, performing several iterations is no longer as much of an issue. The larger memory requirements and more irregular memory access of a two-pass labelling method will have a larger impact on the performance of a GPU algorithm than on a CPU because GPUs are highly optimised for regular memory transactions. We implement several multi-pass methods as well as a two-pass method and compare their results.

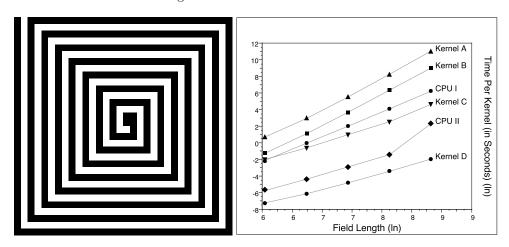

As hypercubic meshes have clearly defined structures and neighbours, there is no need to store neighbour lists separately. Instead the position of a cell's neighbours can be calculated explicitly. We can also make use of specialised memory types available on the GPU to improve memory access. In our previous work [29] it was shown that the optimal memory type to use for simulating field equations is the texture memory type. The texture memory type uses an on-chip memory cache that caches values from global memory in the spatial locality. This allows threads that access the values from memory in the same spatial locality to read from the texture cache rather than the slow global memory. The memory access patterns for CCL algorithms are very similar to the patterns for a field equation simulation and texture memory was found to perform the fastest for all CCL algorithms. Only the texture memory implementations of the Kernels are discussed.

# 5.2.1. Kernel A - Neighbour Propagation

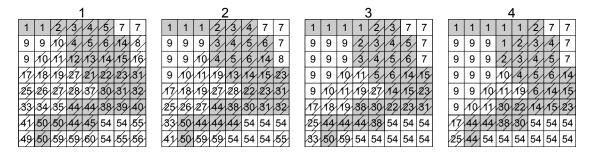

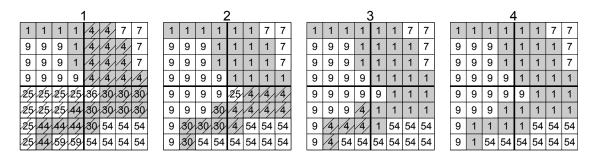

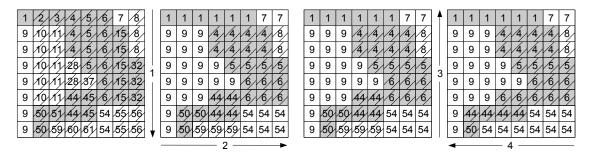

Figure 6: Four iterations of the Neighbour Propagation algorithm. The colour shows the field state of the cell, the number shows the current label assigned to each cell. The lines through the cell shows that the cell does not yet have the correct final label.

Kernel A implementations a very simple multi-pass labelling method. It parallelises the task of labelling by creating one thread for each cell which loads the field and label data from its cell and the neighbouring cells. The threads will then find the cell with the lowest label and the same state as its allocated cell. If the label is less than the current label, the cell will be updated with the new lower label. Figure 6 shows several iterations of this algorithm.

For each iteration, each cell will get the lowest label of the neighbouring cells with the same property. The kernel must be called multiple times until no label changes occur, then it is known that every cell has been assigned its correct final label. To determine if any label has changed during a kernel call, a global

**Algorithm 5** The algorithm for the host and the kernel for the Neighbour Propagation CCL method. The host will call the kernel until  $m_d$  is not set to true at which point the mesh will have the correct labels.

```

function Mesh_Kernel_A_Host(D_d, N)

declare integer L_d[N]

do in parallel on the device using N threads: initialise L_d[0...N-1] such that L_d[i] \leftarrow i

declare boolean m_d in device memory

do in parallel on the device using N threads: call Mesh_Kernel_A(D_d, L_d, m_d)

until m_d = \text{false}

return

function Mesh_Kernel_A(D_d, L_d, m_d)

declare integer id, id_n, label in local memory

declare integer n_{id}[dim \times 2] in local memory

id \leftarrow \text{threadID \& blockID from CUDA runtime}

n_{id} \leftarrow hypercubic neighbours of id where the cells have the same state

label \leftarrow L[id]

for all id_n \in n_{id} do

if L[id_n] < label then

label \leftarrow L[id_n]

m_d \leftarrow true

end if

end for

L[id] \leftarrow label

return

```

boolean is used. If a kernel changes a label it will set this boolean to true. The host program can then examine this boolean value to determine if another iteration of the algorithm is required. The host and device algorithms for this method can be seen in Algorithm 5.

Kernel A requires many iterations to label a mesh because a label can only propagate itself by a maximum of one cell per iteration. When there are large clusters in the mesh, the algorithm will require many iterations to label the entire mesh.

# 5.2.2. Kernel B - Local Neighbour Propagation

Figure 7: Four iterations of the Local Neighbour Labelling algorithm. In this case the field is split into four blocks indicated by the heavy lines. Cells that are crossed out are yet to receive their final label.

Kernel B is an improved version of Kernel A that allows labels to propagate themselves faster through a cluster by making use of Shared-Memory. Initially the threads fetch their cell's label and the labels of all four neighbours from global memory and choose the lowest of these (the same process as Kernel A). Instead of returning here, the threads then write these values into shared memory. The kernels then loop through

Algorithm 6 The algorithm for Kernel B performing the Local Neighbour Propagation CCL method.

```

function Mesh_Kernel_B(D_d, L_d, m_d)

declare integer id, id_L, label in local memory

declare integer n_{id}[dim] in local memory

id \leftarrow \text{threadID \& blockID from CUDA runtime}

n_{id} \leftarrow hypercubic neighbours of id where the cells have the same state

label \leftarrow L_d[id]

for all id_n \in n_{id} do

if L_d[id_n] < label then

label \leftarrow L_d[id_n]

m_d \leftarrow true

end if

end for

declare integer L_L[blockDim] in shared memory

declare boolean m_L in shared memory

id_L \leftarrow \text{threadID from CUDA runtime}

n_{id} \leftarrow \text{neighbours of } id_L \text{ where the cells have the same state}

repeat

L_L[id_L] \leftarrow label

synchronise block

m_L \leftarrow \text{false}

for all id_n \in n_{id} do

if L_L[id_n] < label then

label \leftarrow L_L[id_n]

m_L \leftarrow true

end if

end for

synchronise block

until m_L = \text{false}

L_d[id] \leftarrow label

return

```

updating the labels within shared memory until they stop changing. For each iteration of this loop the kernels will load the neighbours' labels from shared memory and choose the lowest appropriate label (see Algorithm 6). This effectively performs the entire labelling algorithm on each block at a time. The labels for four iterations of the kernel can be seen in Figure 7. Note that the host code for Kernel B is effectively the same as for Kernel A.

As the labels on the borders of the block will change, multiple calls will be required for the entire mesh to be correctly labelled. However, Kernel B will require less iterations than Kernel A (although each kernel call will take longer). However, Kernel B is still limited in that a label can only propagate by the size of a block each iteration (Our block size is 16x16). For a large mesh where the use of GPUs is necessary (eg. 4096x4096), this can still require many kernel calls.

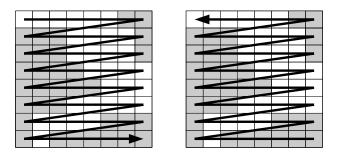

#### 5.2.3. Kernel C - Directional Propagation Labelling

Kernel C is designed to overcome the problem that a label can only propagate itself by one cell per iteration (Kernel A) or one block per iteration (Kernel B). Kernel C achieves this by breaking away from the method of allocating one thread to each cell. Instead, each thread is allocated a row (that is a row of cells in any of the dimensions of the hypercubic mesh). Each thread will iterate through this row propagating the lowest label along the row. By iteratively calling 2d such kernels (one going each direction for each dimension) the program can propagate the lowest labels through the mesh. See Figure 8.

Figure 8: One iteration of the Directional Propagation Labelling algorithm, one pass for each direction in each dimension. Crossed out cells currently have an incorrect label.

Each thread will calculate its unique position (with the dimension of iteration set to either 0 or N-1 depending on direction) and then iterate through the row. For each cell it will check to see if the last cell had the same state and if its label was lower, if this condition occurs the current cell will be assigned the last cell's label. This algorithm is described in detail in Algorithm 7.

**Algorithm 7** The Kernel to iterate through the I<sup>th</sup> dimension of a hypercubic mesh. This function must be called once for each direction in each dimension. Once all functions no longer set  $m_d$  to true, the mesh will be correctly labelled.

```

function Mesh_Kernel_C(I, D_d, L_d, m_d)

declare integer id, label in local memory

id \leftarrow \text{threadID } \& \text{ blockID from CUDA runtime}

label \leftarrow L_d[id, 0] \ / [id, 0] \text{ indexes the array at } id \text{ with the } I^{th} \text{ dimension component set to } 0.

for n \leftarrow 1 to N - 1 do

if (D_d[id, n] = D_d[id, n - 1]) \&\& (label < L_d[id, n]) then

L_d[id, n] \leftarrow label

m_d \leftarrow true

else

label \leftarrow L_d[id, n]

end if

end for

return

```

# $5.2.4.\ Kernel\ D$ - Label Equivalence

Kernel D is a multi-pass algorithm that records and resolves equivalences. However, unlike a two-pass algorithm this method does not record an entire equivalence table. Instead the kernel will record the lowest (and the most likely) label that each label is equivalent to. This reduces the memory complexity of the method while still allowing the equivalences to be resolved with a small number of iterations (4096x4096 systems were labelled in 9 or less iterations). This method is similar to the CPU algorithm described by Suzuki Et Al in [31].

As with Kernel A and B, one thread is created for each cell. Each thread will examine the neighbouring labels and if it finds that it is next to a lower label, it will put that lower label into the equivalence list if the label is lower than the value currently in the list. At the end of this kernel call, the equivalence list will have a list of labels and the lowest other label that they are directly neighbouring. See Algorithm 8.

The problem with this is that there will be equivalence chains, i.e. 16 is equivalent to 12 which is equivalent to 4 and so on. So there is another kernel that will resolve the equivalence lists so that the list will store the real lowest equivalent label. As each cell has a unique label at the start of the process, one thread is launched for each cell (which is the same as one thread for each initial label). These threads will

Algorithm 8 The algorithms for the host code and the three phases of Kernel D: Scanning, Analysis and Labelling.

```

function Mesh_Kernel_D_Host(D_d, N)

declare integer L_d[N], R_d[N]

do in parallel on the device using N threads: initialise L_d[0...N-1] such that L_d[i] \leftarrow i

do in parallel on the device using N threads: initialise R_d[0...N-1] such that R_d[i] \leftarrow i

declare boolean m_d in device memory

repeat

do in parallel on the device using N threads: call Mesh_Kernel_D_Scanning_Phase(D_d, L_d, R_d, m_d)

do in parallel on the device using N threads: call Mesh_Kernel_D_Analysis_Phase(D_d, L_d, R_d)

do in parallel on the device using N threads: call Mesh-Kernel-D-Labeling-Phase (D_d, L_d, R_d)

until m_d = \text{false}

return

function Mesh_Kernel_D_Scanning_Phase(D_d, L_d, R_d, m_d)

declare integer id, label_1, label_2 in local memory

declare integer n_{id}[dim] in local memory

id \leftarrow \text{threadID \& blockID from CUDA runtime}

n_{id} \leftarrow neighbours of id where the cells have the same state

label_1 \leftarrow L_d[id]

label_2 \leftarrow MAXINT

for all id_n \in n_{id} do

\min(label_2, L_d[id_n])

end for

if label_2 < label_1 then

atomicMin(R_d[label_1], label_2)

m_d \leftarrow true

end if

return

function Mesh_Kernel_D_Analysis_Phase(D_d, L_d, R_d)

declare integer id, ref in local memory

id \leftarrow \text{threadID} \& \text{blockID} \text{ from CUDA runtime}

if L_d[id] = id then

ref \leftarrow R_d[id]

repeat

ref \leftarrow R_d[label]

until ref = R_d[label]

R_d[id] \leftarrow ref

end if

return

function Mesh_Kernel_D_Labeling_Phase(D_d, L_d, R_d)

declare integer id

declare integer ref in local memory

id \leftarrow \text{threadID \& blockID from CUDA runtime}

L_d[id] \leftarrow R_d[L_d[id]]

return

```

Figure 9: A single iteration of the Label Equivalence method. From left to right: the initial scan and initial equivalence list, the list after the scan, the list after analysis and the mesh after labelling from the equivalence list. Crossed out lines indicate cells that have do not yet have their final label.

retrieve the label currently assigned to that cell, it will then check to see if the label that cell has is the same as the label that would have been initially assigned to it. If the label is same then that thread is considered to own that label and will resolve the equivalence chain, if not it will simply return. The thread must then expand the equivalence chain to discover what the real lowest label it is equivalent to is. It will look up its label in the equivalence list and find the label it is equivalent to, it will then look up this label. This is repeated until the label it looks up in the list is equivalent to itself, this will be the lowest label in the equivalence chain. Once this value is found it overwrites the equivalence list with this value. See Algorithm 8.

This process sounds computationally expensive, however, most threads will not need to expand a long equivalence list. If a thread in the equivalence chain has already expanded and overwritten the equivalence list, other threads that have that value in their chain will not need to expand the entire chain as some part of it has already been done. While the order in which CUDA executes the threads is not controllable, the order of execution is known and repeatable. The scheduler assigns blocks to multiprocessors in order of block number. In general the threads with lower id's will be executed first and thus the equivalence list resolution process will remain relatively fast.

Once the equivalence chains have been expanded, the final stage of the labelling process can take place. One thread for each cell will be launched that will read that cell's label. Look up the label in the equivalence list and then assign the equivalent label to the cell. See Algorithm 8.

This process cannot label the entire mesh in a single pass and several iterations will be required. However, its method of combining labels rather than cells allows it to process large meshes with very few iterations. The advantage of this method over a two-pass system is that it does not require a large equivalence matrix (which uses too much memory) or linked-list processing (which is infeasible on a GPU).

### 5.3. CPU Implementations

Figure 10: The alternating raster scan patterns used by the CPU I method.

For comparison purposes we have also implemented two hypercubic mesh CCL algorithms on the CPU. These two algorithms are serial implementations of the algorithms we have previously discussed. The method

Table 2: This table gives a brief overview of the different CUDA implementations.

### **Arbitrarily Structured Graphs**

**Kernel 1**: Operates on the edge set. Compares the colour values of the two vertices connected by an edge and updates the higher one using atomicMin.

Kernel 2: Operates on the vertices and their adjacency-lists. Uses a frontier array to flag vertices whose colour has been been changed in one iteration to be processed in the next iteration. When being processed, a vertex compares its colour value to those of its neighbours and updates the higher one using atomicMin.

**Kernel 3**: Performs one breadth-first search for every connected component in the graph. Starting with a single vertex, it spreads the colour to all other vertices in the same component, processing all vertices at distance s-1 from the source during iteration s.

# Hypercubic Mesh Graphs

Kernel A: Neighbour Propagation - Each iteration selects the lowest neighbouring label for each cell.

Kernel B: Local Neighbour Propagation - Each iteration resolves the labels within a block.

Kernel C: Directional Propagation - Each iteration propagates labels in a single direction.

**Kernel D**: Label Equivalence - Each iteration resolves the lowest (most likely) label equivalence chain and assigns all cells in the chain the final label.

CPU I is simply an alternating raster scan which updates the labels based on each cell's neighbours. The raster scan directions are alternated each iteration to ensure that labels are propagated in all directions. See Figure 10. This raster scan CPU method is the CPU equivalent of Kernels A-C as it performs neighbour comparison operations each step (as with Kernels A & B) and the alternating scan directions are similar to the directional propagation method of Kernel C.

The labelling method CPU II uses the same algorithm as Kernel D, but simply finds and resolves the equivalences in serial on the CPU. Serial processing provides no advantage in the scanning or labelling phase, but can be more efficient in the analysis phase as the equivalence chains will never be more than two equivalences long. This method of labelling is very similar to the one described by Suzuki et al in [31]. Although this method is not as fast as some CPU implementations of two-pass algorithms, it still provides a useful benchmark for comparing the GPU labelling methods.

### 6. Performance Results

We now analyse the performance of the CUDA kernels and CPU reference implementations and compare them with each other. Table 2 briefly summarises the different implementations. Section 6.1 describes the test graphs used for the arbitrary graph performance analysis, which is given in Section 6.2. The results for the hypercubic mesh graphs are analysed in Section 6.3.

The system used for the performance measurements has the following configuration: An Intel Core2 Quad CPU running at  $2.33 \mathrm{GHz}$  and  $4 \mathrm{GB}$  of DDR2-800 system memory ( $\approx 2.8 \mathrm{GB}$  accessible due to the use of a 32-bit operating system) with an NVIDIA GeForce GTX260 graphics card which has 216 CUDA cores and 896MB of device memory. The Linux distribution Kubuntu 8.10 is used as the operating system. Version 2.1 of the CUDA toolkit and the corresponding developer drivers 180.22 for the GPU are installed on this system.

#### 6.1. Arbitrary Test Graphs

A number of graph instances are used to compare the performance of the CUDA kernels and to see how well they hold up against the CPU algorithm. Table 3 gives an overview of the graph properties.

**Disjoint** This algorithm generates graphs with a specified number of major components. Vertices are assigned to these sets at random. Edges are created between randomly selected vertices from the same set. This is a variant of the Erdős-Rényi method of generating random graphs that differs in the initial partitioning of the vertices into different sets. The resulting graph has at least the specified number of

Table 3: This table lists the properties of the graphs that are used to analyse the performance of the different labelling algorithms. Disjoint 1 and 2 have 100 major components, most of the other components that are found in some of their graph instances are monomers (i.e. vertices with no neighbours). The line, scale-free and Watts-Strogatz (W-S) graph instances consist of only one component. They are used to determine how well the algorithms perform when they are used to verify that a graph is fully-connected. Furthermore, Barabási's scale-free and Watts-Strogatz's small-world graphs are well known network models that have been studied in many scientific publications and are therefore of particular interest. The abbreviation m stand for "millions".

|                 | Vertices                    | Edges                         | Average  | Components  |

|-----------------|-----------------------------|-------------------------------|----------|-------------|

|                 |                             |                               | Degree   |             |

| Disjoint 1      | 2m-16m                      | $50 \mathrm{m}$               | 6.3 - 50 | 100 - 31044 |

| Disjoint 2      | $1 \mathrm{m}$              | $10\mathrm{m}{-}60\mathrm{m}$ | 20 - 120 | 100         |

| Disjoint 3      | $5 \mathrm{m}$              | $60 \mathrm{m}$               | 24       | 1 - 1000019 |

| Line            | 0.2 m - 1 m                 | $0.2\mathrm{m}{-1\mathrm{m}}$ | 2        | 1           |

| Scale-free      | $1\mathrm{m}{-5\mathrm{m}}$ | $5\mathrm{m}{-}25\mathrm{m}$  | 10       | 1           |

| W-S, $p = 0.01$ | 2m-14m                      | $10\mathrm{m}{-}70\mathrm{m}$ | 10       | 1           |

| W-S, $p = 0.1$  | 2m-14m                      | $10\mathrm{m}{-}70\mathrm{m}$ | 10       | 1           |

| W-S, $p = 1.0$  | 2m-14m                      | $10\mathrm{m}{-70\mathrm{m}}$ | 10       | 1           |

components. It can have more components, most of them consisting of only one vertex (monomers). This is more likely to be the case when the number of edges in relation to the number of vertices is small.

Three different tests are performed with this algorithm, listed in the table as Disjoint 1, 2 and 3. The first one varies the number of vertices in the graph, while keeping the number of edges (50,000,000) and major components (100) fixed. The second one varies the number of edges, while keeping the number of vertices (1,000,000) and major components (100) fixed. And Disjoint 3 varies the number of major components  $(10^0,10^1,\ldots,10^6)$ , while keeping the number of vertices (5,000,000) and the number of edges (60,000,000) fixed.

Line A line graph is a simple one-dimensional graph where every vertex is connected to the vertex before and after itself. The first and last vertex are the only exceptions with only one neighbour. A line is the graph with the highest possible diameter d = |V| - 1. And as described in Section 4.3, the performance of the CUDA algorithms proposed in this paper is heavily dependent on the graph diameter. The line graph is the worst case scenario for them.

Scale-free networks have a power-law degree distribution for which the probability of a node having k links follows  $P(k) \sim k^{-\gamma}$  [32]. Typically, the exponent  $\gamma$  lies between 2 and 3 [33, 27]. Such a graph has a small number of vertices with a very large degree, also called the hub nodes, while most other vertices have a relatively small degree. The algorithm implements the Barabási-Albert model of gradual growth and preferential attachment described in [32], where new vertices are gradually added to the graph and connected to the already present vertices with a probability that is based on the degree of those vertices.

Watts-Strogatz The Watts-Strogatz (W-S) small-world network model described in [34] is often used in the literature. It starts off with a regular graph where every vertex is connected to its k nearest neighbours. Then, one end of each edge is randomly rewired with probability p, considering every edge exactly once. The rewired edges are shortcuts or "long-distance" links in the graph. For a large range of p, W-S have shown that the resulting networks have a high clustering coefficient and a small path length, which are characteristic properties of small-world networks.

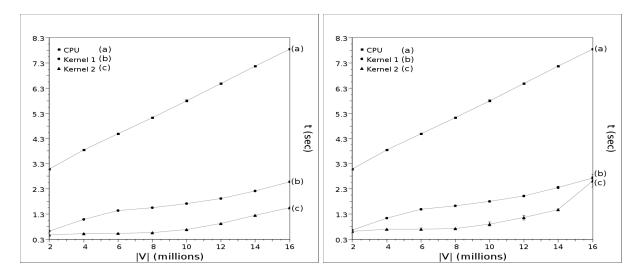

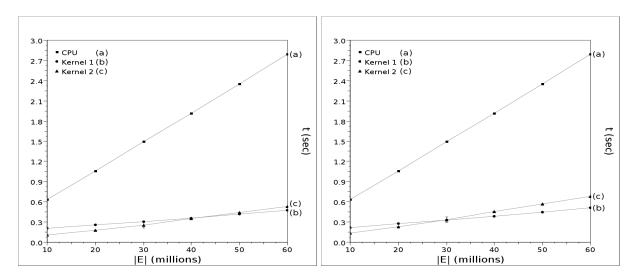

#### 6.2. Arbitrary Graph Performance Analysis

This section discusses the performance of the different graph labelling algorithms using the graph instances described in the previous section as test cases. Each data point shown in the result plots given in Figures 11 to 17 is the mean value of 30 measurements. The error bars illustrate the standard deviation from the mean. The performance results for Kernels 1 and 2, as well as for the CPU reference implementation, are shown for all of the graph instances. The implementation of Kernel 3 is much slower than the other approaches for all graphs with the exception of the line graphs. Its results have been omitted from all other

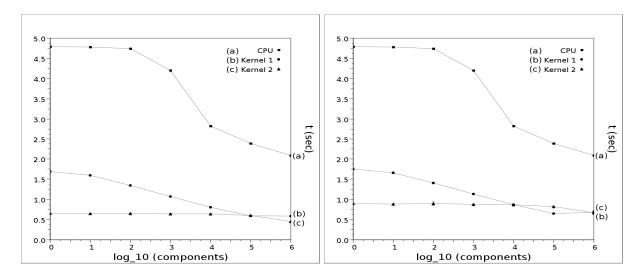

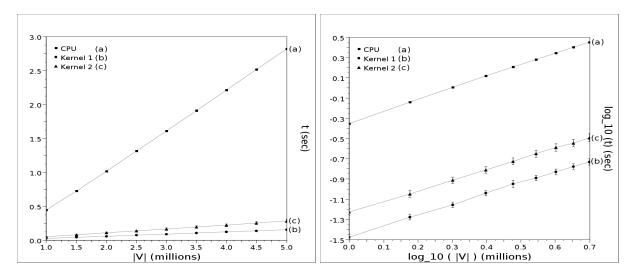

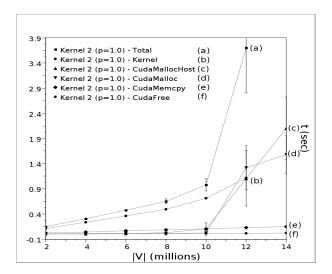

Figure 11: The execution times t measured to process the **Disjoint 1** graphs excluding (left) and including (right) memory allocation, deallocation and host  $\leftrightarrow$  device memory copies. The number of vertices |V| increases from 2,000,000 – 16,000,000. The number of edges and major components is set to 50,000,000 and 100 respectively. The execution times for Kernel 3 are in the range from  $\approx 20-229$  seconds.

result plots as they would otherwise dominate the plots and the performance differences between Kernels 1 and 2 and the CPU algorithm would get lost.

Most of the figures described in this section show two result plots. They illustrate, unless specifically mentioned otherwise, the CUDA kernel execution times without (left) or with (right) the time taken for device memory allocation, deallocation and memory copies between the host and device. The kernel execution times by themselves are of particular interest if the labelling algorithm is used in conjunction with other CUDA kernels that modify or analyse the same graph instance, which means that the data is already on the device. The plot on the right, on the other hand, is more relevant if only the component labelling is done on the device, which means that the graph data has to be copied to device memory before it can be processed.

Figure 11 illustrates the graph labelling performance for the **Disjoint 1** graphs. The results demonstrate how even large graphs can be labelled in a matter of seconds. When it comes to the raw labelling performance, then Kernel 2 can clearly finish the task in the shortest amount of time. This is also true when the time for memory allocation, deallocation and host  $\leftrightarrow$  device memory copies is included. Only at the last data point, where |V| = 16,000,000 (total device memory usage 443MB for Kernel 1 and 534MB for Kernel 2), does the mean value of the measurements of Kernel 2 make a sudden jump. The results are also much more spread out then before, as illustrated by the larger error bar. This behaviour can also be observed on some of the following result plots and will be discussed at the end of the section.

**Disjoint 2** keeps the number of vertices consistently at 1,000,000, but increases the number of edges added between these vertices and therefore the average degree k of the graph instances. The performance measurements are illustrated in Figure 12. While Kernel 2 again shines for low degrees, Kernel 1 can outperform it once k exceeds  $\sim 90$  when excluding and  $\sim 55$  when including the memory allocation and copy times. Kernel 1 operates on the edge set E, whereas Kernel 2 operates on the arc sets that make up the adjacency-lists of the individual vertices. Even though Kernel 1 can not use some of the optimisation techniques used in Kernel 2, like the frontier array or texture fetches, it makes up for this once the degree is high enough by only having to traverse half as many connections than Kernel 2.

The performance measurements for **Disjoint 3**, illustrated in figure 13, show how the number of major components  $(10^0, 10^1, \dots, 10^6)$  effects the execution times of the algorithms. The number of vertices and edges is kept consistent at 5,000,000 and 60,000,000 respectively. Both the CPU algorithm and Kernel 1 finish the tasks significantly faster for a large number of components in the graph. The more components, the

Figure 12: The execution times t measured to process the **Disjoint 2** graphs excluding (left) and including (right) memory allocation, deallocation and host  $\leftrightarrow$  device memory copies. The number of edges |E| increases from 10,000,000-60,000,000. The number of vertices and major components is set to 1,000,000 and 100 respectively. The execution times for Kernel 3 are in the range from  $\approx 9.8-11.2$  seconds.

Figure 13: The execution times t measured to process the **Disjoint 3** graphs excluding (left) and including (right) memory allocation, deallocation and host  $\leftrightarrow$  device memory copies. The number of major components increases from  $10^0, 10^1, \dots, 10^6$ . The number of vertices and edges is set to 5,000,000 and 60,000,000 respectively. The execution times for Kernel 3 are in the range from  $\approx 47-1515$  seconds.

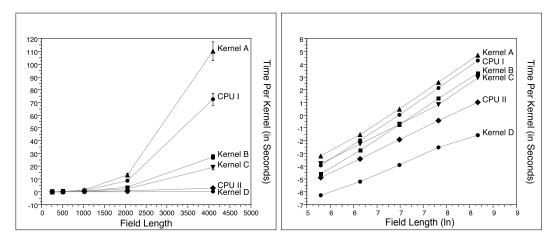

Figure 14: The execution times t measured to process the **Line** graphs (left). Because the CUDA kernel execution times are so high and the graphs are rather small (compared to the other graphs used for the performance measurements), the device memory operations do not change the results in any significant way. The timing results increase logarithmically with the order of the graph |V| (right), which increases from 200,000-1,000,000. The slopes of the least square linear fits to the data sets on the logarithmic plot, rounded to two significant digits, are:  $CPU \approx 1.00$ , Kernel  $1 \approx 1.76$ , Kernel  $2 \approx 1.77$  and Kernel  $3 \approx 1.57$ . This is the only graph type where Kernel 3 performs better than the other CUDA kernels. However, the CPU algorithm takes  $\ll 1$  second for all measured graphs of this type, beating the CUDA kernels by far.

less vertices are in each component, which means the component diameters are smaller too. The execution times of Kernel 2 are much less effected by the number of components. Interestingly, the decrease of the execution times of Kernel 1 mostly stops at  $\sim 10^5$ , whereas the range from  $\sim 10^5$  to  $10^6$  is where the execution times for Kernel 2 begin to decrease more noticeably.

The results for the **Line** graphs are shown in Figure 14. As mentioned before, this is the worst case scenario for the CUDA kernels, because the diameter d of the graph is equal to N-1. This requires the kernel to be called up to N times. The CPU implementation, on the other hand, can very quickly propagate the colour in N-1 recursive calls from the first vertex to the last vertex.

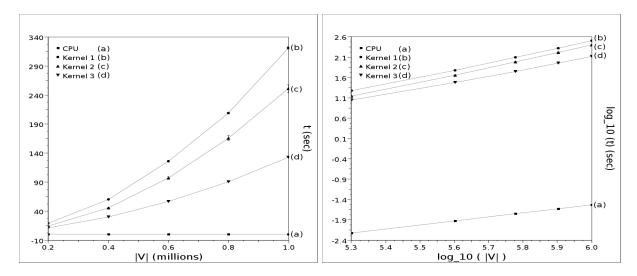

Figure 15 illustrates the performance measurements for the **Scale-free** graphs generated with Barabási's model. Kernel 1 and 2 both finish the labelling tasks considerably faster than the CPU implementation and scale well with the network size. The device memory allocation and host  $\leftrightarrow$  device memory copies do not change the outcomes significantly.

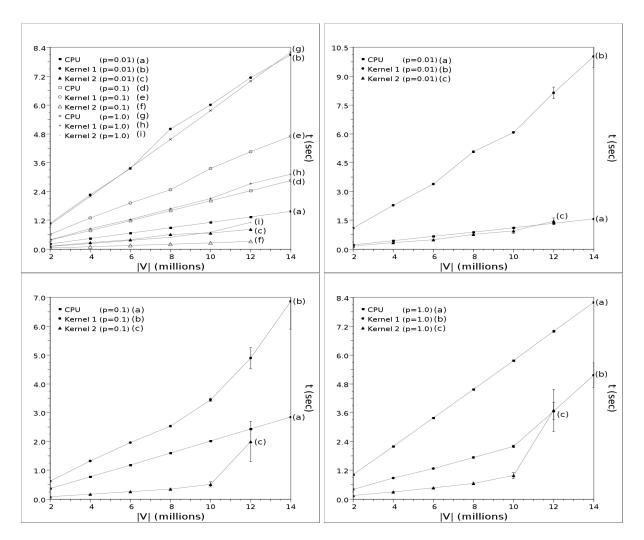

Figure 16 illustrates the performance results for the **Watts-Strogatz** graphs for three different rewiring probabilities. The CPU algorithm performs well for small values of p, but gets worse with increasing randomness, whereas Kernel 1 behaves the other way around. Data pre-fetching techniques employed by the CPU work better on regular, more predictable graphs than on the random data accesses that occur more frequently the higher the value of p is. Kernel 1, on the other hand, is much less affected by the storage locations of the vertices that form the end points of an edge. And it benefits a lot from the long-distance links created by rewiring edges, as these reduce the diameter of the graph.