# Semi-automatic Validation of Cycle-Accurate Simulation Infrastructures: The Case for gem5-x86

Juan M. Cebrian<sup>1</sup>, Adrián Barredo, Helena Caminal, Miquel Moretó, Marc Casas, Mateo Valero

Barcelona Supercomputing Center (BSC), Barcelona, Spain

# Abstract

Since the early 70s, simulation infrastructures have been a keystone in computer architecture research, providing a fast and reliable way to prototype and evaluate ideas for future computing systems. There are different types of simulators, from most detailed (cycle-accurate) to time-based/functional and analytical modeling. Increasing accuracy translates into several orders of magnitude in terms of simulation speed. Yet, a question remains open: are the results derived from the simulation infrastructure representative of a real machine?

Validation of these infrastructures is complex and costly, usually performed upon release. However, most simulators do not provide the appropriate means to verify or validate new architectural models. In this paper, we introduce a semiautomatic validation framework based on real-hardware performance counter information. The framework provides two levels of abstraction: a) a high level definition of the processor behavior (Top-Down model) and b) detailed perstructure and per-pipeline-stage usage breakdown to pinpoint simulator issues. We used this framework to validate the latest available gem5-x86 simulation environment, and found several sources of error that alter the expected behavior of the simulated processor, which we were later to document and correct.

© 2020 Elsevier. This manuscript version is made available under the CC-BY-NC-ND 4.0 license http://creativecommons.org/licenses/by-nc-nd/4.0/

<sup>\*</sup>Juan M. Cebrian

Email addresses: jm.cebriangonzalez@gmail.com (Juan M. Cebrian), adrian.barredo@bsc.es (Adrián Barredo), helena.caminal@bsc.es (Helena Caminal), miquel.moreto@bsc.es (Miquel Moretó), marc.casas@bsc.es (Marc Casas), mateo.valero@bsc.es (Mateo Valero)

# 1. Introduction

In the last decade, the complexity of modern computer systems has reached unprecedented levels. Prototyping any system component is exceedingly expensive, forcing architects to rely on simulation to model and evaluate new ideas. Simulators produce quantitative estimates in a safe, timely and cost-effective manner. As a matter of fact, architecture researchers have increasingly relied on simulators over the years. Yi *et al.* [1] have classified the performance evaluation methods for papers appearing in the International Symposium on

- <sup>10</sup> Computer Architecture (ISCA) in six selected years. In the conference's inaugural year (1973), only two papers out of 28 (7.1%) were simulation-based, but that number steadily increased to 27.9% in 1985, 71.9% in 1993, 80% in 1997, and finally to 88% and 87% in 2001 and 2004, respectively. Modern simulators model multiple ISAs (instruction set architecture), CPU (central processing)

- <sup>15</sup> unit) types, interconnect topologies, and other devices with different levels of detail. Complete infrastructures are able to boot unmodified operating systems (OS), and even run interactive graphical workloads. To add further complexity to these systems, architects use a wide variety of methodologies, benchmarks and datasets on top of the simulated infrastructure.

<sup>20</sup> Current simulation speeds often limit the scope and depth of the work that can be performed. Simulation infrastructures can be classified based on the level of detail of the simulation as follows: cycle-level, time-based/functional and analytical modeling, from more to less accurate. Cycle-level accuracy is necessary when working with very specific hardware features that require a high level of

detail. Timing simulation and analytical modeling are key enabling techniques to explore the design space and to enable software development on unavailable hardware. Fast simulations of many-core processors at system level are critical, due to the need to emulate the behavior and communication of tens to hundreds of cores. Hybrid methodologies, like interval simulation, provide some balance

<sup>30</sup> between detailed cycle-accurate and time-based/functional simulation. This allows applications with long execution times to be modeled much faster, while still providing the necessary level of detail to observe core, memory, interconnect and system interactions.

In this paper we focus on cycle-level simulators, complex pieces of software that typically take hundreds of thousands of lines of code. Cycle-accurate simulators need to model each of the processor components as accurately as possible, updating state elements at every clock cycle. As a result, insightful information can be retrieved when running realistic applications and datasets. This is key to quantitatively estimate the usage and behavior of specific structures for

- <sup>40</sup> given sizes, and to design features or configurations in the micro-architecture. Cycle-accurate simulators also enable the evaluation of new hardware features and instructions, providing binary compatibility and enabling performance and energy studies, especially in hardware/software co-design. Unfortunately, this level of accuracy comes at a price: long simulation times and high development/-

- validation costs. Single-core cycle-accurate simulators can execute around 0.01 to 0.3 million instructions per second (MIPS), leading to simulation times of several days for a couple of minutes of application time.

In essence, while simulation is indubitably one of the most important tools available to computer architecture researchers, designers have to face trade-offs between performance, accuracy and flexibility that inherently lead to a certain

degree of experimental error. As a result, several important challenges arise regarding the simulation process that need to be addressed:

*Verification, validation and calibration.* Implementation and testing of a simulation infrastructure so that it accurately models a state-of-the-art proces-

sor is a tedious and laborious process. Formal verification (using specification languages) is usually reserved to simple embedded models, leaving ad-hoc techniques for complex processor models. Simulators are usually verified and validated before release by the developers and, upon release, by other institutions. Black and Shen [2] classified the different sources of simulation error into:

- a) Modeling errors: erroneous description of the desired functionality. b) Specification errors: the developer is unaware of the internal functionality being modeled.

c) Abstraction errors: the developer fails to implement certain details of the system being modeled. Modeling errors can be corrected, but, as years go by, the slow and infrequent updates often result in simulators that model un-

- realistic, buggy, or even obsolete computer architectures. Many researchers just take simulators "as provided", and do not spend time checking the correctness of the infrastructure built with new tool-chains, running new benchmarks, or validating a modified simulator to represent a system which was not originally intended to model. They do not consider either if abstraction or specification

- <sup>70</sup> errors, which may not affect overall application performance, produce unacceptable errors in their specific area of research. There is a real necessity to have a simple infrastructure to ensure that the cumulative errors do not lead to unreliable results over the years. There are also another two additional "sources of error" that are worth mentioning.

- Input datasets. Long simulation times may be an issue when using cycle-accurate infrastructures. One common "solution" is to use small input datasets to reduce simulation time. However, doing so may lead to different conclusions than studies performed using more realistic input sets, above all if simulated resources are not scaled accordingly. This is certainly true when simulating multi/many

- <sup>80</sup> core architectures in which synchronization heavily depends on workload distribution. Basically, not only do we need a simulator that models the target architecture in detail, it also must be driven by a realistic workload.

*Lack of features.* Computer architecture advances quickly and simulation infrastructures have difficulties to match all the architectural features introduced

<sup>85</sup> by different companies. This is usually due to their complexity and the lack of permanent developers/resources. While users may expect missing some modern processor features on the simulation infrastructure, they usually underestimate the impact it could have on their proposals (e.g., SIMD, prefetching, write buffers, etc.). Certain features can be critical for the performance of specific

<sup>90</sup> applications or per-structure behavior, and the lack of them can be a real issue. Researchers may propose some architectural changes to solve an issue that is no longer existent, or that can affect applications designed with modern features in mind. It is important to revisit simulator implementation/validation for stateof-the-art processors that are representative of modern systems and ensure they are able to capture the behavior of emerging workloads.

In this paper we address some of the above-mentioned issues, providing researchers with a semi-automatic infrastructure to analyze the resource requirements of different input workloads and to ease the validation process of cycle-accurate simulation infrastructures against real hardware. Our method-

- ology is based on performance counter information and the Top-Down Model approach [3]. Performance counter information is used, in essence, to define the processor behavior for a given workload and to detect hardware bottle-necks. Per-structure and pipeline performance counters are used to pinpoint the sources of error in the simulation infrastructure. We also provide a case

- study for gem5-x86, describing the bugs found and possible fixes, showing the final behavior. The "fixed" simulator improves both the accuracy of the results and the simulation speed for a relatively up-to-date revision of gem5-x86 (new  $\mu$ ops (Micro-operations) and reduced simulation stalls due to different sources of error). The framework will be made available upon publication for the research community [4].

The paper is organized as follows. Section 2 reviews the related work on simulation environments and validation alternatives. Section 3 describes the proposed validation framework. Section 4 describes the infrastructure and methodology used in the article. Section 5 presents a case study performed on gem5-x86.

<sup>115</sup> Finally, Section 6 summarizes the main conclusions and future work.

# 2. Related Work

Simulation infrastructures have become very popular since the late 90s, in a great effort from both the industry and the research community to improve the quality, accuracy and development/evaluation time of novel ideas.

120

Cycle-level simulators can be seen as high-level abstractions of RTL (registertransfer level) designs implemented over several thousands of lines of code. These complex systems model each of the processor components as accurately as needed, updating state elements at every clock cycle, so that insightful information can be retrieved when running realistic applications and datasets. M5 [5], gemsOpal [6], PTLsim [7] or MARSS [8] are examples of simulation 125 infrastructures that can achieve cycle-accuracy.

Time-based simulation provides a good trade-off between accuracy and simulation speed, processing most of the instructions from the application in a simplified way. MASE is an example of time-based simulation, which combines timing and functional modeling [9]. MASE was built on top of SimpleScalar, 130 one of the first trace-driven simulators available for the research community [10]. Asim or RSIM are other examples of the initial efforts to provide time-based and functional simulation infrastructures [11, 12]. More recently, Kang et al. [13] conducted an interesting survey on time-based and functional simulation infrastructures, extending the work done by Yi et al. [1], and classifying time-based 135

methods into different categories: • CPI-Based simulation (k-CPI). This methodology assumes that each instruction takes k cycles to execute them. A simplified model can assume

140

145

that each instruction requires one cycle to execute (1-CPI model). A more complex model can provide a different CPI value for each instruction or instruction group based on the processor's specification datasheet (datasheet model). k-CPI models can be easily built on top of functional simulators without sacrificing the simulation speed. Commercial processor simulators such as Imperas OVP [14] or Arm FastModels [15] use a k-CPIbased simulation approach. While k-CPI models are easy to understand

and fast to simulate, the accuracy of the results is far from real hardware measurements, especially for corner cases, since this model neglects the complex behavior of modern microprocessor architectures.

- Sampled simulation. Cycle-accurate simulation is performed over a subset of the instruction stream divided into "sampling units". The selection of the sampling units can be done randomly [16], periodically [17], or based on phase analysis [18, 19, 20]. The main issue of this approach is to guarantee that the sampling units properly represent computational and memory patterns of the whole application. Statistical methods can be applied to ensure this. Phase-sampling can be also handled at an application level, providing pre-processed sampling units for complete applications (e.g., SimPoint [21] and SMARTS [17]).

- Statistical simulation. This strategy speeds up architectural simulation by building synthetic traces or benchmarks that are representative for long-running benchmarks [22, 23]. The synthetic trace is built based on the results obtained in two collection phases. The first one collects information about instruction count, types and dependencies. The second phase collects micro-architectural dependent statistics (e.g., cache, branch).

- FPGA-accelerated simulation. As the name suggests, it builds timing models onto field-programmable gate-arrays (FPGAs) [24, 25, 26]. These models demand additional hardware and development time to synthesize the model into hardware, so it is common to offload only performance-critical parts of software-based techniques, rather than performing the whole simulation on the FPGA.

- Hybrid simulation. This methodology tries to obtain the best features from cycle-accurate and functional simulation by dynamically switching between them, while keeping the processor-centric state synchronized. HySim [27, 28] divides the code into processor-specific functions (executed in the cycle-accurate simulator) and target-independent functions, exe-

150

155

160

- cuted by the host. MARSS [8] or GEMsOpal [6] support seamless dynamic switching between the cycle-accurate simulation mode and the native x86 emulation mode of QEMU/Simics. gem5 supports KVM-mode, where code execution can be migrated to native hardware for execution and sent back to the simulator, significantly improving the performance [29].

- Control-sensitive simulation. A specific case of sampled simulation that works at a basic block level. A basic block is defined as the code between two branch instructions. Key statistics per basic block can be obtained by running multiple times at different contexts using a timing-accurate simulator (e.g., [30]) or a static worst-case execution time analysis framework [31, 32] such as OTAWA [33] and Absint aiT [34].

- Trace-driven simulation. Timed/functional simulation that uses traces obtained in a real system as inputs. It provides a fast and reliable model for design space exploration, but limited support for architectural changes. Examples of this methodology include CMP\$im [35], Graphite [36], Sniper [37], ZSim [38] or MUSA [39].

Finally, analytical simulation/modeling uses mathematical formulas to model the performance of the architecture. Mechanistic models (or white-box models) [40, 41, 42], construct a model based on the mechanics of the target architecture. On the other hand, empirical models (or black-box models) [43], utilize a parameterized performance model, trained using machine learning or regression 195 analysis, without any specific knowledge about the micro-architecture of the target processor. TQSIM uses analytical models based on sampled simulation over disruptive events, such as cache misses and branch misprediction [13].

Regarding validation of simulation infrastructures, each simulation framework has been validated against real architectures of the same period. However, 200 regression tests for simulator modifications when modifying the source code are usually not present. In addition, hardware evolves quickly, and changing the simulator parameters may lead the model to misbehave when compared

175

180

185

with newer hardware, so additional validation methods are required. Zhang et

al. [44] propose a new methodology for validating simplified simulation models, which focuses on the trends of metric values across benchmarks and architectures, instead of errors of absolute metric values. However, the validation of a simplified model requires a detailed cycle-accurate one. Nyew *et al.* [45] use domain-specific information to effectively capture a potential mismatch between

- the assumed architecture model and its simulator. They show how a simulatorgenerated event trace can be fed into an automatically generated verification program, used to verify that the simulator obeys the invariants. Techniques to extract simulator behavior from traces and present the results to the user are also reported.

- The works that show similarities to ours were performed by Gutierrez *et al.* [46], Butko *et al.* [47], Akram *et al.* [48] and Walker *et al.* [49]. In the first work, the authors validated the gem5 simulator against a Versatile Express TC2 board (Gutierrez) and a Snowball SKYS9500-ULP-C01 board (Butko), not only in terms of runtime, but also by adding statistics about L2 caches.

- In addition, Gutierrez et al. provided L1 data and instruction cache, TLB (Translation Lookaside Buffer.) together with branch predictor statistics. Their evaluation showed 20% accuracy on average for most of them. They link most of this error to modeling similar but not identical components. Gibson et al. [50] also showed the importance of simulator validation to improve accuracy and

- <sup>225</sup> correctness against real hardware. Akram *et al.* performed an evaluation of different x86 simulation infrastructures, reporting an 80% IPC deviation in gem5 when compared with a modern Haswell-like processor. In contrast to previous works, which are designed for a specific platform, we provide a semi-automatic framework to perform a more detailed evaluation of key system components and pipeline stages (both in terms of instructions and running/stalled cycles).

To conclude, Walker *et al.* designed GemStone, a tool which uses hierarchical clustering, correlation analysis, and regression techniques to identify sources of error without requiring detailed CPU specifications. This allows existing models to be improved, new models to be developed, validation of simulator

- changes, and the testing of model suitability for specific use-cases. They also automate the process of characterising hardware platforms, identifying sources of error in gem5 models and quantifying the effect of errors on the performance. This is the closest related work to our validation framework. Their work is fully automated, but lacks the level of detail that our framework can achieve. For ex-

- <sup>240</sup> ample, it is pointed out that they discovered an issue with the branch predictor. This information is also provided by the Top-Down model in our framework. However, other sources of error, such as the one discovered by our framework regarding additional cycles when fetching instructions, or the wrong mapping of instructions to ALUs have not been detected by their tool. We believe this

- <sup>245</sup> is due to the fact that they have tried to find an overall model focusing on "performance", while giving less importance to per/structure detailed functionality. This may hide specific modeling issues that are hidden by overall model behavior. We provide a high abstraction layer (based on the Top-Down model) to summarize processor behavior for a given workload, together with detailed <sup>250</sup> information as expected from a cycle-level simulation infrastructure. We also

- propose some fixes, workarounds and solutions to improve the quality of the works based on the gem5-x86 infrastructure.

#### 3. Validation Framework

- The validation framework presented in this paper consists of a set of python and bash scripts to semi-automatize the process of profiling, gathering, processing and visualizing statistics. This helps to detect errors in cycle-accurate simulation infrastructures. The same framework can be used to check real-system behavior with different input sizes and extrapolate the expected behavior in the simulation infrastructure [4].

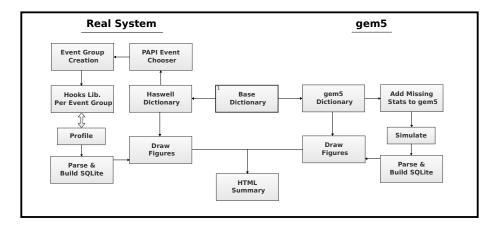

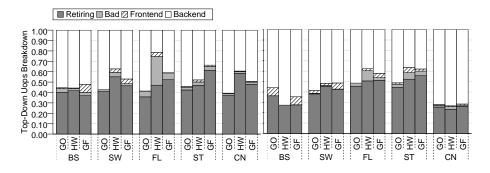

- Figure 1 shows an overview of the validation framework. The base of the framework is a python dictionary (base dictionary), composed by a set of unique keys that map to database entries or simple formulas (multi-level addition, subtraction, multiplication or division) with elements of the database. The current

Figure 1: Overview of the Validation Framework.

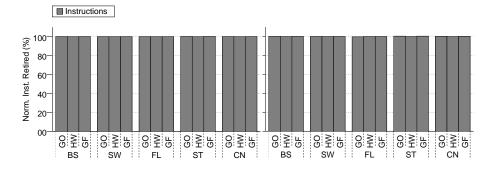

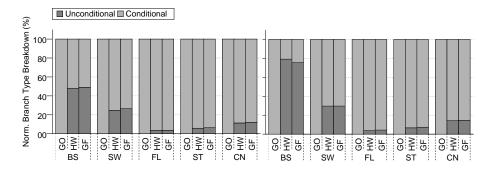

base dictionary defines keys for all the required information to build the TopDown model, as well as pipeline cycle/stall activity and per-stage instruction count; reasons for dispatch/execute stalls; usage statistics for L1, L2, L3 caches, TLB and branch predictor (left column in Tables 1 and 2).

Users need to create a dictionary for each pair architecture/simulator they want to validate (e.g., Haswell Dictionary and gem5 Dictionary in Figure 1). The selected keys will be mapped to specific performance counters or simulator statistics using those dictionaries. Input values will be obtained in the profiling/simulation steps and parsed into a SQLite database. Table 1 shows a complete example for an Intel i7-4600U Haswell processor. For example, the *TOTAL CYCLES* key will search for the database entry *perf::CYCLES*. In addition, the

- key L2 READ ACCESSES maps to a formula that adds the L1D and L1I read misses @(+,perf::PERF COUNT HW CACHE L1D:READ:MISS,perf::PERF COUNT HW CACHE L11:READ:MISS). Formulas can be specified as @(OP-ERATOR, key1, key2 ... keyN). Each key can be, at the same time, a formula with the same format or an entry from the database. On the other hand, if there

- is no performance counter or stat available in either platform, the value "none" should be specified. This abstraction layer, built on top of both the simulator statistics and the real hardware performance counter interfaces (e.g., PAPI,

| Table 1: | Haswell | Dictionary. | Core | Performance | Counters. |

|----------|---------|-------------|------|-------------|-----------|

|          |         |             |      |             |           |

| Dictionary Kove                                                                                       | Associated Database Entry or Fermula (Performance Counter or Combination of Counters)                                                                                                          |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Dictionary Keys Associated Database Entry or Formula (Performance Counter or Combination of Counters) |                                                                                                                                                                                                |  |  |  |  |  |

| CLOCKS                                                                                                | #Top-Down Model<br>CPU.CLK.UNHALTED                                                                                                                                                            |  |  |  |  |  |

| SLOTS                                                                                                 |                                                                                                                                                                                                |  |  |  |  |  |

|                                                                                                       |                                                                                                                                                                                                |  |  |  |  |  |

| DECODED_NONE                                                                                          | IDQ_UOPS_NOT_DELIVERED:CORE                                                                                                                                                                    |  |  |  |  |  |

| ISSUED_ANY                                                                                            | UOPS_ISSUED:ANY                                                                                                                                                                                |  |  |  |  |  |

| RETIRE_SLOTS                                                                                          | UOPS_RETIRED:RETIRE_SLOTS                                                                                                                                                                      |  |  |  |  |  |

| RECOVERY_CYCLES                                                                                       | RECOVERY_CYCLES INT_MISC:RECOVERY_CYCLES                                                                                                                                                       |  |  |  |  |  |

| #Pipeline-Stalls-Per-Stage                                                                            |                                                                                                                                                                                                |  |  |  |  |  |

| TOTAL_CYCLES                                                                                          | perf: CYCLES                                                                                                                                                                                   |  |  |  |  |  |

| STALL_CYCLES_IFETCH<br>STALL_CYCLES_DECODE                                                            | ICACHE:IFETCH_STALL<br>IDQ:EMPTY                                                                                                                                                               |  |  |  |  |  |

| STALL_CYCLES_DISCODE                                                                                  | IDQ:EMPTY<br>RESOURCE_STALLS:ANY                                                                                                                                                               |  |  |  |  |  |

| STALL_CYCLES_DISPATH<br>STALL_CYCLES_ISSUE                                                            |                                                                                                                                                                                                |  |  |  |  |  |

| STALL_CYCLES_ISSUE                                                                                    | UOPS_ISSUED:STALL_CYCLES                                                                                                                                                                       |  |  |  |  |  |

|                                                                                                       | UOPS_EXECUTED:STALL_CYCLES                                                                                                                                                                     |  |  |  |  |  |

| STALL_CYCLES_RETIRE UOPS_RETIRED.STALL_CYCLES                                                         |                                                                                                                                                                                                |  |  |  |  |  |

| MACDO INST TOTAL                                                                                      | #Instructions-Per-Stage                                                                                                                                                                        |  |  |  |  |  |

| MACRO_INST_TOTAL                                                                                      | perf::INSTRUCTIONS                                                                                                                                                                             |  |  |  |  |  |

| MICRO_INST_ISSUED                                                                                     | UOPS_ISSUED:ALL                                                                                                                                                                                |  |  |  |  |  |

| MICRO_INST_EXECUTED                                                                                   | UOPS.EXECUTED:CORE                                                                                                                                                                             |  |  |  |  |  |

| MICRO_INST_RETIRED                                                                                    | UOPS_RETIRED:ALL                                                                                                                                                                               |  |  |  |  |  |

| MACRO_INST_RETIRED                                                                                    | INSTRUCTIONS_RETIRED                                                                                                                                                                           |  |  |  |  |  |

|                                                                                                       | #Cycle Activity                                                                                                                                                                                |  |  |  |  |  |

| CYCLE_ACTIVITY:CYCLES_NO_EXECUTE                                                                      | CYCLE_ACTIVITY:CYCLES_NO_EXECUTE                                                                                                                                                               |  |  |  |  |  |

| CYCLE_ACTIVITY:STALLS_L1D_PENDING                                                                     | CYCLE_ACTIVITY:STALLS_LID_PENDING                                                                                                                                                              |  |  |  |  |  |

| CYCLE_ACTIVITY:STALLS_L2_PENDING                                                                      | CYCLE_ACTIVITY:STALLS_L2_PENDING                                                                                                                                                               |  |  |  |  |  |

| CYCLE_ACTIVITY:STALLS_LDM_PENDING                                                                     | CYCLE_ACTIVITY:STALLS_LDM_PENDING                                                                                                                                                              |  |  |  |  |  |

| CYCLE_ACTIVITY:CYCLES_L1D_PENDING                                                                     | CYCLE_ACTIVITY:CYCLES_L1D_PENDING                                                                                                                                                              |  |  |  |  |  |

| CYCLE_ACTIVITY:CYCLES_L2_PENDING                                                                      | CYCLE_ACTIVITY:CYCLES_L2_PENDING                                                                                                                                                               |  |  |  |  |  |

| RESOURCE_STALLS:ANY                                                                                   | #Dispatch Resource Stalls<br>RESOURCE_STALLS:ANY                                                                                                                                               |  |  |  |  |  |

|                                                                                                       | RESOURCE_STALLS:AN F                                                                                                                                                                           |  |  |  |  |  |

| RESOURCE_STALLS:RS<br>RESOURCE_STALLS:SB                                                              | RESOURCE_STALLS:RS<br>RESOURCE_STALLS:RB                                                                                                                                                       |  |  |  |  |  |

| RESOURCE_STALLS:SB<br>RESOURCE_STALLS:ROB                                                             | RESOURCE_STALLS:SB<br>RESOURCE_STALLS:ROB                                                                                                                                                      |  |  |  |  |  |

| RESOURCE_STALLS:ROB                                                                                   | #TLB                                                                                                                                                                                           |  |  |  |  |  |

| DTLB_READ_HITS                                                                                        |                                                                                                                                                                                                |  |  |  |  |  |

| DTLB_READ_MISSES                                                                                      | perf::PERF_COUNT_HW_CACHE_DTLB:READ:ACCESS<br>perf::PERF_COUNT_HW_CACHE_DTLB:READ:MISS                                                                                                         |  |  |  |  |  |

|                                                                                                       |                                                                                                                                                                                                |  |  |  |  |  |

| DTLB_WRITE_HITS                                                                                       | perf::PERF_COUNT_HW_CACHE_DTLB:WRITE:ACCESS                                                                                                                                                    |  |  |  |  |  |

| DTLB_WRITE_MISSES                                                                                     | perf::PERF_COUNT_HW_CACHE_DTLB:WRITE:MISS                                                                                                                                                      |  |  |  |  |  |

| DTLB_TOTAL_HITS<br>DTLB_TOTAL_MISSES                                                                  | <pre>@(+,perf::PERF_COUNT_HW_CACHE_DTLB:READ:ACCESS,perf::PERF_COUNT_HW_CACHE_DTLB:WRITE:ACCESS)</pre> @(+,perf::PERF_COUNT_HW_CACHE_DTLB:READ:MISS,perf::PERF_COUNT_HW_CACHE_DTLB:WRITE:MISS) |  |  |  |  |  |

|                                                                                                       |                                                                                                                                                                                                |  |  |  |  |  |

| ITLB_READ_HITS                                                                                        | perf::PERF.COUNT_HW.CACHE_ITLB:READ:ACCESS                                                                                                                                                     |  |  |  |  |  |

| ITLB_READ_MISSES perf::PERF_COUNT_HW_CACHE_ITLB:READ_MISS<br>#Branch Predictor                        |                                                                                                                                                                                                |  |  |  |  |  |

| BR_INST_TOTAL                                                                                         |                                                                                                                                                                                                |  |  |  |  |  |

|                                                                                                       | PAPI, BR, INS                                                                                                                                                                                  |  |  |  |  |  |

| RLINST_UNCOND PAPLBR_UCN<br>BR_INST_COND PAPLBR_CN                                                    |                                                                                                                                                                                                |  |  |  |  |  |

|                                                                                                       |                                                                                                                                                                                                |  |  |  |  |  |

| BR_INST_COND_TAKEN                                                                                    | PAPI_BR_TKN                                                                                                                                                                                    |  |  |  |  |  |

| BR_INST_COND_NOT_TAKEN                                                                                | PAPI_BR_NTK                                                                                                                                                                                    |  |  |  |  |  |

| BR_INST_COND_MISSPREDICT                                                                              | PAPI_BR_MSP                                                                                                                                                                                    |  |  |  |  |  |

| BR_INST_COND_CORRECT                                                                                  | PAPI_BR_PRC #Opt-cr                                                                                                                                                                            |  |  |  |  |  |

| CONTEXT SWITCHES                                                                                      | #Other                                                                                                                                                                                         |  |  |  |  |  |

CONTEXT-SWITCHES

perf::CONTEXT-SWITCHES

#### Table 2: Haswell Dictionary. Cache Performance Counters.

| Dictionary Keys    | Associated Database Entry or Formula (Performance Counter or Combination of Counters)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                    | #L1 cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| L1D_READ_HITS      | perf::PERF_COUNT_HW_CACHE_L1D:READ:ACCESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| L1D_READ_MISSES    | perf::PERF_COUNT_HW_CACHE_L1D:READ:MISS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| L1D_WRITE_HITS     | perf::PERF_COUNT_HW_CACHE_L1D:WRITE:ACCESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| L1D_WRITE_MISSES   | PAPI_L1_STM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| L11_READ_HITS      | perf::PERF_COUNT_HW_CACHE_L11:READ:ACCESS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| L11_READ_HITS      | none                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| L11_READ_MISSES    | perf::PERF_COUNT_HW_CACHE_L11:READ:MISS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                    | #L2 cache                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| L2D_READ_ACCESSES  | perf::PERF_COUNT_HW_CACHE_L1D:READ:MISS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| L2D_READ_MISSES    | none                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

| L2D_WRITE_ACCESSES | PAPI_L1_STM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| L2D_ACCESSES_TOTAL | PAPI_L2_DCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

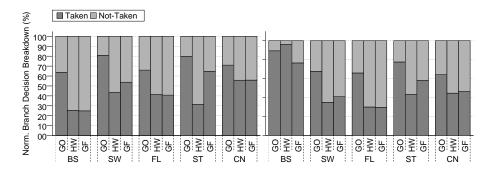

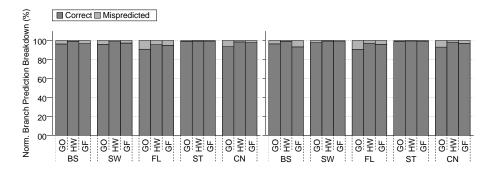

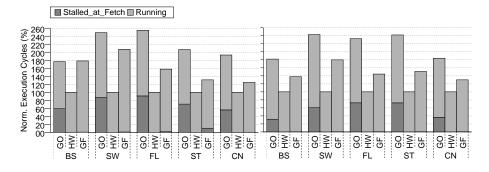

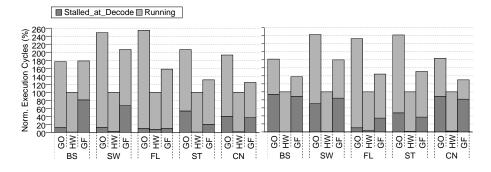

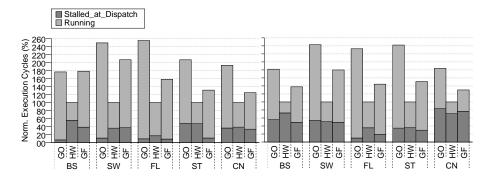

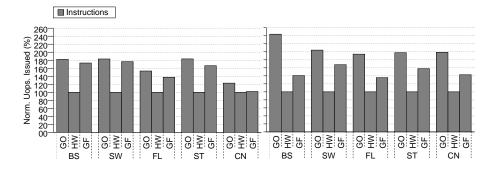

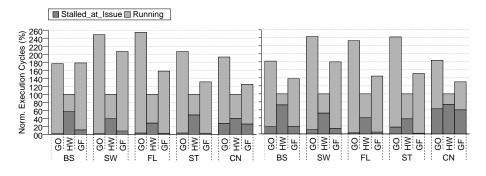

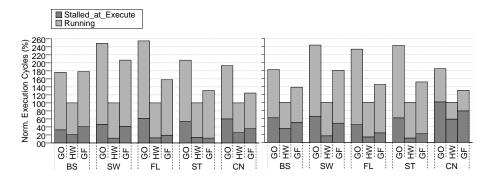

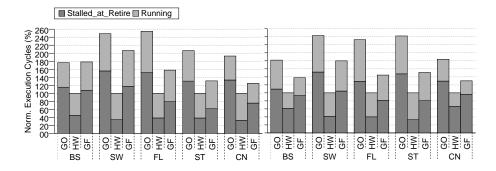

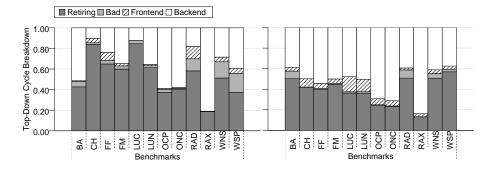

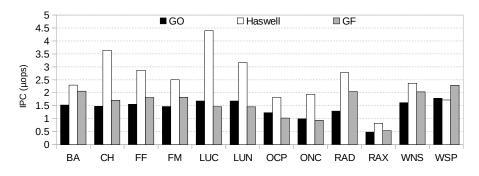

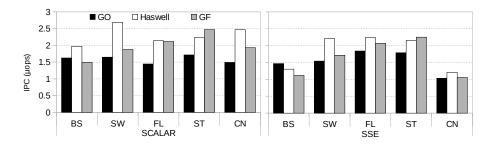

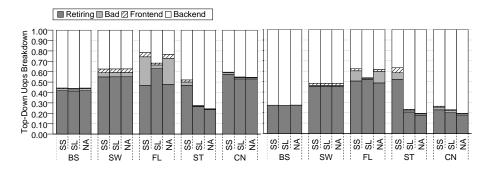

| L2_READ_TOTAL      | PAPIL2.TCR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |