# Low-Voltage, Low-Power V<sub>t</sub> Independent Voltage Reference for Bio-Implants

Paulo Cesar Crepaldi, Tales Cleber Pimenta, Robson Luiz Moreno and Leonardo Breseghello Zoccal

Additional information is available at the end of the chapter

http://dx.doi.org/10.5772/39231

## 1. Introduction

Microelectronics has become a powerful tool of electronic systems for biomedical applications. In recent years, integrated circuits are being fabricated with large densities and endowed with intelligence. The reliability of these systems has been increasing and the costs have been reducing. The interaction between medicine and technology, as it is the case of microelectronics and biosensor materials, allows the development of diagnosing devices capable of monitoring pathogens and diseases. The design of sensors, signal conditioners and processing units aim to place the whole system in the patient or, even more desirable, implanted, where it becomes a Lab-on-Chip and/or a Point-of-Care device (Colomer-Farrarons et al., 2009). Once an implanted device becomes part of a biological data acquisition system, it must meet important constraints, such as reduced size, low power consumption and the possibility of being powered by an RF link, thus operating as a passive RFID tag (Landt. J., 2005).

The low power restriction is extremely important to the patient safety in order to avoid local heating and consequently possible tissue damage. It also limits the power of RF transmitter that can, as well, induce dangerous electromagnetic fields – EMF (large current density in the body tissue surrounding the implant). The EMF risks can be extended to the implanted device itself such as malfunction (undesirable lack of action, erroneous action and hazardous action) and even, permanent damage.

The focus of this chapter is to discuss the implementation of a CMOS voltage reference and the boundary conditions, including the use of a low cost CMOS process (0.35 TSMC for instance), low-voltage low-power operation and simple circuit topology.

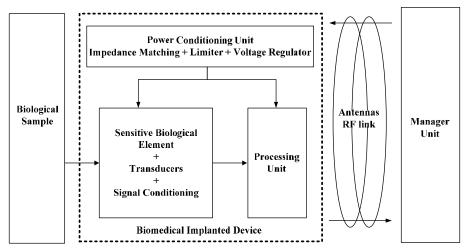

# 2. Typical implanted device as a smart biological sensor

A typical CMOS front-end architecture for an in-vivo Biomedical Implanted Device - BID is shown in Figure 1. The system consists, basically, of the sensitive biological element, the transducer or detector element and its associate electronics and signal processing, and the RF link to establish a communication with the external unit. The combination of the implanted device, the local wireless link and a communication network results in a Wireless Biosensor Network (WBSN) (Guennoun, et al., 2008).

Figure 1. Typical Implanted Biomedical Device acting as a RFID Tag.

Linear systems based on semiconductor devices demand a stable power supply voltage for proper operation. Fluctuations on the input line voltage, load current and temperature variations may cause the circuit to deviate from its optimum operation bias point and even loose its linearity. Therefore, the power supply topology must assure minimum impacts on the linearity under those variations (Crepaldi et al., 2010). The impact of temperature variations in implantable devices is minimized once the body temperature is kept stable at approximately 37°C by an efficient biological feedback system (Mackowiak et al., 1992). Even in the presence of a disease or during a surgery proceeding, the body temperature suffers from just a few Celsius degrees variation.

As can be seen on Figure 1, a Voltage Regulator is part of the power conditioning unit. It is responsible to provide a stable voltage to the sensors/transducers and their associated electronics.

The classic topologies designed to provide stable power supply voltage are the linear and the switched voltage regulators. Switched regulators present a complex topology, mainly due to its control systems, and generally require more power consumption and larger silicon area than linear ones. Additionally they generate more noise at the regulated output due to its inerently switching operation (Rincon-Mora & Allen, 1998).

The low-dropout (LDO) voltage regulator is one of the most popular power converter used in power management and it is extremelly suitable for implanted systems. This kind of regulator requires a voltage reference circuit with a good Process-Voltage-Temperature (PVT) tolerance, generally achieved by Bandgap references. There are alternative circuits capable of obtaining low-voltage and high-accuracy, nevertheless some of those approaches may require components not readily available in CMOS technology and may require additional fabrications steps. Bandgap references based on weak inversion operation are a promising trend in biomedical applications (Roknsharifi et al., 2001; Magnelli et al., 2011). Since the reference is intended to be used in an implanted device, the temperature range is narrow and therefore it is not taken into account. The reference voltage Power Supply Rejection Ratio (PSRR) and process dependence are the main concerns.

# 3. Voltage reference

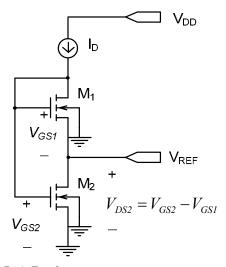

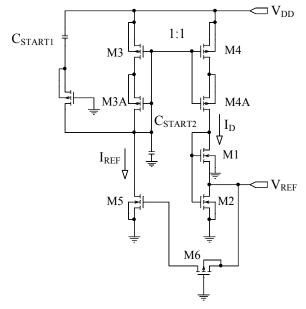

Figure 2 shows the voltage reference suitable for umplented devices. Transistors M1 and M2 form the composite structure (Ferreira & Pimenta, 2006). This kind of arragement represents the key feature for low-voltage operation, and along with low current operation (in the range of nA), the circuit provides low power operation. The voltage reference is obtained at M<sub>2</sub> drain and it corresponds to its V<sub>DS</sub> voltage. The current I<sub>D</sub> is be fixed at tenths of nA in order to reduce the total power consumption, as stated. Also, it is desirable to have the power supply reduced to a minimum, respecting, however, the corner process.

**Figure 2.** Voltage Reference Basic Topology.

If the MOS transistors are biased in the sub-threshold region, the drain current is given by equation (1). This current is based on the channel diffusion current referred to voltage source. It is a consensus formulation among EKV, ACM and BSIM3v3 models. Is is the weak inversion characteristic current, T is the absolute temperature, n is the slope factor in weak inversion (typically 1.3), k is the Boltzmann constant, (W/L) is the transitor geometric aspect ratio,  $V_{TH}$  is the threshold voltage and q is the charge of the electron.

$$I_{DS} = I_{S} \left(\frac{W}{L}\right) exp \left(\frac{V_{GS} - V_{TH}}{\frac{nkT}{q}}\right) \left[1 - exp \left(-\frac{V_{DS}}{\frac{kT}{q}}\right)\right]$$

(1)

Considering transistor  $M_2$  operating in the saturation region, equation (1) can be simplified for  $V_{DS}$  values that are larger than the thermal equivalent voltage (kT/q). At body temperature, approximately 310K, (kT/q) can be set to 26.7mV, so for an 80mV at  $V_{DS}$  (3 times larger) the (1-exp) term in equation (1) can be neglected and the drain current is expressed as:

$$I_{DS} = I_{S} \left(\frac{W}{L}\right) exp\left(\frac{V_{GS} - V_{TH}}{\frac{nkT}{q}}\right); \quad V_{DS} \ge 3\frac{kT}{q} \approx 80mV@T = 310K$$

(2)

The current  $I_S$  is the same for transistors  $M_1$  and  $M_2$  since it is a function of process parameters.  $V_{REF}$  is obtained by considering that  $M_1$  and  $M_2$  drain currents ( $I_{DS}$ ) are also equal.

$$\frac{I_{DS}(M1)}{I_{DS}(M2)} = \frac{I_{S}\left(\frac{W}{L}\right)_{M1} exp\left(\frac{V_{GS1} - V_{TH1}}{\frac{nkT}{q}}\right)}{I_{S}\left(\frac{W}{L}\right)_{M2} exp\left(\frac{V_{GS2} - V_{TH2}}{\frac{nkT}{q}}\right)} = 1$$

(3)

By inspection of Figure 2 it is possible to establish a relationship between the drain source voltage of M2 and the gate voltages of M1 and M2, given as:

$$V_{DS2} = V_{GS2} - V_{GS1} \tag{4}$$

By substituting (4) into (3), *VDS2* is given as:

$$V_{DS2} = \frac{nkT}{q} ln \left[ \frac{\left(\frac{W}{L}\right)_{M1}}{\left(\frac{W}{L}\right)_{M2}} \right] - V_{TH1} + V_{TH2}$$

(5)

Transistor  $M_2$  has a nominal threshold voltage ( $V_{THO}$ ) but  $M_1$  suffer from body effect and, consequently, its threshold voltage should be adjusted by:

$$V_{TH1} = V_{TH0} + \gamma \left( \sqrt{2\Phi_F + V_{SB}} - \sqrt{2\Phi_F} \right) \tag{6}$$

where  $\gamma$  is the body factor coefficient and  $2\Phi F$  ( $\approx 600 \text{mV}$ ) is the Fermi potential. Notice that VsB (bulk-source potential) is equal to M2 drain source voltage or, in other words, it is equal to  $V_{REF}$ . The following approximation (Burington, 1973). can be used, if  $(V_{REF})^2 \ll (2\Phi_F)^2$ .

$$\sqrt{a+x} = \sqrt{a} + \frac{x}{2\sqrt{a}}; \quad a^2 >> x^2$$

$$\sqrt{2\Phi_F + V_{REF}} = \sqrt{2\Phi_F} + \frac{V_{REF}}{2\sqrt{2\Phi_F}}; \quad V_{REF}^2 << (2\Phi_F)^2$$

(7)

By combining (5), (6) and (7), the reference voltage is given as:

$$V_{REF} = \frac{n\frac{kT}{q}ln\left[\frac{\left(\frac{W_{L}}{M_{1}}\right)_{M1}}{\left(\frac{W_{L}}{M_{2}}\right)_{M2}}\right]}{1 + \frac{\gamma}{2\sqrt{2\Phi_{F}}}}$$

(8)

Considering that (Tsividis, 1999):

$$1 + \frac{\gamma}{2\sqrt{2\Phi_F}} = n \tag{9}$$

The resulting equation for the reference voltage is:

$$V_{REF} = \frac{kT}{q} ln \left[ \frac{\left( \frac{W}{L} \right)_{M1}}{\left( \frac{W}{L} \right)_{M2}} \right]$$

(10)

As can be observed, the reference voltage does not depend on MOS transistors threshold voltages and its value is adjusted by the geometric aspect ratio between the M1 and M2. The threshold voltage is largely affected by process variations (corners). For instance, in TSMC 0.35μm technology, the 3σ deviation from typical conditions can be as large as 20%.

Furthermore, the operation in the subthreshold region (or weak inversion) provides promotes an additional feature for the circuit, which is the low-voltage and low-power topology (Bero & Nyathi, 2006; Nomani et al., 2010; Ueno et al., 2006).

## 3.1. Vref range values

The minimum  $V_{REF}$  value is determined by the approximation that leads to eq. (2). The maximum value is determined by the approximation that leads to eq. (7) and Table I shows the relative error at different values of  $V_{REF}$ .

| Vref [mV] | $\sqrt{2\Phi_F^{} + V_{REF}^{}}$ | $\sqrt{2\Phi_F} + \frac{V_{REF}}{2\sqrt{2\Phi_F}}$ | Relative Error<br>(%) |

|-----------|----------------------------------|----------------------------------------------------|-----------------------|

| 80        | 0.825                            | 0.826                                              | 0.196                 |

| 100       | 0.837                            | 0.839                                              | 0.297                 |

| 120       | 0.849                            | 0.852                                              | 0.416                 |

| 140       | 0.860                            | 0.865                                              | 0.550                 |

| 160       | 0.872                            | 0.878                                              | 0.699                 |

**Table 1.** *VREF* Relative Error for eq. (7) approximation.

For this project, it is adopted 100mV for  $V_{REF}$ . This value is larger than 3(kT/q) and represents an error of less than 0.5%, as stated in Table I. Besides, it is an "exact" value to be used in the voltage regulator to obtain other reference values.

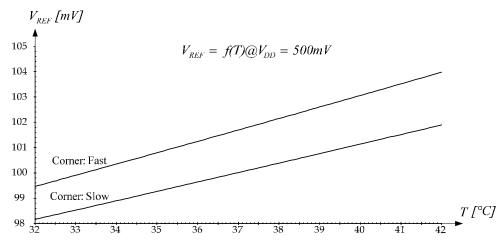

## 3.2. Vref temperature impact

Although the proposed circuit is intended to be used in a temperature controlled environment, a temperature analysis is performed, and it shows a linear behavior. Although it is an important result, the implanted biomedical system could use any calibration method to compensate the process corners deviations. The temperature behavior of VREF can be found from eq. (11) at the different temperatures  $T_0$  and T.

$$\frac{V_{REF}(T)}{V_{REF}(T_0)} = \frac{\frac{kT}{q} ln \left[ \frac{(W/L)_{M2}}{(W/L)_{M1}} \right]}{\frac{kT_0}{q} ln \left[ \frac{(W/L)_{M2}}{(W/L)_{M1}} \right]} = \frac{T}{T_0}$$

(11)

It can be inferred from eq. 11 that the drain-source voltage of M1 presents a PTAT (Proportional to Absolute Temperature) behavior. Fig. 3 shows the simulation of circuit from Fig. 1 over the 35°C to 42°C temperature range, for a 500mV power supply voltage. That temperature range corresponds to limits between surgical procedures (lowered body temperature) or any pathology (fever). The simulation includes the three corners; typical, slow and fast. Additional circuitry, as shown in Fig. 1 (Processing Unit), can be added to provide an analog to digital conversion, where the gain and offset errors can be minimized.

**Figure 3.** Simulation of *VREF* voltage @ VDD=0.5V for a clinical temperature range including the fast and slow process corners.

Including this temperature impact, the voltage reference can be stated as having a nominal value of 100mV (typical) with a worst case dispersion of +4% (fast corner) and -1,8% (slow corner). The respective temperature coefficients are 0.35mV/°C (slow corner) and 0.45mV/°C (fast corner).

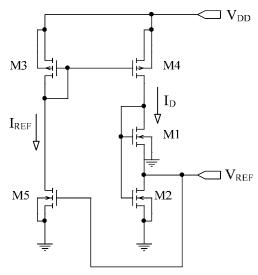

# 4. The voltage reference circuit implemented with composite transistors

Fig. 4 shows the circuit used to generate the current ID. Transistor M5 is biased by the voltage reference, which it is assumed to be constant, and its drain current (IREF) is mirrored by M3-M4. The overall circuit implementation is done by using composite transistors as depicted in Fig. 5. The current  $I_D$  is fixed at approximately 15nA. As can be observed, there is a feedback loop M2-M5 that does improve the PSRR of the circuit, as it will be demonstrated by simulation. The use of composite transistors is fundamental to reduce the mismatch between the mirrored currents.

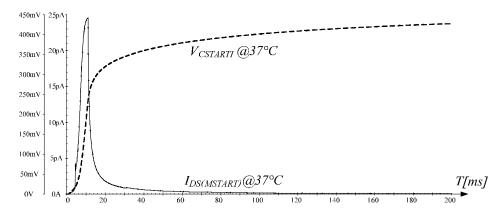

As it is the case of self-biased circuits, it is necessary a startup circuit. It is implemented through transistor MSTART, and capacitors CSTART1 and CSTART2. On power up, an impulsive current will flow and the circuit will be lead to the desired operation point condition. All the transistors aspect ratios are optimized by a set of interactive simulations aiming the target values I<sub>D</sub>=15nA and V<sub>REF</sub>=100mV, for the typical process parameters.

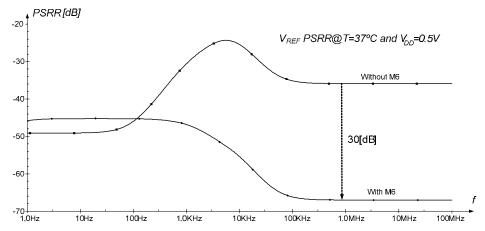

Transistor M6 is included in the feedback loop to improve the power supply rejection ratio (PSSR) at higher frequencies, as it acts a low pass filter.

Mostly transistors aspect ratios are also refined by interactive simulations. Transistor M2 aspect ratio is assumed to be 50/1 where the channel length of 1µm is adopted to be approximately 3 times the minimum size of 0.35 TSMC process to reduce the short channel effects.

**Figure 4.** In current generation by mirroring concept.

Figure 5. Proposed Reference circuit.

# 5. Simulation results

This section presents a set of electrical simulations that validate the main concepts of the voltage reference.

# 5.1. Minimum power supply

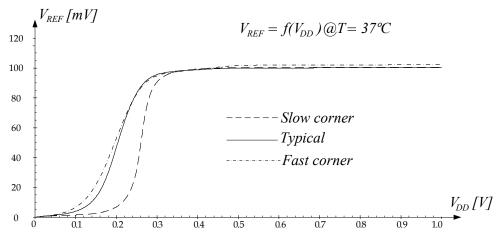

As stated early, it is important to keep the whole system operating in the low power condition. Fig. 6 shows the simulation used to investigate the minimum power supply that maintains the circuit proper function. The temperature was kept constant at 37°C. The three curves are result of typical, slow, and fast PMOS and NMOS parameters of 0.35 TSMC process.

As it can be observed, the supply voltage can be as low as 500mV. Table 2 lists the reference voltage values for some supply voltages and the relative deviation from the nominal (typical) value. The 500mV power supply indicates a worst case deviation of 1.69% at the process corners. This simulation shows an important result since it is in accordance with equation (10), thus indicating an independence of the voltage reference regarding the process corners. Additionally, the use of transistors operating in weak inversion allows power supply voltage reduction to values that characterize low voltage operation.

Figure 6. Simulation to Evaluate the Minimum Power Supply Voltage.

|                     | V <sub>REF</sub> @ T=37°C (mV) |         |        |                           |

|---------------------|--------------------------------|---------|--------|---------------------------|

| V <sub>DD</sub> [V] | Slow                           | Typical | Fast   | Deviation<br>(worst case) |

| 0.5                 | 100.31                         | 99.99   | 101.68 | +1.69%                    |

| 0.6                 | 100.38                         | 100.09  | 102.04 | +1.95%                    |

| 0.7                 | 100.39                         | 100.11  | 102.10 | +1.99%                    |

| 0.8                 | 100.40                         | 100.13  | 102.15 | +2.01%                    |

**Table 2.** *VREF* as a Function of VDD for typical values and process corners.

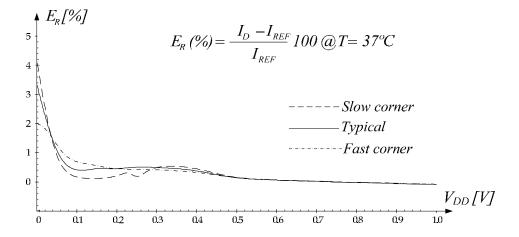

#### 5.2. Matching between IREF and ID

The PMOS composite pairs improve the matching between currents IREF and ID. The simulation results on Fig. 7 show the relative error (ER in %) between currents IREF and ID for the typical and corners process. At a 500 mV supply voltage, the worst case is approximately 0.155%. The current matching between IREF and ID is achieved by the PMOS current mirror due to the higher impedance of the composite structure. This output impedance, for both PMOS pairs, can be stated as:

$$r_{O}(M3A) = ng_{m}(M3A)r_{O}(M3A)r_{O}(M3)$$

(12)

Another point of interest is the fact that the matching between the currents is significant (lower dispersion) from 500mV of power supply, confirming the use of this minimum value.

**Figure 7.** Simulation to Evaluate Mismatch Between *IREF* and *ID*.

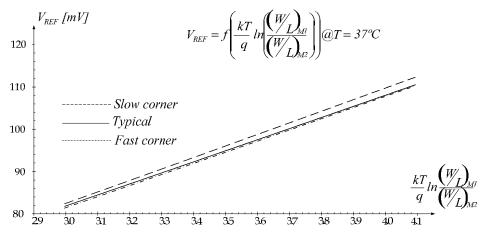

## 5.3. Geometric aspect ratio for transistors M1 and M2

Eq. (10) presents the geometric aspect ratios of transistors M1 and M2,  $(W/L)_1$  and  $(W/L)_2$ , respectively. Therefore, it is possible to evaluate this ideal relationship to achieve the desired target value for the reference voltage. As mentioned previously, it was adopted the minimum channel length L as  $1\mu m$  to minimize short channel effects.

Consequently it is also necessary to adopt a geometric aspect ratio of transistor M2. The  $(W/L)_2$  relationship must be large enough to maintain the  $I_D$  current along all the process corners. A simulation of M2 shows that a 50/1 geometric aspect is enough. Therefore, a simulation process is used to investigate the ideal W/L relationship for M1. Fig. 8 shows the simulation of equation (10) considering the  $V_{REF}$  as a function of geometric aspect ratios  $(W/L)_1$  and  $(W/L)_2$ . Table 3 resumes the values for the 100mV target value.

Figure 8. Simulation used to Evaluate the Geometric Aspect Ratio of Transistor M1

| V <sub>REF</sub> =100mV@ T=37°C and (W/L) <sub>M2</sub> =50/1                                                                          |        |               |      |  |

|----------------------------------------------------------------------------------------------------------------------------------------|--------|---------------|------|--|

|                                                                                                                                        | Slow   | Typical       | Fast |  |

| $ \ln \left[ \frac{(W_L)_{M1}}{(W_L)_{M2}} \right] \qquad 3.6951 \qquad 3.7069 \qquad 3.644 $                                          |        |               |      |  |

| $\left(\frac{W}{L}\right)_{M1}$ [µm]                                                                                                   | 2012.5 | 2012.5 2036.4 |      |  |

| Equation (10) considering (kT/q)=26.73mV@T=37°C                                                                                        |        |               |      |  |

| $\ln \left[ \frac{\binom{W/L}{M1}}{\binom{W/L}{M2}} \right] = 3.7453 \text{ and } \binom{W/L}{M1} = 2107 \text{ [}\mu\text{m}\text{]}$ |        |               |      |  |

Table 3. Simulated and Calculated Geometric Aspect Ratio for Transistor M1.

It was adopted, in this work, (W/L)1 =2036/1 as the typical value. Although there is a dispersion of about 9% between the calculated and simulated (W/L) values for the worst case corner (fast), the impact on the reference voltage is minimized by the logarithmic dependence.

# 5.4. Monte Carlo analysis

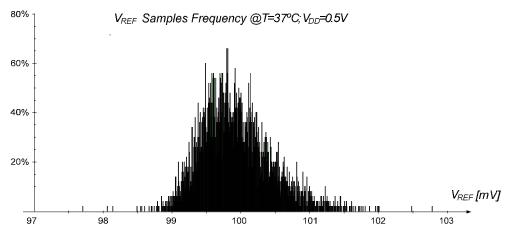

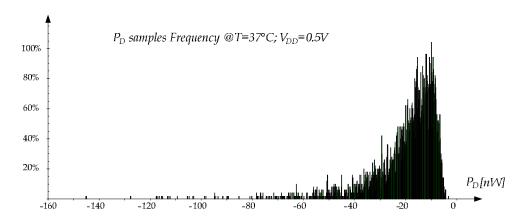

A set of 5000 runs were performed to evaluate the statistical parameters related to VREF. Figs. 9 and Fig. 10 show the simulation result for the reference voltage VREF and the total power dissipation *P*<sub>D</sub>. Table 4 presents the main values.

**Figure 9.** Monte Carlo Analysis – VREF percentage samples.

Figure 10. Monte Carlo Analysis – PD percentage samples.

|      | Vref[mV] | PD [nW] |

|------|----------|---------|

| Mean | 99.9     | 16.9    |

| σ    | 0.503    | 14.6    |

| 3σ   | 1.512    | 43.9    |

**Table 4.** Monte Carlo Analysis @ VDD=500mV and T=37°C.

Table 4 shows that the  $V_{REF}$  can be expressed as 99.9±1.512mV (±1.5%) for a 3 $\sigma$  dispersion. This is an important result considering that the process inherently dispersion on Vt is approximately ±20% (3 $\sigma$ ). A total power dissipation in the range of tenths of nW characterizes a low-power operation. The minus signal in the simulation results is due to the simulation algorithm.

## 5.5. Start-Up circuit

As it is the case of a self-polarized circuit, it is necessary a start-up approach to move the circuit operation to the desired condition. In other words, the start-up circuit must lead the main circuit to the desired operating point. This is realized by introducing the additional components MSTART, CSTART1 and CSTART2. Fig. 11 shows the simulation of MSTART current and CSTARTI voltage as a response to a voltage ramp applied to VDD. As the current vanishes to zero, Cstarti charges toward Vdd and the power dissipated in Mstart tends to zero. The fast and small impulsive current IDS(MSTART) is sufficient to start the whole reference circuit.

Figure 11. Current though MSTART and CSTART1 voltage.

Figure 12. PSRR simulation with and without transistor M6.

# 5.6. Power Supply Rejection Ratio (PSRR)

The voltage reference must exhibit a high PSRR, especially at high frequencies since the implanted device will be activated by a Radio Frequency link. The PMOS transistor placed between M2 and M5 acts as a low-pass filter. Fig. 12 shows the PSRR simulation. As it can be observed from the PSRR simulation presented in Fig 12, the PSRR can be 65dB in the MHz frequency range.

## 6. Layout

The proposed circuit was implemented in standard 0.35µm TSMC CMOS process through MOSIS educational program. Table 5 shows the aspect ratios of the all transistors. In this table the factor M represents a multiplier; i. e. the respective transistor is, actually, a parallel association. For instance, transistor M4A is a parallel association of 3 identical transistors with a geometric aspect ratio of 1000/2.

| Transistor | W/L [µm] | M |

|------------|----------|---|

| M1         | 50/1     | 1 |

| M2         | 2036/1   | 1 |

| M3         | 150/2    | 1 |

| M3A        | 1000/2   | 3 |

| M4         | 150/2    | 1 |

| M4A        | 1000/2   | 3 |

| M5         | 2500/1   | 5 |

| M6         | 2500/120 | 1 |

**Table 5.** All Transistors Geometric Aspect Ratio.

The capacitors are poly-insulator-poly - PIP structures and the layouts of the NMOS and PMOS transistors were implemented using multifinger common centroid configuration. Besides better matching, this layout technique is less sensitive to process variation (Hastings, 2001; Qiang et al., 2011). The source-bulk connection of the PMOS transistors is possible since the TSMC is an n-well process, and therefore all the PMOS transistors are fabricated in different wells.

Mainly for the design of analog integrated circuits, the layout of two matched components is realized in such a way that they can be divided into identical sections, placed symmetrically in a matrix array.

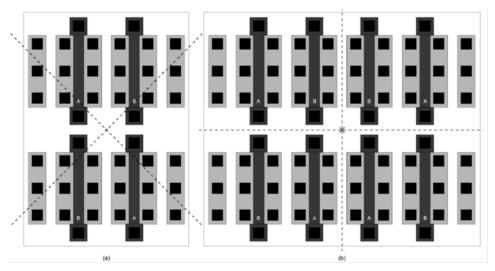

The common centroid layout using matched components arranged in a matrix array, in identical and symmetrical sections, is essential to reduce or even eliminate the systematic mismatching. The distances between the centroids components are null and so are the mismatching caused by mechanical and temperature stress. For instance, in order to improve the differential pair match in operational amplifiers, these transistors are placed in a cross coupled array. Fig. 13 (a) shows two matched devices, each composed of two segments arranged in an array of two rows and two columns (cross-coupled pair). Resistors are rarely laid out as cross-coupled pairs because the resulting arrays usually have unwieldy aspect ratios. If the matched devices are large enough to segment into more than two pieces, then the cross-coupled pair can be further subdivided as show Fig. 13 (b).

Figure 13. Examples of two dimensional common-centroid arrays.

It is recommended that matched components are fabricated near each other, minimizing the mechanical stress. The mechanical stress difference between two matched components is proportional to the abrasive gradient and their distance. For calculations purposes, the location of the component is determined as the average contribution of each section of the component. The resultant location is called centroid of the component. It is important that any symmetric axis crosses the centroid of the device or component

To design components with a centroid layout some rules must be observed:

- Coincidence: The matched devices centroids must be superimposed or as close as 1. possible;

- Symmetry: The component matrix must be symmetrical along the X and Y axes. Ideally, the symmetry must be a consequence of the placement positions of the components and not for the symmetry of each component individually;

- Dispersion: The matrix must exhibit the greatest dispersion level, i.e., each component must be placed with high symmetry along the matrix;

- Compression: The matrix should be as compact as possible, ideally close to a square shape.

A better matching between integrated components reflects in the overall performance of the designed circuit or system. Depending on the matching accuracy, it is possible to consider the following cases:

- *Minimum*: In the range of  $\pm$  1% (representing 6 to 7 bits of resolution). Used for general components in an analog circuit. For instance, current mirrors and biasing circuits;

- Moderate: In the range of  $\pm$  0.1% (representing 9 to 10 bits of resolution). Used in bandgap references, operational amplifiers and input stage of voltage comparators. This range is the most appropriate for analog designs.

Severe: In the range of  $\pm 0.01\%$  (representing 13 to 14 bits of resolution). Used in high precision analog to digital converters (ADCs) and digital to analog converters (DACs). Analog designs using capacitors relations reach this resolution easier than those that use resistors relations.

In the case of a MOS transistor, the process and electrical parameters that have must be taken into account into matching purposes are listed in Table 6.

| Process Parameters             | Electrical Parameters |

|--------------------------------|-----------------------|

| Flat band voltage              | Drain current         |

| Mobility                       | Gate-Source voltage   |

| Substrate Dopant Concentration | Transconductance      |

| Chanel length variation        | Output resistance     |

| Chanel width variation         |                       |

| Short channel effect           |                       |

| Narrow channel effect          |                       |

| Gate oxide thickness           |                       |

| Source/Drain sheet resistance  |                       |

Table 6. Process and Electrical Parameters for Component Matching.

## 7. Conclusions

This chapter presented a low-voltage low-power voltage reference for biomedical applications in which the operating temperature is kept almost constant. Besides a simple topology, the proposed circuit has the advantage of low power dissipation, thus avoiding patient tissue damages. The topology offers a low dependence on process corners and high PSRR. Simulation results point to a reference voltage of 100mV with ±1.5% dispersion (3σ) considering typical and corners parameters. The maximum total dissipated power is about 60.8nW (max) and the PSRR is better than 45dB for a frequency range between 1Hz and 100MHz.

Table 7 shows a comparison of this work with other previously reported in the literature.

|                            | This Work | (Lukaszewicz et.al, 2011) | (Li et al., 2007) |

|----------------------------|-----------|---------------------------|-------------------|

| Tachnology                 | CMOS      | CMOS                      | CMOS              |

| Technology                 | 0.35µm    | 65nm                      | 0.5µm             |

| Vdd [V]                    | 0.5       | 2.6 – 3.63                | 4 - 6             |

| I <sub>D</sub> [μA]        | 0.12      | 47                        | -                 |

| Vref [mV]                  | 100       | -                         | -                 |

| Iref [µA]                  | -         | 6.45                      | 1.612             |

| Area [mm <sup>2</sup> ]    | 0.43      | -                         | 0.026             |

| PSRR [dB]                  | 65@10MHz  | 103@10MHz                 | 45                |

| Process<br>Sensitivity [%] | ±1.5      | ±3                        | ±5.2              |

**Table 7.** Comparison with previous work.

#### **Author details**

Paulo Cesar Crepaldi, Tales Cleber Pimenta, Robson Luiz Moreno and Leonardo Breseghello Zoccal Universidade Federal de Itajuba, Brasil

#### 8. References

- Bero, B. & Nyathi, J. (2006). Bulk CMOS Device Optimization for High-Speed and Ultra-Low Power Operations. 49th IEEE International Midwest Symposium on Circuits and Systems, 2006. MWSCAS '06. 6-9 Aug. 2006, pp. 221-225.

- Burington, R. S. (1973). Handbook of Mathematical Tables and Formulas. McGraw-Hill Book Company, 5th Edition, 1973.

- Colomer-Farrarons, J.; Miribel-Catala, P.; Rodriguez, I. & Samitier, J. (2009). CMOS front-end architecture for In-Vivo biomedical implantable devices. Industrial Electronics, 2009. IECON '09. 35th Annual Conference of IEEE Publication, 3-5 Nov, 2009, pp. 4401 – 4408.

- Crepaldi, P.C.; Pimenta, T. C.; Moreno, R. L. & Rodriguez, E. C. (2010) A Linear Voltage Regulator for an Implanted Device Monitoring System. Analog Integrated Circuits and Signal Processing, Vol. 65, Number 1, March 2010, pp. 131-140.

- Ferreira, L. H. C. & Pimenta, T. C. (2006). A Weak Inversion Composite MOS Transistor for Ultra-Low-Voltage and Ultra-Low-Power Applications. Proc. 13th Int. Conf. Mixed Design Integ. Circuits Syst., Gdynia, Poland, Jun. 2006.

- Guennoun, M.; Zandi, M. &El-Khatib, K. (2008). On the use of Biometrics to Secure Wireless Biosensor Networks. Information and Communication Tecnologies: From Theory to Applications, 2008. ICTTA 2008. 3rd International Conference on Digital Idenfier. 7 - 11 April 2008. pp. 1-5.

- Hastings, A. (2001). The Art of Analog Layout, Publisher: Prentice Hall; 2nd edition (July 4, 2005), ISBN-13: 978-0131464100.

- Landt. J. (2005). The History of RFID, Potentials, IEEE, Volume 24, Issue 4, Oct Nov, 2005, pp. 8-11.

- Li, W.; Lenain, H. & Y. Xiaoling. (2007). All CMOS Temperature, Supply Voltage and Process Independent Current Reference", 7th International Conference on ASIC, 2007. ASICON '07, 22-25 Oct. 2007, pp. 600-603.

- Lukaszewicz, M.; Borejko, T. & Pleskacz, W.A. (2011) A resistorless current reference source for 65 nm CMOS technology with low sensitivity to process, supply voltage and temperature variations. IEEE 14th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS), 2011, pp. 75 - 79

- Mackowiak, P. A.; Wasserman, S. S. & Levine, M. M. (1992). A critical appraisal of 98.6°F, the upper limit of the normal body temperature, and other legacies of Carl Reinhold August Wunderlich. JAMA, volume 268, no. 12, Sept 23/30 1992, pp. 1578-1580.

- Magnelli, L.; Crupi, F.; Corsonello, P.; Pace, C. & Iannaccone, G. (2011). A 2.6 nW, 0.45 V Temperature-Compensated Subthreshold CMOS Voltage Reference. IEEE Journal of Solid-State Circuits, Feb 2011, Volume: 46, Issue: 2, pp. 465-474.

- Nomani, W. K.; Anis, M. & Koley, G. (2010). Statistical Approach for Yield Optimization for Minimum Energy Operation in Subthreshold Circuits Considering Variability Issue. IEEE Transactions on Semiconductor Manufacturing, Vol. 23 No. 1, February 2010. Pp. 77-86.

- Qiang, M.; Linfu, X.; Yiu-Cheong M. & Young, E. F. Y. (2011). Simultaneous Handling of Symmetry, Common Centroid, and General Placement Constraints. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, Vol. 30, Issue:1, 2011, pp. 85 – 95.

- Rincon-Mora, G. A. & Allen, P. E. (1998). Study and Design of Low Drop-Out Regulators. School of Electrical and Computer Engineering - Georgia.

- Roknsharifi, M.; Haider, M.R. & Islam, S.K. (2011). A low-power area efficient voltage reference and data generation unit for inductively powered implant system", Biomedical Wireless Technologies, Networks, and Sensing Systems (BioWireleSS), 2011 IEEE Topical Conference on, Publication Year: 2011, pp: 107 – 110.

- Tsividis, Y. P. (1999). Operation and Modeling of the MOS Transistor," Mc-Graw Hill, 1999.

- Ueno, K.; Hirose, T.; Asai, T. & Amemiya, Y. (2006). Ultralow-Power Smart Temperature Sensor with Subthreshold CMOS Circuits. 2006 International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS2006) Yonago Convention Center. 12-15 Dec. 2006, pp. 546-549.