# Improved Performance by using TaON/SiO<sub>2</sub> as Dual Tunnel Layer in Charge-Trapping Nonvolatile Memory

J. X. Chen<sup>a</sup>, J. P. Xu<sup>a</sup>\*, L. Liu<sup>a</sup>, X. D. Huang<sup>b</sup>, P. T. Lai<sup>b</sup>\*

#### **Abstract**

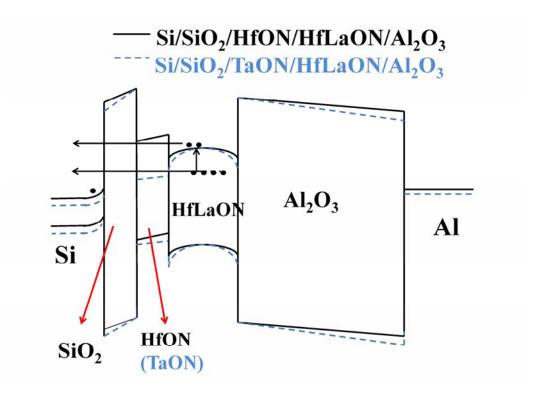

Tunneling-barrier engineered stacks with different high-κ dielectrics are investigated by fabricating the stacked structures of Al/Al<sub>2</sub>O<sub>3</sub>/HfLaON/ (TaON/SiO<sub>2</sub>)/Si and Al/Al<sub>2</sub>O<sub>3</sub>/HfLaON/ (HfON/SiO<sub>2</sub>)/Si. As compared to the device with HfON/SiO<sub>2</sub> dual tunnel layer (DTL), the one with TaON/SiO<sub>2</sub> DTL shows larger memory window (3.85 V at  $\pm 13$  V/1 s), higher program/erase speeds (1.85 V/-2.00 V at +/-12 V/100 μs), better endurance (window narrowing rate of 5.7% after 10<sup>5</sup> cycles). The main mechanisms involved lie in (1) the higher dielectric constant of TaON which induces high electric field in the SiO<sub>2</sub> layer, (2) the smaller conduction/valence-band offsets between TaON and the Si substrate, and (3) better interface quality with SiO<sub>2</sub>. Furthermore, compared with SiO<sub>2</sub> single tunnel layer, better retention characteristics can be achieved for the TaON/SiO<sub>2</sub> DTL due to its larger thickness.

**Keywords**: Flash memory; MONOS; dual tunnel layer (DTL); high-κ dielectric

E-mail address: jpxu@mail.hust.edu.cn, fax: +86-27-87544406 (J. P. Xu),

E-mail address: laip@eee.hku.hk, fax: +852-25598738 (P. T. Lai)

<sup>&</sup>lt;sup>a</sup> School of Optical and Electronic Information, Huazhong University of Science and Technology, Wuhan 430074, P. R. China

<sup>&</sup>lt;sup>b</sup> Department of Electrical & Electronic Engineering, the University of Hong Kong, Pokfulam Road, Hong Kong

<sup>\*</sup>Corresponding authors.

#### 1, Introduction

In recent years, metal-oxide-nitride-oxide-silicon (MONOS) chargetrapping flash memory has attracted a lot of attention due to its advantages of low operating voltage, feasibility of scaling, and simple fabrication process. The basic challenge of the charge-trapping flash memory is how to achieve a tradeoff between program/erase (P/E) efficiency and data retention [1]. The variable oxide thickness (VARIOT) concept [2], consisting of at least two dielectric layers with different dielectric constants  $\kappa$  (i.e., low- $\kappa$ /high- $\kappa$  stack), is a promising solution for the compromise due to the enhanced sensitivity of tunneling current to electric field. Over the past years, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, HfAlO, and Ti-silicate have been investigated as the high-κ material in the SiO<sub>2</sub>/high-κ stack [3-7], and improvements in the relevant memory performances have been demonstrated by using the low-κ/high-κ stack as dual tunnel layer (DTL). On the other hand, nitrogen incorporation in high-κ dielectric films can results in beneficial characteristics, including excellent resistance to interdiffusion of elements between different layers, improved thermodynamic stability, and enhanced immunity to damage induced by high-field stress [8, 9], all of which are highly desirable for the tunneling-barrier engineering applications. However, a combination of the VARIOT concept with the nitrided high-κ oxide film was rarely reported. With a high dielectric constant ( $\kappa \sim 22$ ) and good thermodynamic stability

on  $SiO_2$ , the low-trap-density HfON is believed to be a promising candidate for the barrier-engineered tunnel dielectric in NAND flash memory applications [10-12]. In addition, TaON was also proposed to replace the conventional  $SiO_2$  due to its high dielectric constant ( $\kappa \sim 34$ ) as well as good thermal stability [13, 14], and its small conduction/valence-band offsets to the Si substrate makes it very beneficial for electrons/holes tunneling through the barrier and thus improving P/E performance of the memory devices [15, 16]. Therefore, a new MONOS flash memory structure with TaON/SiO<sub>2</sub> or HfON/SiO<sub>2</sub> as DTL can be proposed by combining the VARIOT concept with the nitrided high- $\kappa$  oxide film.

In this work, MONOS devices with TaON/SiO<sub>2</sub> or HfON/SiO<sub>2</sub> as DTL, HfLaON as charge storage layer (CSL) and Al<sub>2</sub>O<sub>3</sub> as blocking layer (BL) were fabricated, and their memory performances are extensively compared. Experimental results reveal that the memory device with TaON/SiO<sub>2</sub> DTL can achieve larger memory window, higher P/E speeds, and better endurance than the device with HfON/SiO<sub>2</sub> DTL. Also, the retention characteristics of both devices with DTL are improved as compared with the control device with SiO<sub>2</sub> as single tunnel layer.

## 2, Experimental details

MONOS capacitors were fabricated on p-type silicon wafers with a resistivity of  $1 \sim 10 \ \Omega$  cm. After the standard RCA cleaning, 4-nm SiO<sub>2</sub> was grown by thermal oxidation at 900 °C. Then, 4-nm TaON was deposited on SiO<sub>2</sub> by sputtering a Ta target in an Ar/O<sub>2</sub>/N<sub>2</sub> (12/3/15) ambient, followed by rapid thermal annealing in N<sub>2</sub> at 800 °C for 30 s to form TaON/SiO<sub>2</sub> DTL (denoted as TaON sample). For comparison, HfON was also prepared on SiO<sub>2</sub> by sputtering a Hf target in the same deposition and annealing conditions to form HfON/SiO<sub>2</sub> DTL (denoted as HfON sample). Next, 10-nm HfLaON layer as CSL was deposited by RF-sputtering of HfLa target in an Ar/O<sub>2</sub>/N<sub>2</sub> (24/3/6) ambient, followed by rapid thermal annealing in N<sub>2</sub> at 500  $^{0}$ C for 30 s. Then, 13-nm Al<sub>2</sub>O<sub>3</sub> as blocking layer was deposited by ALD method at 300 °C. Finally, Al was evaporated and patterned as gate electrode and also as back electrode, followed by forming-gas annealing in  $H_2/N_2$  (5%  $H_2)$  at 300  $^{0}C$  for 20 min. In order to investigate the qualities of the TaON/SiO<sub>2</sub> and HfON/SiO<sub>2</sub> interfaces, MIS capacitors with Al/TaON/SiO<sub>2</sub>/Si and Al/HfON/SiO<sub>2</sub>/Si structures were fabricated by the same processing conditions.

The dielectric film thickness was measured by multi-wavelength ellipsometry. The electrical characteristics of the devices were measured at room temperature using HP4284A precision LCR meter and HP4156A precision semiconductor parameter analyzer. The flat-band voltage  $(V_{FB})$

of the samples was extracted by assuming  $C_{FB}/C_{OX} = 0.5$  ( $C_{FB}$  and  $C_{OX}$  are the flat-band and oxide capacitances respectively, determined from 1-MHz high-frequency C-V curve). All measurements were carried out under light-tight and electrically-shielded condition.

#### 3, Results and discussion

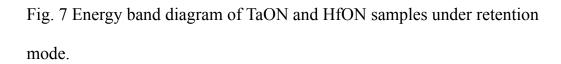

Fig. 1 shows the C-V curves of the MIS capacitors swept in forward and backward directions under +/-4 V sweeping voltages. Little hysteresis is observed for the two devices, indicating the high-quality bulk and interfacial properties of the high-k dielectric layers. Furthermore, the slope of the C-V curve for the Al/TaON/SiO<sub>2</sub>/Si MIS capacitor is steeper than that of the Al/HfON/SiO<sub>2</sub>/Si MIS capacitor, implying better interface quality for the TaON/SiO<sub>2</sub> than the HfON/SiO<sub>2</sub> [17]. In addition, based on the dielectric constants of TaON and HfON [10,14] as well as a low-κ/high-κ thickness of 4 nm/4 nm, the accumulation capacitance for the MIS capacitors with Al/TaON (or HfON) /SiO<sub>2</sub>/Si structures and gate area of  $7.85 \times 10^{-5}$  cm<sup>2</sup> can be calculated to be 60.7 pF and 57.5 pF respectively, which are larger than the ones extracted from the measured C-V curves of the two samples (53.6 pF and 50.8 pF, respectively). The difference should be attributed to the fact that the  $\kappa$  values of the deposited dielectrics are slightly smaller than those in the literature, probably due to the difference in elemental composition and the interface

between the high- $\kappa$ /low- $\kappa$  layers [17].

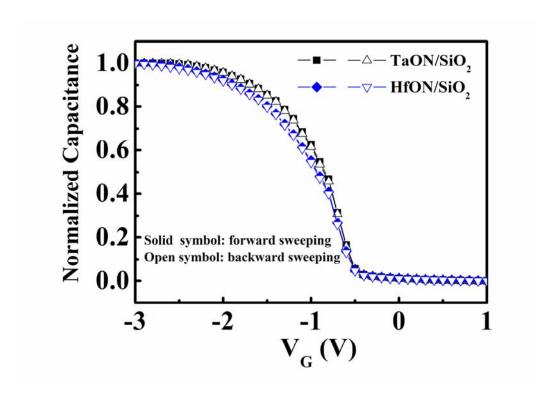

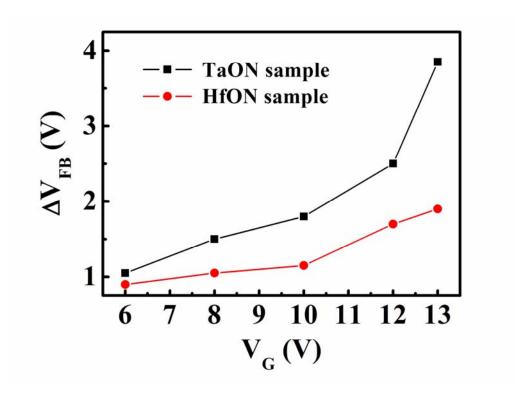

Fig. 2 shows the memory window of the two samples under different P/E voltages for 1 s. It can be observed that the TaON sample presents larger flatband voltage shift ( $\Delta V_{FB}$ ) than the HfON observed sample. Furthermore, their difference increases as the P/E voltage increases. This could be attributed to the fact that TaON has a larger dielectric constant ( $\kappa \sim 34$ ) [14] than HfON ( $\kappa \sim 22$ ) [10], which induces higher electric field in the SiO<sub>2</sub> layer, thus leading to a larger bending of energy band. Also, as shown in Fig. 3, the conduction-band offset of TaON to the Si substrate is 0.3 eV [15, 16], much smaller than the 2.0 eV [10] of HfON conduction-band offset to the Si substrate. Therefore, the electron tunneling distance is shorter in the TaON sample than the HfON sample at the same gate bias.

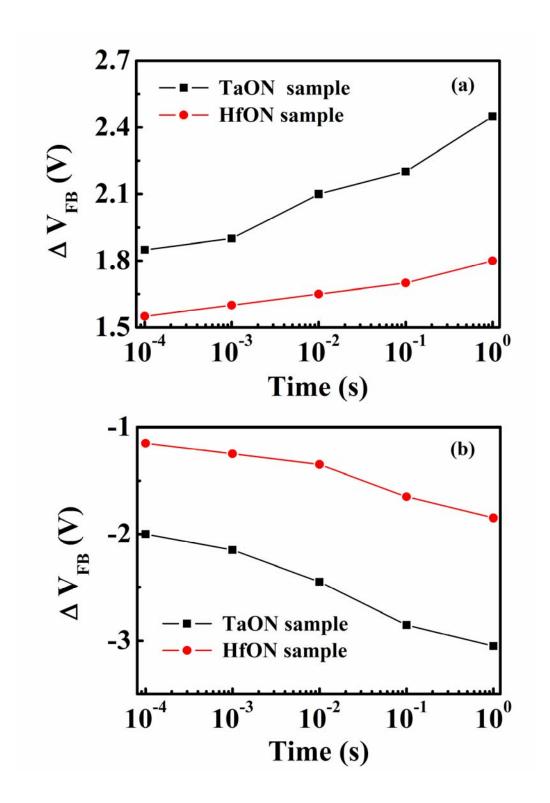

As shown in Fig. 4, the P/E transient performances are characterized in terms of  $\Delta V_{FB}$  as a function of time under P/E voltages of  $\pm 12~V_{.}$  Obviously, higher P/E speeds can be attained for the TaON sample than the HfON sample. After initial 100- $\mu$ s P/E voltages of +/-12 V, the flatband voltage shift is 1.85 V/-2.00 V for the TaON sample, and 1.55 V/-1.15 V for the HfON sample. Furthermore, the TaON sample then exhibits a larger change of  $\Delta V_{FB}$ . Since the CSL and BL are the same for the two devices, the above differences in performances should be mainly attributed to the difference in their stacked tunneling dielectrics. As

mentioned above, the conduction-band offset of TaON to the Si substrate is much smaller than that of HfON, and so the barrier height of the TaON layer is much smaller than that of the HfON layer. On the other hand, the larger dielectric constant of TaON (than that of HfON) results in a higher electric field in the SiO<sub>2</sub> layer of the TaON sample than the HfON sample due to the redistribution of the applied bias over the high-κ/low-κ layers [19]. Consequently, as shown in Fig. 3 (c) and (d), the TaON/SiO<sub>2</sub> DTL exhibits shorter tunneling distance than the HfON/SiO<sub>2</sub> DTL under the same bias, and electrons/holes can tunnel through the TaON/SiO<sub>2</sub> barrier more easily, thus resulting in significantly better P/E performances for the TaON/SiO<sub>2</sub> DTL than the HfON/SiO<sub>2</sub> DTL.

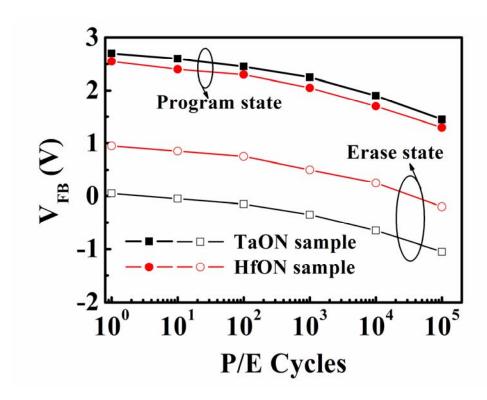

Fig. 5 shows the endurance characteristics of the two devices. The P/E cycle is performed at  $\pm$ 1 V with a pulse width of 100  $\pm$ 100  $\pm$ 100  $\pm$ 10 and then the V<sub>FB</sub> shift is extracted by measuring the C-V curve after 1,  $\pm$ 101,  $\pm$ 102,  $\pm$ 103,  $\pm$ 104, and  $\pm$ 105 P/E cycles. As can be seen in Fig. 5, the memory window is initially 2.65 V and 1.60 V for the TaON and HfON samples respectively and becomes 2.50 V and 1.50 V after  $\pm$ 105 cycles. The lower loss rate of memory window for the TaON sample (5.7%) than the HfON sample (6.3%) could be attributed to the better interface quality of the former, as confirmed in Fig. 1. Besides, the memory-window narrowing of the two devices is not severe, but the flatband voltage presents negative shift for both program and erase states. The negative

$V_{FB}$  shift for the erase state implies that some holes are probably trapped at/near the CSL/TaON (or HfON) interface during the P/E cycling, and the almost unchanged memory window indicates that the amount of electrons captured from the programming tunneling current basically remains the same [19].

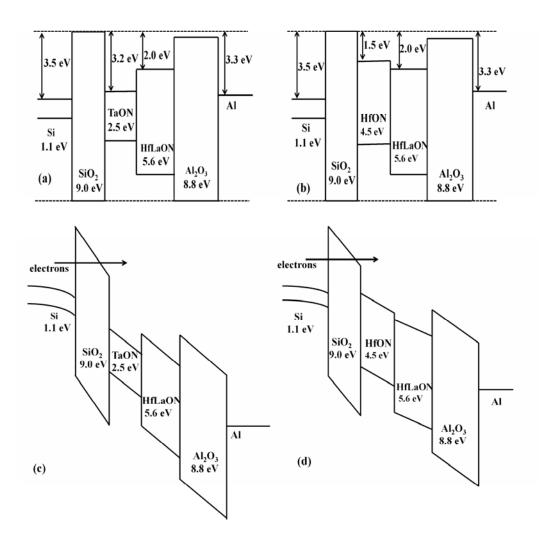

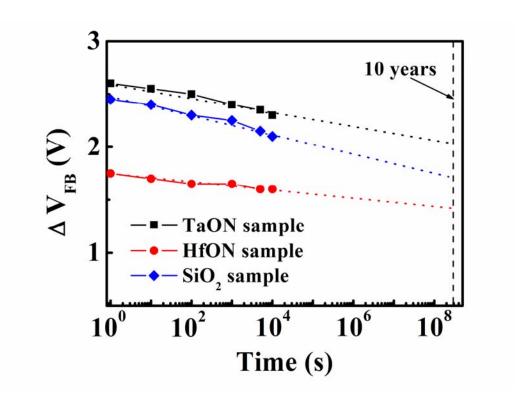

Fig. 6 is the retention characteristics of the two samples measured at room temperature after removing the program or erase voltage of +12 V or -12 V for 1 s. The V<sub>FB</sub> change is extracted by measuring the C-V curves at successive times from 1 s to 10000 s. In order to clarify the impact of the DTL on data retention, another device with only 4-nm SiO<sub>2</sub> as tunnel layer and the same CSL and BL as the TaON and HfON samples is also fabricated (denoted as SiO2 sample). It can be seen that the extrapolated 10-year memory window is 2.04 V, 1.41 V, and 1.92 V for the TaON, HfON and SiO2 samples, respectively (the initial window is 2.60 V, 1.75 V, and 2.90 V, respectively), corresponding to a charge-loss rate of 21.5%, 19.4%, and 33.8%, respectively. Although the TaON sample shows a slightly larger charge leakage than the HfON sample, it is still much smaller than that of the SiO2 sample, indicating that the larger physical thickness of the DTL can effectively improve the charge retention. Since TaON has better interface quality with SiO<sub>2</sub> than HfON (mentioned above), the slightly higher charge-loss rate for the TaON sample than the HfON sample should be mainly attributed to the band

offsets between the high-κ dielectric layer and the silicon substrate, as presented in Fig. 7. Since the conduction band of TaON/HfON is below/above that of HfLaON respectively, the TaON/ SiO<sub>2</sub> barrier exhibits slightly poorer ability in blocking electrons than the HfON/SiO<sub>2</sub> barrier. On the other hand, since more electrons are trapped in the CSL of the TaON sample, a slightly higher electric field is induced in the SiO<sub>2</sub> layer and thus slightly larger bending of energy band occurs during retention (see Fig. 7), which can further enhance the discharge of electrons from the CSL. However, in view of the large memory window, high P/E speeds and good endurance property, the stacked dielectric of TaON/SiO<sub>2</sub> is still a good choice for the DTL application.

#### 4, Conclusion

In summary, high-κ/low-κ dielectric stacks (TaON/SiO<sub>2</sub> and HfON/SiO<sub>2</sub>) as DTL have been investigated based on MONOS capacitors. As compared with the MONOS capacitor with HfON/SiO<sub>2</sub> DTL, the MONOS capacitor with TaON/SiO<sub>2</sub> DTL shows larger memory window, higher P/E speeds, and better endurance. The involved mechanisms are that TaON has larger dielectric constant and smaller band offset to the Si substrate than HfON, thus greatly enhancing charge injection from the Si substrate to the CSL. In addition, the better interface quality for the TaON/SiO<sub>2</sub> DTL than the HfON/SiO<sub>2</sub> DTL is responsible for the better endurance of the former. Furthermore, compared with the device using

only SiO<sub>2</sub> as tunneling layer, both devices with DTL can achieve improved retention characteristics due to the larger physical thickness of the tunnel layer. Therefore, the TaON/SiO<sub>2</sub> stack is a potential alternative as the DTL for MONOS charge-trapping flash memory applications.

## Acknowledgments

This work is financially supported by the National Natural Science Foundation of China (Grant no. 60976091) and the University Development Fund (Nanotechnology Research Institute, 00600009) of the University of Hong Kong.

#### References

- [1] S. Chung, Low Voltage and High Speed SONOS Flash Memory Technology, The Strategies and the Reliabilities, ECS Trans. 27 (2010) 73-78.

- [2] B. Govoreanu, P. Blomme, M. Rosmeulen, J. Van Houdt, and K. De Meyer, VARIOT: a novel multilayer tunnel barrier concept for low-voltage nonvolatile memory devices, IEEE Electron Device Lett. 24 (2003) 99-101.

- [3] Y.Q. Wang, W.S. Hwang, G. Zhang, G. Samudra, Y.C. Yeo, W.J. Yoo, Electrical characteristics of memory devices with a high-k HfO<sub>2</sub> trapping layer and dual SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> tunneling layer, IEEE Trans. Electron Devices 54 (2007) 2699-2705.

- [4] M. Lisiansky, A. Fenigstein, A. Heiman, Y. Raskin, Y. Roizin, L. Bartholomew, A. Gladkikh, R. Brener, I. Geppert, E. Lyakin, B. Meyler, Y. Shnieder, S. Yofis, and M. Eizenberg, Al<sub>2</sub>O<sub>3</sub>-SiO<sub>2</sub> stack with enhanced reliability, J. Vac. Sci. Technol. B (2009) 476-481.

- [5] B. Chakrabarti, H. Kang, B. Brennan, T. J. Park, K. D. Cantley, A. Pirkle, S. McDonnell, J. Kim, R. M. Wallace, and E. M. Vogel, Investigation of Tunneling Current in SiO<sub>2</sub>/HfO<sub>2</sub> Gate Stacks for Flash Memory Applications, IEEE Trans. Electron Devices. 58 (2011) 4189-4195.

- [6] T.-K. Kang, H.-W. Liu, F.-H. Wang, C.-L. Lin, T.-C. Liao, and W.-F.

- Wu, Improved characteristics for Pd nanocrystal memory with stacked HfAlO-SiO<sub>2</sub> tunnel layer, Solid-State Electron. 61(2011) 100-105.

- [7] J. Oh, H. Na, I. S. Mok, J. Kim, K. Lee, and H. Sohn, Physical and electrical properties of band-engineered SiO<sub>2</sub>/(TiO<sub>2</sub>) (x) (SiO<sub>2</sub>)(1-x) stacks for nonvolatile memory applications, Appl. Phys. A 108 (2012) 679-684.

- [8] L. Liu, J. P. Xu, F. Ji, X. D. Huang, and P. T. Lai, A Novel MONOS Memory With High-κ HfLaON as Charge-Storage Layer, IEEE Trans. Device Mater. Relia. 11 (2011) 244-247.

- [9] G. D. Wilk, R. M. Wallace, and J. M. Anthony, High-κ gate dielectrics: Current status and materials properties considerations, J. Appl. Phys. 89 (2011) 5243-5275.

- [10] X. D. Huang, L. Liu, J. P. Xu, P. T. Lai, Improved charge-trapping properties of HfYON film for nonvolatile memory applications in comparison with HfON and  $Y_2O_3$  films, Appl. Phys. Lett. 99 (2011) 112903-3.

- [11] M. Copel, N. Bojarczuk, L.F. Edge, S. Guha, Stability of terbium scandate on Si(100), Appl. Phys. Lett. 97 (2010) 182901-3.

- [12] Y.X. Liu, S. Il Shim, X.W. Wang, L.S. Lee, M.J. Tsai, T.P. Ma, High-quality high-k WON formed with plasma jet assisted PVD process and application as tunnel dielectric for flash memories, Microelectron. Eng. 85 (2008) 45-48.

- [13] P. Li, W. Fan, Y. Li, H. Sun, X. Cheng, X. Zhao, M. Jiang, First-Principles Study of the Electronic, Optical Properties and Lattice Dynamics of Tantalum Oxynitride, Inorg. Chem. 49 (2010) 6917-6924.

- [14] K. Kato, H. Toyota, Y. Jin, T. Ono, Characterization of tantalum oxy-nitrides deposited by ECR sputtering, Vacuum 83 (2008) 592-595.

- [15] C.Y. Kang, Barrier engineering in metal-aluminum oxide-nitride-oxide-silicon (MANOS) flash memory: Invited, Curr. Appl. Phys.10 (2010) e27-e31.

- [16] W.J. Chun, A. Ishikawa, H. Fujisawa, T. Takata, J.N. Kondo, M. Hara, M. Kawai, Y. Matsumoto, K. Domen, conduction and valence band positions of Ta<sub>2</sub>O<sub>5</sub>, TaON, and Ta<sub>3</sub>N<sub>5</sub> by UPS and electrochemical methods, J. Phys. Chem. B 107 (2003) 1798-1803.

- [17] L. Liu, J. P. Xu, J. X. Chen, F. Ji, X. D. Huang, and P. T. Lai, Ultrathin HfON/SiO2 dual tunneling layer for improving the electrical properties of metal-oxide-nitride-oxide-silicon memory, Thin Solid Films 524 (2012) 263-267.

- [18] P.-H. Tsai, K.-S. Chang-Liao, T.-Y. Wu, T.-K. Wang, P.-J. Tzeng, C.-H. Lin, L.-S. Lee, M.-J. Tsai, Novel SONOS type nonvolatile memory device with stacked tunneling and charge trapping layers, Solid-State electron. 52 (2008) 1573-1577.

- [19] T. Lee, S.K. Banerjee, Device characteristics of HfON charge-trap layer nonvolatile memory, J. Vac. Sci. Technol. B 28 (2010) 1005-1010.

### **Captions:**

Fig. 1 C-V curves of the MIS capacitors with Al/TaON/SiO<sub>2</sub>/Si and Al/HfON/SiO<sub>2</sub>/Si structures swept in bi-directions under +/-4 V sweeping voltages.

Fig. 2 Memory window of the two samples under different P/E voltages for 1 s.

Fig. 3 Energy band diagrams of TaON sample (a) and HfON sample (b) under flat band conditions, and TaON sample (c) and HfON sample (d) under programming states.

Fig. 4 The P/E transient performances of the two samples in terms of  $\Delta V_{FB}$  as a function of time at P/E voltages of  $\pm$  12 V: (a) program state and (b) erase state.

Fig. 5 Endurance characteristics of the two devices, with the P/E cycle performed at  $\pm$ 12 V for 100  $\mu$ s /100  $\mu$ s, respectively.

Fig. 6 Retention characteristics of the three samples measured at room temperature after removing 1-s P/E voltages at +/-12 V.

Fig. 1 J.X. Chen

Fig. 2 J.X. Chen

Fig. 3 J.X. Chen

Fig. 4 J.X. Chen

Fig. 5 J.X. Chen

Fig. 6 J.X. Chen

Fig. 7 J.X. Chen