### **Aalborg Universitet**

Investigation on the degradation indicators of short-circuit tests in 1.2 kV SiC MOSFET power modules

Du, He; Reigosa, Paula Diaz: Iannuzzo, Francesco; Ceccarelli, Lorenzo

Published in: Microelectronics Reliability

DOI (link to publication from Publisher): 10.1016/j.microrel.2018.06.039

Creative Commons License CC BY-NC-ND 4.0

Publication date: 2018

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA):

Du, H., Reigosa, P. D., lannuzzo, F., & Ceccarelli, L. (2018). Investigation on the degradation indicators of short-circuit tests in 1.2 kV SiC MOSFET power modules. *Microelectronics Reliability*, 88-90, 661-665. https://doi.org/10.1016/j.microrel.2018.06.039

### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Investigation on the degradation indicators of short-circuit tests in 1.2 kV SiC MOSFET power modules

H. Du\*, P.D. Reigosa, F. Iannuzzo, L. Ceccarelli

Center of Reliable Power Electronics, Department of Energy Technology, Aalborg University, Denmark

### **Abstract**

This paper provides a comprehensive investigation on both static characteristics and short-circuit performance of 1.2 kV SiC MOSFET power modules with 2<sup>nd</sup> generation planar technology. The experimental approach is based on the static characteristics measurements and the short-circuit tests with gradual increase of pulse time duration. If any variation of the static characteristics appears, the time duration of next short-circuit tests would keep the same with the last pulse duration (approach 1) or increase continuously (approach 2). The results of the short-circuit waveforms show a gate degradation which is further confirmed with the measurement of the gate leakage current. Additionally, other degradation indicators, including positive shift of threshold voltage, drain leakage current and on-state resistance increase are evidenced and discussed in this paper. These can be used for early prediction of the degradation and failure in the short-circuit conditions.

### 1. Introduction

Silicon Carbide (SiC) power electronic devices are now considered as the key components for future applications due to their superior physical properties compared with the silicon devices (i.e. increased electric field strength, thermal conductivity and electron velocity) [1]. However, the reliability of SiC devices needs to be further evaluated since siliconbased devices have proven to be more reliable, especially under Short-Circuit (SC) conditions [2].

Many efforts have been carried out to analyse the performance of SiC MOSFETs during SC tests [3]. The change in drain current slope and the appearance of drain current tails at turn-off have been discussed in [4] and [5]. Moreover, the static characteristics before and after the SC tests have also been investigated; among these, the positive and negative shift of threshold voltage (V<sub>th</sub>) has been discussed in [6] and [7], respectively. The longer pulse time duration (t<sub>SC</sub>), larger number of repetitive short circuits (from 1 pulse to 100 pulses SC) and larger gate-source voltage (from +18 V/-5 V to +20 V/-5 V) during SC tests could aggravate the variation of threshold voltage at several hundred mV level [8].

Additionally, the on-state resistance  $(R_{ds,on})$  [9], gate leakage current  $(I_{OSS})$  [10] and drain leakage current  $(I_{DSS})$  [7] also vary after repetitive SC tests. Nevertheless, most of the previous works were focused on discrete devices; the degradation indicators and physical mechanisms of SiC MOSFET power modules in the SC conditions still need to be fully understood.

In this paper, the SC performance of commercial 1.2~kV/500~A SiC MOSFET power modules are presented. A gate degradation has been observed during the SC tests and the successive static characterizations. The impact of SC tests on the static characteristics, including threshold voltage ( $V_{th}$ ), gate leakage current ( $I_{GSS}$ ), drain leakage current ( $I_{DSS}$ ) and on-state resistance ( $R_{DS,on}$ ) have been measured and analysed. Finally, the effects of room-temperature recovery after SC tests have also been investigated for the first time.

### 2. Test setup and approaches

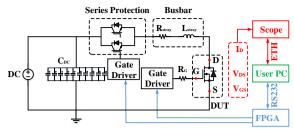

A 2.4 kV/ 10 kA Non-Destructive Tester (NDT) has been used for SC tests. The principle schematic

Fig. 1. Principle schematic of the Non-Destructive Tester (NDT).

Fig. 2. Picture of NDT setup in the laboratory.

and its appearance are shown in Fig. 1 and Fig. 2, respectively. The needed SC energy is provided by a high voltage power supply (DC) and the capacitor bank ( $C_{DC}$ ). A series protection, consisting of 4 IGBT power modules which are paralleled to increase the current capability, is used as a circuit breaker to

prevent explosions and allow failure analyses on the degraded samples. A 10 nH busbar has been designed to ensure low stray inductance. The Device Under Test (DUT) is a  $2^{nd}$  generation planar SiC MOSFET power module, having a half-bridge configuration and rated at 1.2 kV/ 500 A. The DUT is driven by a +20 V/-5 V gate voltage and the used gate resistance is equal to  $10~\Omega.$

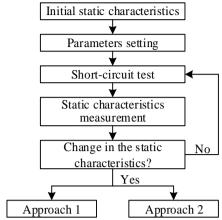

The experimental approach includes two parts: (i) static characterizations and (ii) SC tests, as shown in Fig. 3 and Fig. 4. Initially, the static characteristics are measured before the first SC test, including threshold voltage (V<sub>th</sub>), gate leakage current (I<sub>GSS</sub>), drain leakage current (I<sub>DSS</sub>) and on-state resistance (R<sub>DS,on</sub>). Then, the SC test is performed, and the drain-source voltage (V<sub>DS</sub>), gate-source voltage (V<sub>GS</sub>) and drain current (ID) waveforms are recorded. At the end of every test, a static characterization of the device is performed, then, the pulse time duration is increased gradually with fixed drain-source voltage (500 V) and room temperature. The SC test is stopped when a clear variation of the static characteristics is observed or the acquired SC waveforms show a clear gate damage (i.e. V<sub>GS</sub> drops).

Based on this experimental procedure, the results of the static characteristics after each SC test will be compared with the previous one. As can be seen in Fig. 3, when the pulse time duration  $(t_{SC})$  increases from the blue line to the green line, there is no obvious

## (i) Static characterizations (ii) Short-circuit tests $V_{DS}$ (kV) Vth IGS t (µs) $V_{GS}(V)$ $V_{GS}(\overline{V})$ t (µs) $_{\mathrm{DSS}}(\mathrm{A})$ IDSS $V_{GS}(V)$ RDS.on t (µs) $V_{DS}$

Fig. 3. Schematic of experimental approaches combined with both SC tests and static characteristics.

Fig. 4. Flow chart of experimental approaches combined with both SC tests and static characteristics.

change in the static characteristics. Thereafter, if the pulse time duration of SC test is further increased (from the green line to the red line), the variation of the static characteristics might be more obvious. At this point, two approaches are followed as shown in Fig. 4.

One approach named in the following as approach 1 is to keep the last SC pulse duration ( $t_{SC}$ ) and repeat the SC test with the same  $t_{SC}$  again and again. If the variation on the static characteristics gradually changes in the same direction, this  $t_{SC}$  can be recognized as the critical time at the fixed bias voltage and temperature condition.

The second method named as approach 2 is to increase the  $t_{SC}$  continuously no matter if there is any variation of the static characteristics. This approach allows to investigate the intrinsic SC duration limit at a given DC voltage.

### 3. Experimental results and discussion

### 3.1. Approach 1

At first, the pulse time duration ( $t_{SC}$ ) of SC test is increased gradually from 1  $\mu s$  to 10  $\mu s$  in steps of 1  $\mu s$  showing no obvious change of the SC waveforms or static characteristics. A little change on the static characteristics appears for the first time at  $t_{SC}=11~\mu s$ . However, a more obvious change has been recorded when the SC time duration is set to 11.2  $\mu s$ . This  $t_{SC}$  is considered as the critical SC time, thus, the pulse time is no longer increased and several SC tests have been performed again and again at the same conditions.

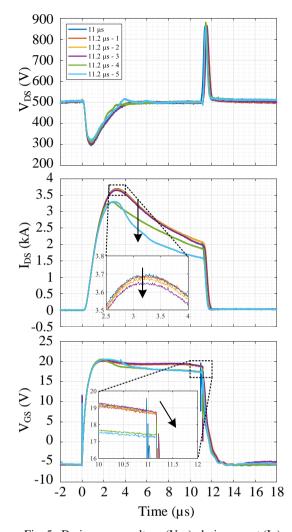

The drain-source voltage ( $V_{DS}$ ), gate-source voltage ( $V_{GS}$ ) and drain current ( $I_D$ ) during SC tests when the pulse time duration ( $t_{SC}$ ) is equal to 11  $\mu$ s and repetitive 11.2  $\mu$ s are presented in Fig. 5. The

Fig. 5. Drain-source voltage ( $V_{DS}$ ), drain current ( $I_D$ ) and gate-source voltage ( $V_{GS}$ ) waveforms at repetitive SC tests with 11.2  $\mu$ s pulse time duration ( $V_{DS}$ =500V).

critical energy ( $E_{\rm C}$ ) is 13.83 J at 11.2 µs.

It can be observed that the on-state gate voltage amplitude clearly decreases from the fourth repetition to the fifth repetition. Meanwhile, a reduction of drain current is observed especially in the fourth and fifth repetitions, which is in agreement with the decreasing gate-source voltage.

The formulated hypothesis is that the gate voltage drop corresponds to a gradual increase in the gate leakage current originating from conductive paths which are formed through the oxide during the SC tests and eventually cause a permanent gate damage. This is also consistent with the reduction of the SC current as presented in Fig. 5. Moreover, the observed variation of  $V_{\rm GS}$  and  $I_{\rm D}$  are in agreement with the results observed for discrete devices in [10] and [11], which are related to the degradation of gate structure.

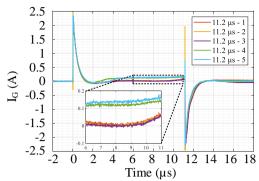

Fig. 6. Calculated gate current ( $I_G$ ) waveforms from the first to fifth repetitive SC test at 11.2  $\mu$ s ( $V_{DS}$ =500V).

Besides, another voltage probe is placed before the external gate resistance ( $R_G=10~\Omega)$  and the gatesource voltage including the  $R_G$  is measured during the SC tests in order to obtain the voltage drop on the  $R_G$ . Then, the gate current ( $I_G$ ) during SC tests can be calculated with the value of the gate resistance and the measured voltage drop across the gate resistance. Fig. 6 shows the gate current waveform with increasing SC repetitions. It is worth to note that the gate leakage current increases from 68 mA for the first repetition up to 160 mA for the fifth repetition at bias voltage of 500V and SC time duration of 11.2  $\mu s$ .

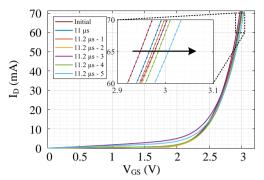

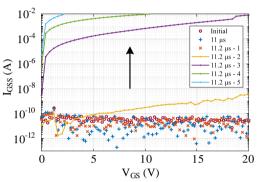

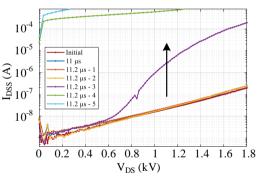

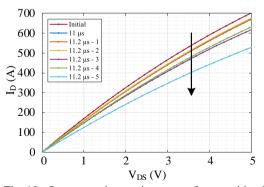

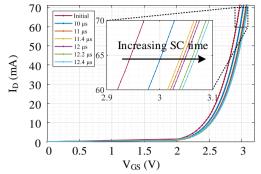

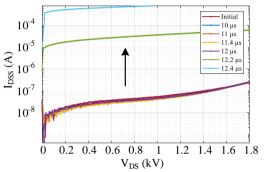

After each SC test, the static characteristics are measured, including the threshold voltage ( $V_{th}$ ), the gate leakage current ( $I_{DSS}$ ), the drain leakage current ( $I_{DSS}$ ) and the on-state resistance ( $R_{DS,on}$ ) which are presented from Fig. 7 to Fig. 10.

In Fig. 7, the threshold voltage shifts positively after each SC test at  $11.2~\mu s$ . Because of the increased oxide conductivity, the effective gate voltage on the device is slightly reduced when the threshold voltage is measured, which ends up in an equivalent threshold voltage shift.

The results of Fig. 8 confirm that the gate leakage current increases gradually. An obvious increase of  $I_{GSS}$  is observed after the second SC test at 11.2  $\mu$ s, which keeps increasing after each SC test, resulting in 0.1 A with the fifth repetitive SC test at 11.2  $\mu$ s.

Similarly, the drain leakage current and the onstate resistance increases after the third SC test at 11.2  $\mu s$ , as shown in Fig. 9 and Fig. 10, respectively. These results indicate that the gate degradation in turns affects the drain leakage path and leads to the reduction of  $V_{GS}$  when the  $I_D\text{-}V_{DS}$  characteristics (onstate resistance) is measured.

### 3.2. Approach 2

The second approach consists in increasing the SC time, even if the static characteristics vary. The

Fig. 7. Threshold voltage shifts after repetitive SC tests at  $11.2 \ \mu s \ (V_{DS}=20 \ V)$ .

Fig. 8. Gate leakage current increases after repetitive SC tests at 11.2 us.

Fig. 9. Drain leakage current increases after repetitive SC tests at  $11.2 \mu s$ .

Fig. 10. On-state resistance increases after repetitive SC tests at  $11.2 \mu s$  ( $V_{GS}$ =20V).

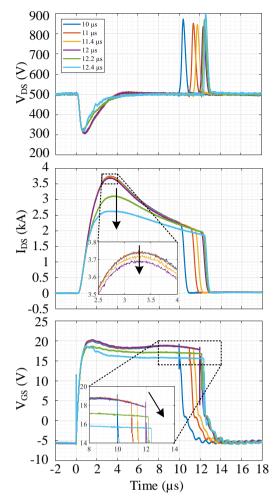

Fig. 11. Short-circuit waveforms including drain-source voltage ( $V_{DS}$ ), drain current ( $I_D$ ) and gate-source voltage ( $V_{GS}$ ) from the experiment at 10  $\mu$ s to 12.4  $\mu$ s.

drain-source voltage ( $V_{GS}$ ), gate-source voltage ( $V_{GS}$ ) and drain current ( $I_D$ ) waveforms during the SC tests from 10  $\mu$ s to 12.4  $\mu$ s are shown in Fig. 11. The  $t_{SC}$  was stopped at 12.4  $\mu$ s because of a large  $V_{GS}$  drop.

The static characteristics measured after each SC test show a positive shift of the threshold voltage and the increase of drain leakage current as they are presented in Fig. 12 and Fig. 13, respectively.

The results of the SC waveforms and the static characteristics show the same trends when compared to the first approach, which also confirms the formulated hypothesis of gate degradation.

Besides, the reduction of the drain current during SC tests is verified by the gate-source voltage decrease according to the Eq. 1 when the  $V_{DS}$  is much larger than  $(V_{CS} - V_{th})$

$$\begin{split} \text{larger than } (V_{GS} - V_{th}). \\ I_D &= \frac{1}{2} \cdot \kappa \cdot (V_{GS} - V_{th})^2 \end{split} \tag{1}$$

Fig. 12. Threshold voltage shifts vs. SC time duration  $(V_{DS}=500V)$ .

Fig. 13. Drain leakage current vs. SC time duration  $(V_{DS}=500 \text{ V})$ .

Fig. 14. Gate leakage current decreases 14 days after the last SC test.

The value of  $\kappa$  calculated by the SC waveform of approach 2 at 12  $\mu s$  is 27.48 when the drain current ( $I_D$ ) achieves the peak. In this case, the  $I_D$  is 3.695 kA and the  $V_{GS}$  at this moment is 19.480 V ( $V_{th}$  is equal to 3.08 V after this SC test).

Then, for the SC test at 12.2  $\mu$ s, the  $V_{GS}$  is 18.154 V ( $V_{th}$  is equal to 3.093 V) and the  $I_D$  calculated by the same  $\kappa$  is 3.116 kA, which is consistent with the experimental result (3.117 kA). Similarly, the calculated  $I_D$  (2.586 kA) from the SC test at 12.4  $\mu$ s agrees with the experimental results (2.630 kA), when the  $V_{GS}$  is 16.820 V and the  $V_{th}$  is 3.099 V.

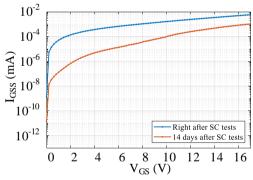

### 4. Room-temperature recovery

The static characteristics of DUT have been measured again 14 days after the last SC test. The variation of gate leakage current, compared with the results obtained right after the SC tests, are shown in Fig. 14.

The results shown in Fig. 14 indicate that the gate oxide damage has a recovery trend. According to the literature, bias-temperature stress-activated defects partially can take place and recover at room temperature in time scales of weeks [12] and the room-temperature recovery would be extensively studied as the next step.

### 5. Conclusions

This paper shows the impact of the short-circuit events on the static characteristics of SiC MOSFET power module with 2<sup>nd</sup> generation and planar technology. The degradation indicators, including the positive shift of threshold voltage, the increase of gate leakage current, drain leakage current and on-state resistance, are analysed following two approaches. The first approach is to apply the same short circuit pulse once a variation of the static characteristics is detected. The second approach is to gradually increase the short circuit pulse even if the static characteristics vary. The results of both approaches show the same trends and confirm that the gate structure can become degraded with a few short circuit tests. The hypothesis of a conducting path formed through the oxide is confirmed by experimental measurements. The gate leakage current is measured again after 14 days, proving that a bias-temperature stress-activated defects come into play.

### References

- M. Nawaz, K. Ilves, Replacing Si to SiC: Opportunities and challenges, Eur. Solid-State Device Res. Conf. 2016, pp. 472–475.

- [2] L. Ceccarelli, P.D. Reigosa, F. Iannuzzo, F. Blaabjerg, A survey of SiC power MOSFETs short-circuit robustness and failure mode analysis, Microelectron. Reliab. 76–77 (2017) 272–276.

- [3] P.D. Reigosa, F. Iannuzzo, H. Luo, F. Blaabjerg, A short-circuit safe operation area identification criterion for SiC MOSFET power modules, IEEE Trans. Ind. Appl. 53 (2017) 2880–2887.

- [4] S. Mbarek, P. Dherbécourt, O. Latry, F. Fouquet, Short-circuit robustness test and in depth microstructural analysis study of SiC MOSFET, Microelectron. Reliab. 76–77 (2017) 527–531.

- [5] G. Romano, L. Maresca, M. Riccio, V. D'Alessandro, G. Breglio, A. Irace, A. Fayyaz, A. Castellazzi, Short-circuit failure mechanism of SiC power MOSFETs, IEEE 27th Int. Symp. Power Semicond. Devices IC's (ISPSD) 2015, pp. 345–348.

- [6] E.P. Eni, S. Beczkowski, S. Munk-Nielsen, T. Kerekes, R. Teodorescu, R.R. Juluri, B. Julsgaard, E. Vanbrunt, B. Hull, S. Sabri, D. Grider, C. Uhrenfeldt, Short-circuit degradation of 10-kV 10-A SiC MOSFET, IEEE Trans. Power Electron. 32 (2017) 9342–9354.

- [7] X. Zhou, H. Su, Y. Wang, R. Yue, G. Dai, J. Li, Investigations on the degradation of 1.2-kV 4H-SiC MOSFETs under repetitive short-circuit tests, IEEE Trans. Electron Devices. 63 (2016) 4346– 4351.

- [8] L. Fursin, X. Li, Z. Li, M. O'Grady, W. Simon, A. Bhalla, Reliability aspects of 1200V and 3300V silicon carbide MOSFETs, IEEE 5th Work. Wide Bandgap Power Devices Appl. (WiPDA) 2017, pp. 373–377.

- [9] T.T. Nguyen, A. Ahmed, T. V. Thang, J.H. Park, Gate oxide reliability issues of SiC MOSFETs under short-circuit operation, IEEE Trans. Power Electron. 30 (2015) 2445–2455.

- [10] A. Castellazzi, A. Fayyaz, L. Yang, M. Riccio, A. Irace, Short-circuit robustness of SiC power MOSFETs: Experimental analysis, Proc. Int. Symp. Power Semicond. Devices ICs (ISPSD) 2014, pp. 71–74.

- [11] D. Othman, S. Lefebvre, M. Berkani, Z. Khatir, A. Ibrahim, A. Bouzourene, Robustness of 1.2 kV SiC MOSFET devices, Microelectron. Reliab. 53 (2013) 1735–1738.

- [12] A.J. Lelis, R. Green, D.B. Habersat, M. El, Basic mechanisms of threshold-voltage instability and implications for reliability testing of SiC MOSFETs, IEEE Trans. Electron Devices. 62 (2015) 316–323.