## Ryerson University Digital Commons @ Ryerson

Theses and dissertations

1-1-2011

# Analysis and architecture design of scalable fractional motion estimation for H.264 encoding

Jasmina Vasiljevic Ryerson University

Follow this and additional works at: http://digitalcommons.ryerson.ca/dissertations

#### Recommended Citation

Vasiljevic, Jasmina, "Analysis and architecture design of scalable fractional motion estimation for H.264 encoding" (2011). *Theses and dissertations*. Paper 709.

This Thesis is brought to you for free and open access by Digital Commons @ Ryerson. It has been accepted for inclusion in Theses and dissertations by an authorized administrator of Digital Commons @ Ryerson. For more information, please contact bcameron@ryerson.ca.

## ANALYSIS AND ARCHITECTURE DESIGN OF SCALABLE FRACTIONAL MOTION ESTIMATION FOR H.264/AVC ENCODING

by

## Jasmina Vasiljević

#### A thesis

presented to Ryerson University

in partial fulfillment of the

requirements for the degree of

Master of Applied Science (MASc)

in the Program of

Electrical and Computer Engineering

Toronto, Ontario, Canada, 2011

©Jasmina Vasiljević, 2011

#### AUTHOR'S DECLARATION FOR ELECTRONIC SUBMISSION OF A THESIS

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Ryerson University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Ryerson University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be made electronically available to the public.

## Acknowledgments

I would like to thank my wonderful and strong family; my mother who selflessly encouraged, advised and fought for me every step of the way; my father who instilled in me an unquenchable thirst for science from a very young age; my brother who leads and inspires by example, continuously reminding me that no goal is out of reach; and finally to my soul mate, best friend and my *ljljic* – Davor Čapalija. I would also like to thank Professor Andy Ye for taking me on as a student and his help during the course of my study.

#### Abstract

## ANALYSIS AND ARCHITECTURE DESIGN OF SCALABLE FRACTIONAL MOTION ESTIMATION FOR H.264/AVC ENCODING

Jasmina Vasiljević

Master of Applied Science (MASc)

Department of Electrical and Computer Engineering

**Ryerson University**

Fractional Motion Estimation (FME) is an important part of the H.264/AVC video encoding standard. FME can significantly increase the compression ratio achievable by video encoders while improving video quality. However, it is computationally expensive and can consist of over 45% of the total motion estimation runtime. To maximize the performance and hardware utilization of FME implementations on Field-Programmable Gate Arrays (FPGAs), one needs to effectively exploit the inherent parallelism in the algorithm. In this work we explore two approaches to FME algorithm parallelization in order to effectively increase the processing power of the computing hardware. The first method is referred to as vertical scaling and the second horizontal scaling. In total, we implemented six scaled FME designs on a Xilinx Virtex-5 FPGA. We found that our best vertically scaled FME design exhibited a speedup of 8x over the horizontally scaled designs. Additionally, we conclude that scaling vertically within a 4x4 pixel sub-block is more efficient than scaling horizontally across several sub-blocks. As a result we were able to achieve higher video resolutions at lower hardware resource costs. In particular, it is shown that the best vertically scaled design can achieve 30 fps of QSXGA (2560x2048) video using 4 reference frames with only 25.5K LUTS and 28.7K registers.

## **Table of Contents**

| Table of Contents                                 | IV   |

|---------------------------------------------------|------|

| List of Tables                                    | VIII |

| List of Equations                                 | X    |

| List of Figures                                   | XII  |

| Chapter 1 – Introduction                          | 1    |

| 1.1 Thesis Objectives                             | 5    |

| 1.2 Thesis Organization                           | 7    |

| Chapter 2 – Background and Motivation             | 8    |

| 2.1 Introduction to Video                         | 8    |

| 2.2 Digital Video Compression                     | 10   |

| 2.3 Variable Block Size Motion Estimation (VBSME) | 12   |

| 2.4 Search Windows and Multiple Reference Frames  | 13   |

| 2.5 The Fractional Motion Estimation Algorithm    | 14   |

| 2.6 The FME Architecture                          | 17   |

| 2.7 Hardware Implementation                       | 19   |

| 2.7.1 Finite Impulse Response Filter              | 19   |

| 2.7.2 The 2-D Hadamard Transform                  | 20   |

| 2.8 Motivation                                            | 22 |

|-----------------------------------------------------------|----|

| 2.9 Chapter Summary                                       | 26 |

| Chapter 3 - The Scalable FME Architecture                 | 27 |

| 3.1 Interpolation Engine                                  | 31 |

| 3.1.1 Horizontal Interpolation Unit                       | 31 |

| 3.1.2 Vertical Interpolation Unit                         | 33 |

| 3.2 SATD Processing Unit                                  | 36 |

| 3.2.1 Vertical Scaling of the PU                          | 38 |

| 3.2.2 Residue Generators                                  | 40 |

| 3.2.3 The 2-D Hadamard Transform                          | 41 |

| 3.2.4 Absolute Function and Summation                     | 44 |

| 3.2.5 Horizontal Scaling of the PU                        | 45 |

| 3.3 Chapter Summary                                       | 48 |

| Chapter 4 - Design Space Exploration                      | 49 |

| 4.1 Block Decomposition                                   | 49 |

| 4.1.1 Block Decomposition for Vertically Scaled Designs   | 50 |

| 4.1.2 Block Decomposition for Horizontally Scaled Designs | 54 |

| 4.2 Data Redundancy                                       | 57 |

| 4.2.1 Calculating Data Redundancy                         | 57 |

| 4.2.2 Data Redundancy in Vertically Scaled Designs        | 60 |

|                                                           |    |

| 4.2.3 Data Redundancy in Horizontally Scaled Designs     | 61 |

|----------------------------------------------------------|----|

| 4.3 Hardware Utilization                                 | 61 |

| 4.3.1 Input Data Width Variance                          | 62 |

| 4.3.2 Throughput Variance                                | 63 |

| 4.3.3 Vertical Alignment                                 | 65 |

| 4.3.4 Calculating Hardware Utilization                   | 67 |

| 4.4 Processing Time                                      | 72 |

| 4.5 Chapter Summary                                      | 73 |

| Chapter 5 – Experimental Evaluation                      | 74 |

| 5.1 Target Device and Tools                              | 74 |

| 5.2 Performance Analysis                                 | 76 |

| 5.2.1 Hardware Implementation Results                    | 77 |

| 5.2.2 Scalability Analysis                               | 79 |

| 5.2.3 Frequency Analysis                                 | 86 |

| 5.3 Target Video Resolution Specifications               | 88 |

| 5.4 Chapter Summary                                      | 91 |

| Chapter 6 – Concluding Summary                           | 92 |

| 6.1 Comparative Study                                    | 93 |

| 6.2 Future Work                                          | 94 |

| Appendix A - Redundancy Analysis and Block Decomposition | 95 |

| Appendix B – Hardware Utilization of the Interpolation Engine | 97  |

|---------------------------------------------------------------|-----|

| Summary of Terms                                              | 100 |

| Glossary                                                      | 103 |

| References                                                    | 105 |

## **List of Tables**

| Table 1 - The FME Scaled Designs                                                        | :6 |

|-----------------------------------------------------------------------------------------|----|

| Table 2 - The Block Decomposition Schedule for the [M=1, N=1], [M=2, N=1], [M=4, N=1]   | 1] |

| Designs5                                                                                | 52 |

| Table 3 - The Block Decomposition Schedule for the [M=10, N=1] Design                   | 53 |

| Table 4 - The Block Decomposition Schedule for the [M=1, N=4] Design                    | 54 |

| Table 5 - The Block Decomposition Schedule for the [M=1, N=2] Design                    | 6  |

| Table 6 - Data Redundancy for Six FME Scaled Designs                                    | 59 |

| Table 7 – Data Redundancy Analysis and Block Decomposition for the [M=1, N=1] Design 6  | 50 |

| Table 8 – The Throughput Variance and PU Utilization of the [M=1, N=1] Base Design 6    | 55 |

| Table 9 - Hardware Utilization Summary6                                                 | 57 |

| Table 10 - Total Number of Clock Cycles Required for Processing 41 Subblocks            | 13 |

| Table 11- Implementation Results - Xilinx XC5VLX85T FPGA                                | 7  |

| Table 12 - Performance Analysis                                                         | 32 |

| Table 13 - Scalability Ranking 8                                                        | 35 |

| Table 14 - Target Video Resolution9                                                     | 0  |

| Table 15 - Comparison to Previous Work9                                                 | 13 |

| Table 16 - Redundancy Analysis and Block Decomposition Calculations for the [M=1, N=1   | ], |

| [M=2, N=1] and [M=4, N=1] Design                                                        | 15 |

| Table 17 - Redundancy Analysis and Block Decomposition Calculations for the [M=10, N=1] | 1] |

| Design9                                                                                 | )5 |

| Table 18 - Redundancy Analysis and Block Decomposition Calculations for the IM-1 N-7    | 21 |

| Design                                                                                    |

|-------------------------------------------------------------------------------------------|

| Table 19 - Redundancy Analysis and Block Decomposition Calculations for the [M=1, N=4]    |

| Design                                                                                    |

| Table 20 – Hardware Utilization of the Interpolation Engine for the [M=10, N=1] Design 97 |

| Table 21 - Hardware Utilization of the Interpolation Engine for the [M=4, N=1] Design 97  |

| Table 22 - Hardware Utilization of the Interpolation Engine for the [M=2, N=1] Design 98  |

| Table 23 - Hardware Utilization of the Interpolation Engine for the [M=1, N=1] Design 98  |

| Table 24 - Hardware Utilization of the Interpolation Engine for the [M=1, N=2] Design 99  |

| Table 25 - Hardware Utilization of the Interpolation Engine for the [M=1, N=4] Design 99  |

## **List of Equations**

| Equation 1 - Peak Signal to Noise Ratio                                               |

|---------------------------------------------------------------------------------------|

| Equation 2 - Half Pixel Generation                                                    |

| Equation 3 – Quarter Pixel Generation                                                 |

| Equation 4 – Generating the SATD Value                                                |

| Equation 5 - Half Pixel Range                                                         |

| Equation 6 – Half and Quarter Pixel Range                                             |

| Equation 7 - FIR Filter                                                               |

| Equation 8 – 1-D Hadamard Transform                                                   |

| Equation 9 – Hardware Optimized 1-D Hadamard Transform                                |

| Equation 10 - The Running Time of FME                                                 |

| Equation 11 – Total Number of Macroblocks per Video Frame                             |

| Equation 12 – Percent of Data Redundancy                                              |

| Equation 13 – The Total Number of Pixels Processed for all Subblock Types             |

| Equation 14 - The Total Number of Pixels Processed for all Subblock Types After Block |

| Decomposition                                                                         |

| Equation 15 – Interpolation Engine Utilization Example                                |

| Equation 16 - PU Utilization Example                                                  |

| Equation 17 - IE Utilization for the [M= 2, N=1] Design                               |

| Equation 18 – IE Utilization for the [M= 2, N=1] Design                               |

| Equation 19 - Hardware Utilization Approximation of the Interpolation Engine          |

| Equation 20 –Hardware Utilization Approximation for the Processing Unit               |

| Equation 21 – Total Number of Clock Cycles                           | 72 |

|----------------------------------------------------------------------|----|

| Equation 22 – Total Wall Clock Time                                  | 78 |

| Equation 23 - Macroblocks per Second                                 | 78 |

| Equation 24 - Cost-Performance Product                               | 79 |

| Equation 25 - Linear Scaling in Terms of the Cost-Performace Product | 79 |

| Equation 26 - Scalability Properties                                 | 80 |

| Equation 27 – Relative Hardware Resource Cost                        | 81 |

| Equation 28 - Speedup                                                | 81 |

| Equation 29 - Relative Efficiency                                    | 81 |

| Equation 30 - Macroblocks per Second                                 | 89 |

| Equation 31 - Frames per Second                                      | 89 |

## **List of Figures**

| Figure 1 - Various Video Formats and Resolutions                                | 9  |

|---------------------------------------------------------------------------------|----|

| Figure 2 - Motion Estimation.                                                   | 11 |

| Figure 3 – Encoding a Singe Frame with Different VBSME settings                 | 12 |

| Figure 4 - MB and Subblocks Sizes in VBSME                                      | 13 |

| Figure 5 - Half and Quarter Pixels                                              | 15 |

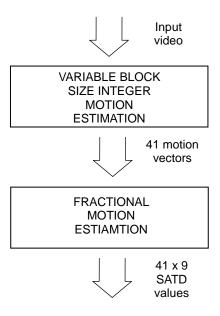

| Figure 6 - Motion Estimation Block                                              | 18 |

| Figure 7 - Pipelined Hardware Implementation of the FIR Filter                  | 20 |

| Figure 8 - The Hardware Implementation of the Optimized 1-D Hadamard Transform  | 21 |

| Figure 9 - The Input Array Sizes for 6 Scaled FME Designs                       | 28 |

| Figure 10 - The Scalable FME Architecture                                       | 30 |

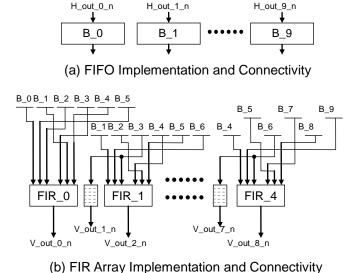

| Figure 11 - The H-IPU Connectivity at Row m and Column n                        | 32 |

| Figure 12 – Pixel Interpolation in Stage 1                                      | 32 |

| Figure 13 - The <i>n</i> th Scalable V-IPU                                      | 34 |

| Figure 14 - V-IPU for the [M=10, N=1] Design                                    | 35 |

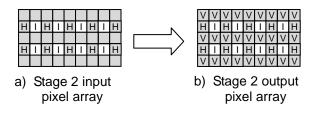

| Figure 15 – Pixel Interpolation in Stage 2                                      | 36 |

| Figure 16 - The Processing Unit Architecture                                    | 37 |

| Figure 17 - The Vertically Scaled PU Designs with Various Data Throughput Rates | 39 |

| Figure 18 - The Residue Generator                                               | 40 |

| Figure 19 - 2-D Hadamard Transform                                              | 41 |

| Figure 20 - Operation of the Transpose Shift Register for the [M=1, N=1] PU     | 42 |

| Figure 21 - The Absolute Function and Summation Units                           | 44 |

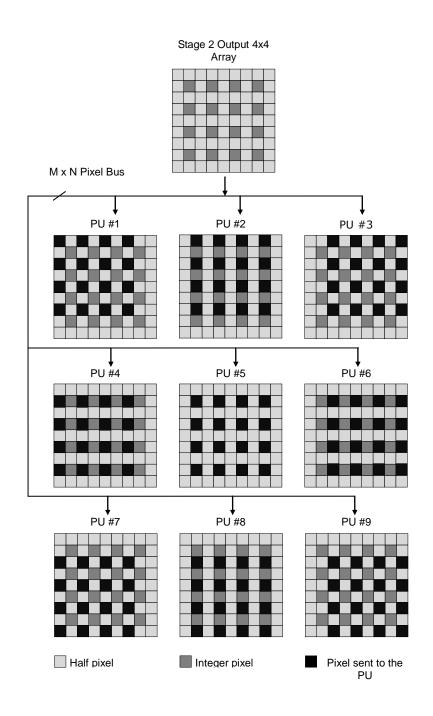

| Figure 22 - Pixel Layout at the Output of Stage 2 (V-IPUs)                                    | 45   |

|-----------------------------------------------------------------------------------------------|------|

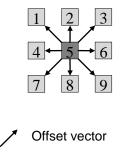

| Figure 23 - Nine Half Pixel Candidate Positions and Their Offset Vectors for One Integer Pixe | el46 |

| Figure 24 - Mapping a 4x4 Subblock to a Single Set of 9 PUs                                   | 47   |

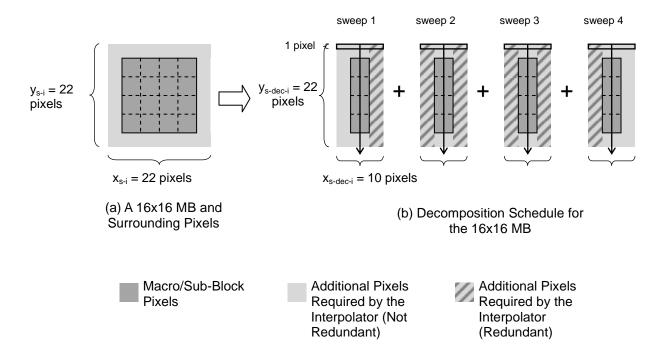

| Figure 25 - Decomposition Schedule for a 16 x 16 Block for the [M=1, N=1] Design              | 51   |

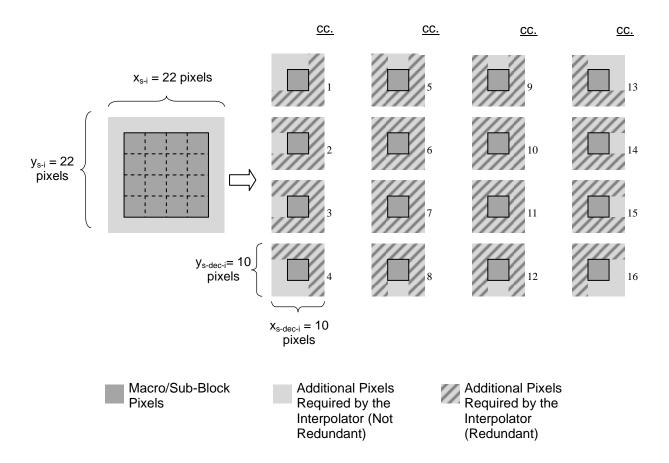

| Figure 26 - 16x16 Block Decomposition and Data Redundancy for the [M=10, N=1] Design          | 53   |

| Figure 27 - Hardware utilization for the [M=1, N=4] design for 16x16, 8x8, and 4x4 blocks     | 55   |

| Figure 28 - Decomposition Schedule for a 16 x 16 Block for the [M=1, N=2] Design              | 56   |

| Figure 29 - Timing Diagram for Processing a 4x4 Block Using the [M=1, N=1] Design             | 64   |

| Figure 30 - Data Alignment for [M=1, N=1], [M=2, N=1], [M=4, N=1] and [M=10, N=1]             | 66   |

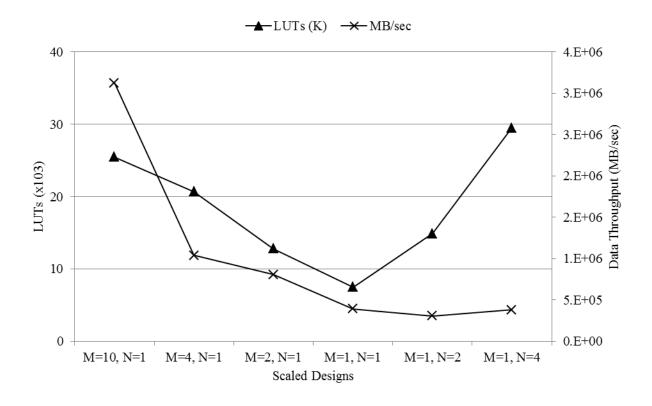

| Figure 31 - LUT Count Compared with Data Throughput                                           | 78   |

| Figure 32 - Product of Cost and Total Execution Time                                          | 80   |

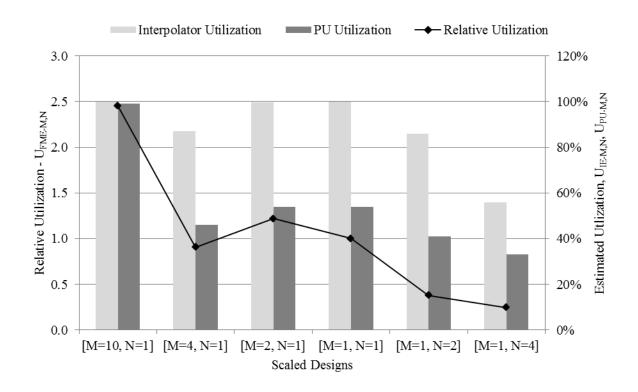

| Figure 33 – Measured Overall Relative Utilization and Estimated Utilization                   | 82   |

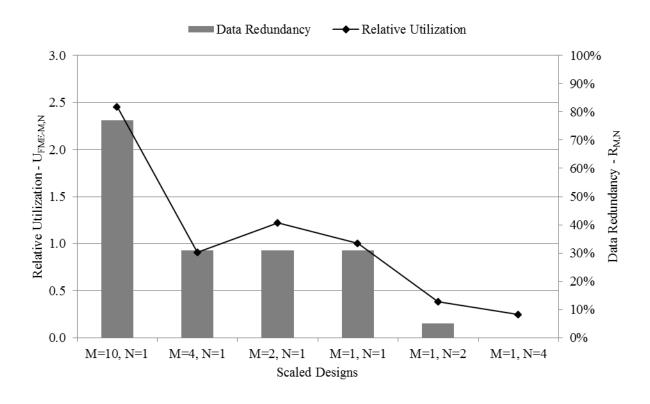

| Figure 34 – Relevant Utilization and Data Redundancy                                          | 83   |

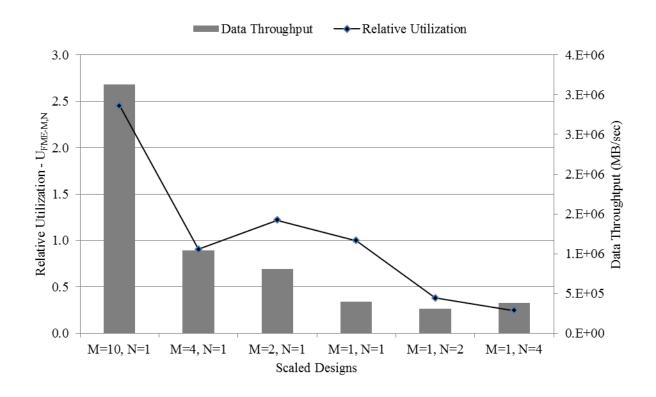

| Figure 35 – Relative Utilization and Data Throughput                                          | 84   |

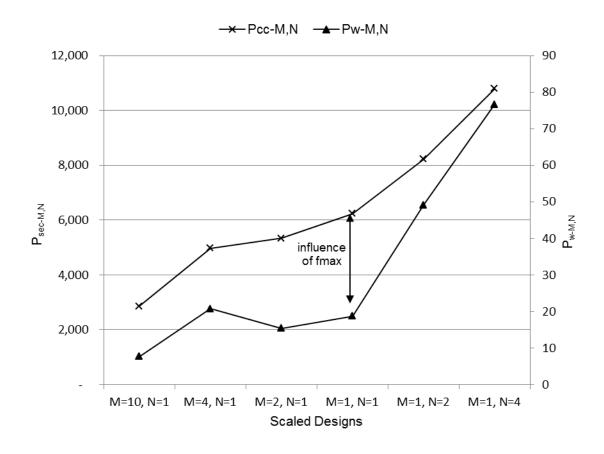

| Figure 36 - Effect of the Maximum Achievable Frequency on the Design Scalability              | 87   |

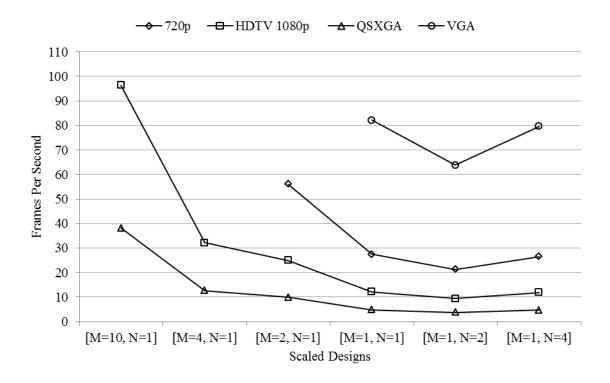

| Figure 37 - Frames per Second at Various Video Resolutions                                    | 90   |

#### **Chapter 1 – Introduction**

Motion Estimation (ME) is a video compression algorithm that removes spatial and temporal data redundancy between frames by using motion vectors (MVs) to track the motion of objects within video footage. Unlike previous encoding algorithms, the H.264/AVC standard offers the use of Fractional Motion Estimation (FME). This is an engine which fine-tunes MVs to sub-pixel granularities in order to achieve an enhanced video quality and a better compression ratio which reduces transfer stream bit-rates as well as the amount of video memory storage. Compared with previous video compression standards, such as H.263 and MPEG-2, the H.264/AVC encoding standard can achieve 49% and 64% bit-rate reductions respectively [1]; as well as a compression rate of 50:1 [53].

There exists a quantitative formal video quality measurement called the Peak Signal to Noise Ratio  $-PSNR_{dB}$ . The  $PSNR_{dB}$  depends on the mean squared error (MSE) between an impaired video frame and the original, based on the following equation:

$$PSNR_{dB} = 10\log_{10}\frac{(2^n - 1)^2}{MSE}$$

Equation 1 - Peak Signal to Noise Ratio

where n is the number of bits per pixel and MSE is the mean squared error [2].  $PSNR_{dB}$  can be calculated quickly and easily and is a widely used metric to compare the quality of compressed and decompressed video images. It has been measured that the FME can improve video quality by +4 dB [3].

The FME algorithm is an essential part of the H.264/AVC video compression standard. However, the FME algorithm is computationally expensive. Due to the high computing demand, many hardware architectures have been proposed to accelerate the computation of the FME algorithm. The large range of H.264/AVC engines vary from a free low-end Xilinx soft-core[4], to high-priced, high-performance designs aimed at the broadcasting industry, targeting custom FPGA/ASIC systems [5]. Further, the FME has been implemented on a variety of target architectures, for example: ASIC/FPGA [1][3][6]-[17], hybrid hardware/software systems [18] and GPUs[18][20].

The need for scalable high-performance encoding engines with efficient use of hardware resources have been previously recognized as a need [7][8][9][18][21][22]. These implementations use systolic arrays in order to achieve flexible scalable designs. They succeeded in providing a high degree of hardware utilization as well as data throughput rate. The parameterizable designs [7][8][9] allowed for setting of a variable which controls the size of the pixel block to be processed. While these designs are capable of handling a range of variable pixel array sizes, they require the user to commit to particular block dimensions at compile time. These works do not address the scalability and utilization challenges which arise when processing all 7 variable sized blocks at the same time. In addition, some designs evaluate MVs at a quarter-pixel resolution [18] in a single step whereas the refinement can be divided into two stages. A two stage refinement would involve Unnecessary computation can be saved by first evaluating the best half pixel, followed by refining it to a quarter pixel resolution.

Certain implementations focused on optimizing the pixel interpolation [23], while others on the distortion evaluation units [24]. Further, approximation algorithms have been implemented to simplify the computational complexity FME by abstracting away the need for

pixel interpolation [25], although they do suffer a video quality penalty.

A number of works have implemented full support of variable block sizes (VBS) [1][3][10][16]. They are capable of processing all 7 of the variable sized blocks. Processing of VBS gives rise to various hardware utilization problems and data flow trade-offs. In addition, these implementations are not scalable and easily parameterizable. They are capable of processing 4, 8 or 16 pixels from the same row of a macroblock, thus possessing horizontal parallelism. We found however, that expanding parallelism only along the row can potentially degrade hardware utilization. In this work, we explore an increase in parallelism along a column of pixels as well.

In this work, we perform a scalability study of FME with the goal of gaining performance while minimizing the use of additional hardware resources. Our target architecture is an FPGA which is capable of providing custom fine-grain optimizations with regards to parallelization. In our work, we describe the design and implementation of the Interpolation Engine (IE), as well as the distortion computation units (Processing Units - PUs). We implement a parameterizable, scalable design, capable of processing all 7 types of variable block sizes. We implement and analyze a total of six scalable FME architectures, with our formulated analysis method. In addition, we present results for both, the IE and the PU together, and analyze their interaction with respect to data flow, hardware utilization and data redundancy in order to identify the optimal high-performing FME engine.

Due to the high computing demand, many hardware architectures have been proposed to accelerate the computation of the FME algorithm. Most of the architectures, however, have been implemented in Application Specific Integrated Circuit (ASIC) technology. Except for the work in [15][26], which implements a non-scalable version of FME on FPGAs, limited information

exists on performance and algorithm-architecture mapping exploration of the FME onto reconfigurable technologies. In this work, we perform a scalability study of FME on FPGAs with the goal of gaining performance while minimizing the use of additional resources.

Scalability is a concept frequently used to indicate the *quality* of parallel systems. Many engineering issues emerge when scaling and implementing an algorithm. Many of these issues are best dealt with at the algorithmic level, rather than by manually modifying the code for each individual implementation. The fastest scaled implementation can depend on many factors, such as target architecture, amount of parallelism, software environment and memory hierarchy. A good understanding of the concept of scalability can be used to select the best algorithm-architecture combination for a problem. By determining the performance of an algorithm with a particular architecture and varying amounts of resources, one can determine the maximum speedup which can be obtained for a minimum amount of additional recourses.

This work provides an insight into the influence of the algorithm on the architecture and vice-versa to enable us to understand the scalability of the FME algorithm-architecture pair. We develop and present an empirical approach in order to quantify and evaluate two different scalability approaches and a total of six scaled FME implementations. We also present our new innovative approach to FME scalability, vertical scaling, and compare it against the traditional implementation of horizontal scaling.

The investigation of scalable FME implementations on FPGAs is particularly important since the programmability of FPGAs encourages design reuse and can greatly enhance the upgradability of digital systems. Scalability eases the creation of highly flexible FPGA-based encoding systems which can accommodate a multitude of existing standards as well as support the emergence of new standards. An efficient scalable FME implementation can be incorporated

into a single FPGA solution targeting low cost, low-resolution applications as well as multiple FPGA designs targeting high performance high-resolution applications.

#### 1.1 Thesis Objectives

The objective of this work is to develop and implement a scalable FME engine. We aim to analyze the trade scalability trade-offs and quantify them in order to find a suitable scalability approach.

#### 1.2 Thesis Contributions

In this work, we perform a scalability study of FME by increasing parallelism along a column of pixels as well as along a row of pixels. We define a set of overhead functions associated with the different algorithmic and architectural characteristics in order to quantify the scalability of the FME engine as a parallel system. Based on the results, we design and implement a scalable high-performance FME algorithm platform. We isolate the algorithmic and architectural overheads by examining their influence on the processing time and the use of hardware resources. Our design is then implemented on an FPGA which is capable of providing custom fine-grain optimizations with regards to parallelization. In summary, our contributions are four-fold:

- 1. Introduced a vertical scaling approach

- 2. Developed hardware utilization analysis metrics for scalable FME designs

- 3. Performed direct quantitative comparison between vertical and horizontal FME implementations

4. Implemented a parameterizable design, changeable at compile time to instantiate various scalable FME architectures

We describe the design and implement the Interpolation Engine (IE) and the distortion computation units (referred to as Processing Units PUs), capable of processing all 7 types of variable block sizes. The results for both the IE and the PU are presented. Their interaction between data flow, hardware utilization and data redundancy are analyzed in order to identify the best configuration for high-performing FME engines. Designs that implement a more complete H.264/AVC system typically choose an FME architecture that suits a pipeline work balance between the IME and FME. In order to reduce the clock cycles required to process the 41 subblocks. So far, designers have chosen a faster implementation by increasing parallelism horizontally. We argue and show that increasing parallelism vertically is significantly more efficient in terms of hardware resources and achieved throughput, and therefore urge designers to reconsider their choices taking into account analysis presented in this work. Looking at our scalability curve and cost-performance product derived in Chapter 5, we conclude that in terms of resource use the designer is better off choosing any of the three vertically scaled designs over the horizontally scaled versions. While previous works have implemented a more complete H.264/AVC system, our work was developed based on a bottom-up approach, starting at understanding all of the FME design trade-offs. Thus, in future work, the relationship between integer motion estimation (IME) and FME can be efficiently exploited through the application of the analytical methods developed in this work.

Finally, a four page conference paper version of this work was published in [54], and a journal was published in [55].

#### 1.3 Thesis Organization

This thesis is organized as follows. Chapter 2 provides a summary of background information on video compression as well as a few of the motion estimation features which are specific and new to the H.264/AVC standard, including the motivation behind our work. Our newly developed scalable FME architecture is presented in Chapter 3, and Chapter 4 discusses the design space exploration where we formulate our design evaluation metrics. Chapter 5 presents details of the experimental setup and implementation results, and then moves on to describe our empirical study of the specific scalability challenges and analysis of performance trade-offs. Finally, Chapter 6 concludes by summarizing the presented work and related research, along with future work which can build upon the current results.

## **Chapter 2 – Background and Motivation**

This chapter describes video and compression related background, including technical details required for estimation of computational complexity.

#### 2.1 Introduction to Video

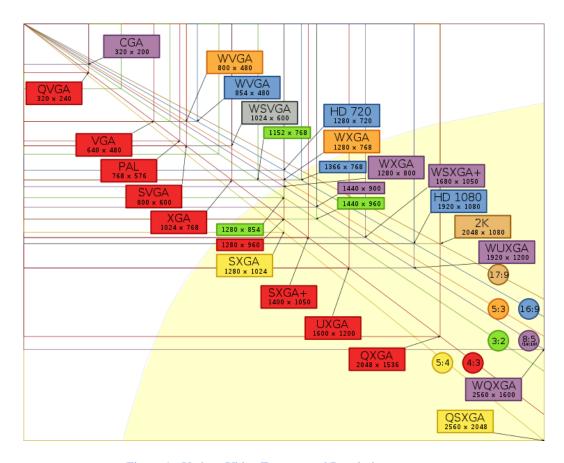

Many digital video formats exist, varying in their target resolutions, colour space, chrominance sub-sampling ratios and signal sampling frequencies. Figure 1 shows a sample map of the rich variety of available formats.

Figure 1 - Various Video Formats and Resolutions

The mathematical representation of a set of colours is called a colour space [27]. Popular models are RGB, used in computer graphics, YIQ, YUV or YCbCr, popular in video broadcasting systems, and CMYK, used in colour printing. The YCbCr format has one luminance (Y) and two chrominance components (Cb and Cr). The luminance and chrominance components are quantized as 8-bit data values. The 8-bit luminance value represents a single unsigned integer byte of data, ranging from 0 to 255, where 0 corresponds to a purely black pixel and 255 to a purely white pixel [27].

In this work we deal with the luminance component only which is what motion estimation engines utilize for encoding. This design choice stems from the observation that the human eye is more sensitive to changes in brightness then colour. What this means is that when

humans take in the view of an image as a whole, a lack of colour does not adversely affect the ability to discern motion.

#### 2.2 Digital Video Compression

Digital video compression is performed by identifying and removing data redundancy in order to reduce transmission bandwidth and overall file size. This reduction can be achieved on two separate fronts: spatial, across a search region of a single frame, and temporal, across multiple frames.

For example, in a single frame, spatial redundancy can be performed on a large consistent background shade of blue sky. In this case the large repetitive area can be compressed through the use of various discreet cosine transformations which map an image in terms of its light or colour intensities [28]. Since this type of compression does not involve motion estimation, this topic is not examined further.

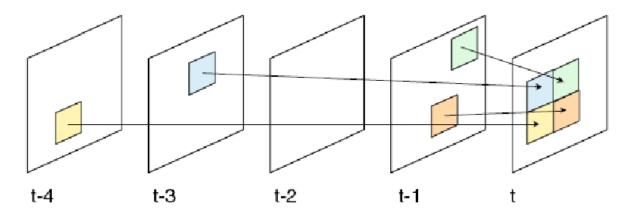

Temporal compression is achieved through the removal of data repeated over a given sequence of frames, for example background objects which are not likely to change over the course of a given footage. Their redundancy can be taken advantage of by transmitting the object's motion from frame to frame, which can result in considerable data compression. The recording of motion is done in the form of MVs. Consequently, the motion estimation algorithm is the process of deriving suitable MVs which best describe the movement of objects from one frame to the next.

Each video frame is processed in terms of macroblocks (MBs), which are a 16x16 pixel arrays. A frame that is in the process of being encoded is called a current frame. The goal of the

ME engine is to describe the current frame in terms of MBs already in the current frame or within a set of reference frames. The reference frames may come before or after the current frame as they are all buffered inside a decoder and can be referenced as needed. The ME algorithm scans potential reference MBs in order to find the most suitable one for the current MB. Once the ME engine decides on the optimal match, it encodes the current block of pixels as an MV. The MV is calculated as the spatial and temporal displacement between the current and reference MBs. Sample MVs are shown in Figure 2.

Figure 2 - Motion Estimation

Notable new features of the H.264/AVC compression standard include Variable Block Size Motion Estimation (VBSME) and Multiple Reference Frame (MRF) searching. Both of these features increase the computational complexity by expanding the search space and hence the required calculations. MRF enables the engine to capture periodic motion across a number of reference frames and from it extract data redundancy. VBSME has the capability of detecting motion of smaller objects but can increase the transmission bandwidth in order to deliver a higher quality stream and finer granularity of motion.

Currently, these techniques have been widely implemented as the basis of the H.264/AVC video standard. With the optimization and enhancement of these techniques, as well as others,

the standard has been able to achieve compression ratios as high as 60:1 as well as improved video quality [28]. The development of H.264/AVC was done by the International Telecommunications Union – Telecommunications Standardization Sector (ITU – T) Video Coding Experts Group (VCEG) and the International Organization for Standardization (ISO) MPEG committee.

#### 2.3 Variable Block Size Motion Estimation (VBSME)

The technique of matching MBs was used in previous video compression standards, such as MPEG-2. However, the new H.264/AVC standard introduces VBSME which employs subblocks smaller than the MB in order to detect finer granularity of motion within a video sequence. For example, Figure 3 shows the same video frame encoded with three different thresholds of subblock granularity.

Figure 3 – Encoding a Singe Frame with Different VBSME settings

In general, larger blocks are well suited for representing large areas of consistent motion and patterns, such as backgrounds. Analysis and experimentation has concluded that a 16 pixel by 16 pixel square MB size is the best compromise between computational complexity and

accuracy [29]. On the other hand, an MB is less likely to be able to precisely describe fine grain objects which could move in several different directions. Reducing the subblock size increases the likelihood of all pixels within that subblock having uniform velocity, and hence the MV being a good fit for the motion of the block. On the other hand, finer granularity comes with an increase in the amount of required computations as well as the total final MV count contained in a single frame, which in turn can increase bandwidth.

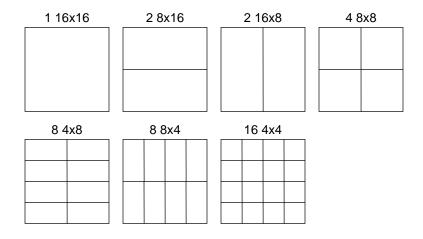

The H.264/AVC standard specifies that the VBSME takes in an MB as input and subdivides the block six times to produce a total of 41 subblocks shown in Figure 4. Motion estimation is then performed on each subblock across multiple reference frames in order to produce 41 integer MVs.

Figure 4 - MB and Subblocks Sizes in VBSME

### 2.4 Search Windows and Multiple Reference Frames

When searching for possible matches for an MB, the integer motion estimation (IME) searches through all of the provided reference frames within a designated search window. A

common search window size is 48 pixels high and 63 pixels across, with a corresponding search range of [-16, +16] vertically and [-24, +23] horizontally, centered on the position of the original current MB.

Further, since the H.264/AVC specification allows for the encoder to search within multiple reference frames (MRF), the MB is compared against one search window within each frame. Commonly, industry applications support the use of at least 4 reference frames, but the specification for allows up to 16. As such, the real-time design requirement used in this thesis is 4 reference frames for each target video resolution. The advantage of MRF is that it equips the encoder with the ability to potentially detect periodic motion. Optimal MB matches can be located within frames that are further away, prior to the immediately previous frame, where periodic motion occurs. This technique can increase the number of acceptable matches for a current MB, which in turn improves the compression ratio, as well as the video quality [30]. However, this advantage significantly increases the amount of computations required by the encoder.

#### 2.5 The Fractional Motion Estimation Algorithm

The input to FME consists of a set of motion vectors from the integer VBSME algorithm [31].

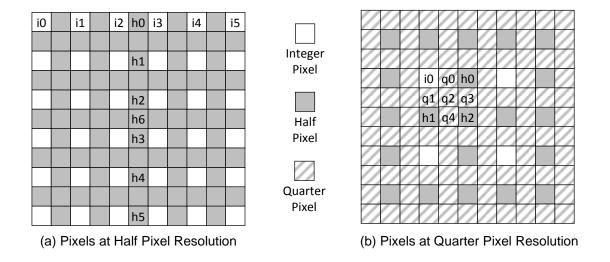

Figure 5 - Half and Quarter Pixels

FME is used to refine the integer MVs at two finer granularities: at half pixel resolution and quarter pixel resolution. In particular, half pixels are created for reference frames based on Equation 2, where each pixel is defined as the weighted average of a row of six neighboring integer pixels or a column of six neighboring half pixels, as shown in Figure 5 - (a). Quarter pixels, on the other hand, are defined by Equation 3, where each quarter pixel is calculated as the average of two of its neighboring integer/half pixels as shown in Figure 5 - (b).

$$h_0 = \frac{\left(i_0 - 5 \times i_1 + 20 \times i_2 + 20 \times i_3 - 5 \times i_4 + i_5\right)}{32}$$

$$h_6 = \frac{\left(h_0 - 5 \times h_1 + 20 \times h_2 + 20 \times h_3 - 5 \times h_4 + h_5\right)}{32}$$

Equation 2 - Half Pixel Generation

$$q_0 = \frac{(i_0 + h_0 + 1)}{2}; \quad q_1 = \frac{(i_0 + h_1 + 1)}{2}$$

$$q_2 = \frac{(h_0 + h_1 + 1)}{2}; \quad q_3 = \frac{(h_0 + h_2 + 1)}{2}$$

Equation 3 – Quarter Pixel Generation

Half and quarter pixels are used to refine the integer motion vectors in two stages. First FME compares each integer motion vector to eight of its surrounding motion vectors at half pixel resolution. Here, the Sum of Absolute Transformed Differences (SATDs) is used as a metric which evaluates the suitability of the subblock. Equation 4 defines the SATD value for a 4x4 subblock. In the equation, Hadamard represents the 2-D Hadamard transform [24], C(i, j) represents the value of pixel (i, j) in the 4x4 block, x and y represent the horizontal and vertical displacement (due to the integer motion vector) of the pixel coordinates in the reference frame with respect to the pixel coordinates in the 4x4 block, R(rx + x + i, ry + y + j) represents the value of the corresponding pixel (rx + x + i, ry + y + j) in the reference frame, and rx and ry (as defined in Equation 6) represent the range of motion estimation at half pixel resolution.

The best motion vector at half pixel resolution is further refined at quarter pixel resolution based on Equation 3. Here x and y represent the displacement of the reference pixels with respect to pixels in the 4x4 block at half-pixel resolution, rx and ry (as defined in Equation 6) represent the search range at quarter pixel resolution, and the SATDs of the larger blocks are similarly defined as the sum of all SATDs of their constituting 4x4 blocks.

$$rx' = rx + x$$

;  $ry' = ry + y$

$$R_{M} = \begin{pmatrix} R(rx'+0,ry'+0) & R(rx'+1,ry'+0) & R(rx'+2,ry'+0) & R(rx'+3,ry'+0) \\ R(rx'+0,ry'+1) & R(rx'+1,ry'+1) & R(rx'+2,ry'+1) & R(rx'+3,ry'+1) \\ R(rx'+0,ry'+2) & R(rx'+1,ry'+2) & R(rx'+2,ry'+2) & R(rx'+3,ry'+2) \\ R(rx'+0,ry'+3) & R(rx'+1,ry'+3) & R(rx'+2,ry'+2) & R(rx'+3,ry'+3) \end{pmatrix}$$

$$C_{M} = \begin{pmatrix} C(0,0) & C(1,0) & C(2,0) & C(3,0) \\ C(0,1) & C(1,1) & C(2,1) & C(3,1) \\ C(0,2) & C(1,2) & C(2,2) & C(3,2) \\ C(0,3) & C(1,3) & C(2,3) & C(3,3) \end{pmatrix}$$

$$M = Hadamard(R_{M} - C_{M})$$

$$SATD = \sum_{i=0}^{3} \sum_{j=0}^{3} |M(i, j)|$$

Equation 4 – Generating the SATD Value

$$rx \in [-0.5 \quad 0 \quad 0.5] \quad ry \in [-0.5 \quad 0 \quad 0.5]$$

Equation 5 - Half Pixel Range

$$rx \in [-0.25 \quad 0 \quad 0.25] \quad ry \in [-0.25 \quad 0 \quad 0.25]$$

Equation 6 – Half and Quarter Pixel Range

#### 2.6 The FME Architecture

The FME engine takes in as input a series of sets of 41 MVs, previously processed by an integer VBSME engine, shown in Figure 6. The 41 MVs point to the seven types of variable

sized subblocks previously shown in Figure 4. The blocks are sent to the FME engine and processed in various sized pixel array chunks per clock cycle, depending on the instantiated size of the scalable FME.

Figure 6 - Motion Estimation Block

#### 2.7 Hardware Implementation

The following section describes two specific hardware implementation techniques used in this work.

#### 2.7.1 Finite Impulse Response Filter

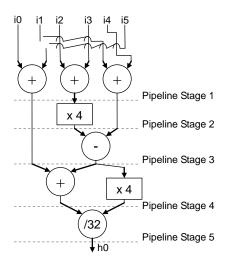

The FIR filter is the basic building block of the FME engine and is used to generate half-pixels based on a weighted sum of its neighboring six integer pixels. In this section we describe its hardware implementation. The original FIR filter weighted sum is shown in Equation 2. For the purpose of a hardware implementation, the filter was optimized by pipelining and sharing resources [3]. The logic is grouped so that the greatest common factors of each weight value are processed together. In addition, the logic is setup so that the multiplier values are a power of two and can be implemented as simple shift registers. Figure 7 shows the five stage pipelined data flow, defined by Equation 7 which is mathematically equivalent to Equation 2.

$$h_0 = \{ [(i_0 + i_5) + (i_2 + i_3) \times 4 - (i_1 + i_4)] + [(i_2 + i_3) \times 4 - (i_1 + i_4)] \times 4 \} \div 32$$

Equation 7 - FIR Filter

Figure 7 - Pipelined Hardware Implementation of the FIR Filter

#### 2.7.2 The 2-D Hadamard Transform

The 2-D Hadamard transform yields a convenient and fast hardware implementation because all of its coefficients are either 1 or -1. The pixel bit vectors are transformed into a 2's compliment format. When multiplying by 1, the original pixel bit vector is preserved, and when multiplying by -1 the bit vector's most significant bit is inverted.

The original equation for the 1-D Hadamard transform is shown in Equation 8, where *a*, *b*, *c* and *d* are the four input pixels, and *had\_out\_m\_0*, *had\_out\_m\_1*, *had\_out\_m\_2*, and *had\_out\_m\_3*, are the four output pixels. The alike terms are grouped together in order to avoid redundant calculations resulting in Equation 9 which is mathematically equivalent to Equation 8. The hardware implementation is shown in Figure 8. The intermediate pipeline Stage 1 of adders ensures sharing of the like terms for the second stage of adders [24]. This way, only eight adders are required instead of 12 if the adder structure was designed corresponding to the original Equation 8.

had \_out \_

$$m_0 = a + b + c + d$$

had \_out \_ $m_1 = a - b + c - d$

had \_out \_ $m_2 = a + b - c - d$

had \_out \_ $m_3 = a - b - c + d$

Equation 8 – 1-D Hadamard Transform

had

$$_out _m_0 = (a+b)+(c+d)$$

had  $_out _m_1 = (a-b)+(c-d)$

had  $_out _m_2 = (a+b)-(c+d)$

had  $_out _m_3 = (a-b)-(c-d)$

Equation 9 – Hardware Optimized 1-D Hadamard Transform

Figure 8 - The Hardware Implementation of the Optimized 1-D Hadamard Transform

#### 2.8 Motivation

The motivation behind our work is rooted in the complexity requirements of video processing. This complexity appears on many fronts, such as large memory storage occupancy, high transmission bandwidth requirements, the number of GIPS for encoding and large amounts of needed hardware resources. Below we provide sample numbers and requirements for each of these, some corresponding to the entire H.264/AVC standard, and some for FME in particular. Next, we formulate a complexity expression with regards to the processing requirements. Our calculation is expressed in terms of *pixel comparisons*, which translates to multiple instructions, the number of which depends on the way the algorithm is coded as well as the targeted device. We also briefly explain the difference between full-search and fast-search FME algorithms. Finally, we present a brief introduction into the concept of our new FME scaling approach.

Raw digital video in its uncompressed form requires a considerable amount of storage space and transmission bandwidth. For example, uncompressed HD video requires 3.12 MB to store data belonging to a single frame. Capturing a video stream at a real-time rate of 30 fps requires 93.6 MB of storage for every second of video. This is a relatively large amount. In comparison, a Blu-ray disk with 100 Giga Bytes of storage capacity would be able to hold only 18 minutes of uncompressed HD video. Similarly, compression plays a large role in today's networked environments where limited bandwidths are present. The H.264/AVC codec can achieve a 64% bit-rate reduction [1]. To process a large amount of data in real-time video encoders are required to operate at the rate that digital video streams are captured. The processing requirement will intensify as high definition resolutions and frame rates increase in the future. This trend creates a requirement for continuously evolving processing hardware as

well as scalable solutions.

The computational requirement of the entire H.264/AVC codec, which FME is part of,

has also been examined. In particular, experimental results using the Joint Video Team Reference

Software (JM7.3) [32], have shown the video encoding algorithm to consume over 80 GIPS,

with a baseline profile Level 2 with CIF<sup>1</sup> format, 5 reference frames and +/- 16SR<sup>2</sup> [3]. The FME

has been measured to occupy 45% of the run-time in inter prediction [3]. Similarly, the

computational complexity for the SDTV<sup>3</sup> and HDTV720p<sup>4</sup> standards, with 4 reference frames

was measured by *iprof* software [33] (an instruction level software analyzer) to be 2470 and 3600

GIPS respectively [1], which is beyond the capability of general purpose processors, making

dedicated hardware a necessity.

The FME occupies a large part of the overall H.264/AVC engine. One hardware

implementation of the codec shows the FME consisting of over 400,000 gates, which amounts to

43% of the total chip resources used [1].

Next we explain the difference between full-search and fast-search FME algorithms, which

is necessary to understand our formulation of the computational complexity. Hardware

implementations of the FME algorithm can be classified into two types: fast search [34]-[43] and

full search [1][3][10]-[16] algorithms. Fast search approaches can potentially reduce the

computational complexity through algorithmic optimizations, at certain costs to video quality.

These shortcuts result in irregular memory accesses because the optimizations are designed to be

content dependent. This means that different video streams will result in a range of total

processing times and complexities. As a result fast search is less computationally traceable,

<sup>1</sup> CIF resolution:352x288 in PAL

<sup>2</sup> SR – Search Range

<sup>3</sup> SDTV resolution: 856x480

<sup>4</sup> HDTV720p resolution: 1780x956

23

meaning that it is difficult to measure the exact efficiency of specific computational blocks because they will differ over various content. Full search algorithms eliminate the unpredictable data flow by fully exploring the motion estimation search space to produce higher compression ratios and video quality than fast search algorithms. The focus of this investigation is based on full search whose computational complexity is not dependent on the video content as it is fitting with our goal to quantify performance and identify the algorithmic scalability potential.

The following is our complexity analysis of the full-search half-pixel VBS-FME algorithm. We can define the running time, T, of the FME algorithm by calculating the number of operations that need to be performed per second, where each operation is considered to be a pixel comparison between two corresponding pixel locations in the reference and current subblock. The running time can be expresses in the following form:

$$T = P_{MB} \times i \times r_{xy} \times R_{frame} \times MB_{frame} \times fps$$

Equation 10 - The Running Time of FME

$$MB_{frame} = \frac{width_{frame}}{16} \times \frac{height_{frame}}{16}$$

Equation 11 – Total Number of Macroblocks per Video Frame

Where the complexity scales linearly with each of the following variables:

$P_{MB}$  – number of pixels in a single MB

*i* – seven various subblock sizes

$r_{xy}$  – nine half pixel candidate positions

$R_{frame}$  – number of reference frames; range [1, 16]

*fps* – frames per second

MB<sub>frame</sub> – total number of MBs in a single video frame

*width*<sub>frame</sub> – width of a video frame

*height<sub>frame</sub>* – height of a video frame

The full-search half-pixel VBS-FME algorithm has the following fixed values:  $P_{MB} = 256$ , i = 7,  $r_{xy} = 9$ . The remaining variables can be set within the encoder to suit the video stream to be processed as well as the desired compression ratio. A sample setting where  $R_{frame} = 4$ , (width<sub>frame</sub> x height<sub>frame</sub>) = 1920x1080 (HDTV) and fps = 30 yields a total of approximately 15.7 x 10<sup>9</sup> pixel comparisons per second.

Having expressed the intense computational complexity trend, it follows to set out to create algorithms with higher processing bandwidth, yet with efficient design implementation. Next we describe our approach at scaling the FME algorithms.

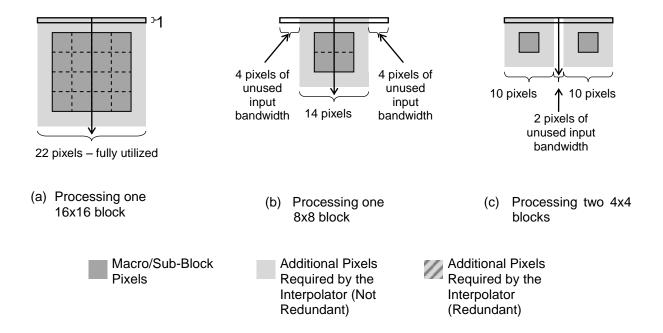

The size of macro/sub-blocks can range from 4x4 to 16x16 pixels, FME hardware must carefully balance parallelism with hardware utilization. In particular, previous work [1][3][10]-[16] has implemented designs that can simultaneously process 4, 8 or 16 pixels from a single row of a macro/subblock at a time. In this work we found that expanding parallelism only along the row, however, can quickly degrade utilization as the number of simultaneously processed pixels is increased. Since under-utilized hardware reduces overall efficiency, it is important to create designs that can increase parallelism while maintaining a high degree of hardware utilization.

We observe that the parallelism of FME not only can be increased horizontally across a row of pixels but also vertically along a column of pixels. Designs that increase parallelism in the vertical direction can potentially provide higher performances while maintaining high hardware utilization. In this work, we develop a scalable FME algorithm and compare the effect of horizontal with vertical scaling.

Table 1 - The FME Scaled Designs

| Type of Scaling | Scaled FME Designs | Source of Design |  |

|-----------------|--------------------|------------------|--|

| Vertical        | M=10, N=1          | Our work         |  |

|                 | M=4, N=1           | Our work         |  |

|                 | M=2, N=1           | Our work         |  |

| Base Design     | M=1, N=1           | [13]             |  |

| Horizontal      | M=1, N=2           | [15]             |  |

|                 | M=1, N=4           | [16]             |  |

Table 1 lists six scaled FME designs addressed in this work. The base and horizontal design were previously implemented by [15] and [16] respectively. The three vertically scaled designs have been developed in this research. The new designs are primarily based on the base design, which was enhanced to form a scalable version. The vertically scaled designs were enhanced to perform vertical data processing.

## 2.9 Chapter Summary

In this chapter we presented the basics of video and video compression algorithms. In particular we covered the mathematical calculation necessary for the FME algorithm which is referenced in the later chapters where we introduce our hardware architecture design. The basics of FME calculations are strongly correlated with design decisions we faced when scaling the encoder. In addition we described a few techniques used during the hardware implementation as well as the non-scaled FME architecture. Finally, we conclude the chapter with the motivation behind our work which is rooted in the complexities of video encoding.

## **Chapter 3 - The Scalable FME Architecture**

This chapter describes the scalable FME architecture core. The description is presented in a top down approach, starting with the overall data flow of the FME algorithm. We introduce the architectural components of the FME core followed by how each of them is scaled in the design.

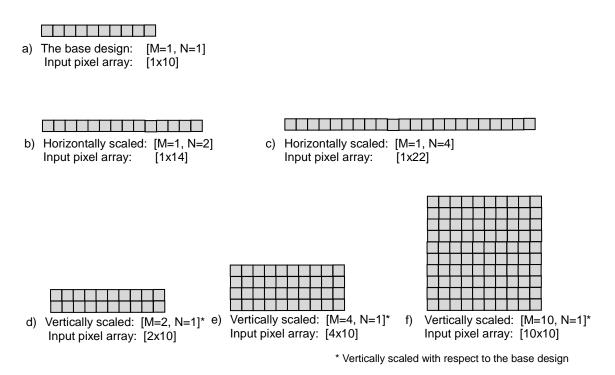

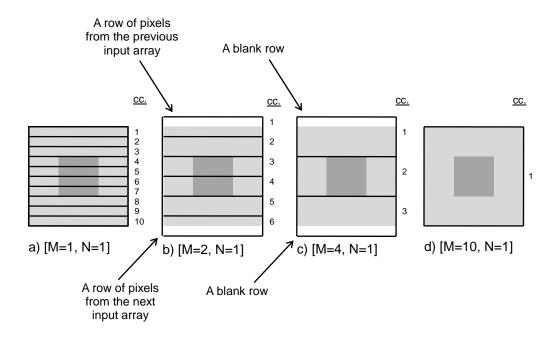

In this work, we employ a scalable full-search FME engine on an FPGA in order to investigate the tradeoffs between used hardware resources and measured performance. We create several versions of the FME architecture by introducing two scalable factors, M and N. By varying these scalable factors we in turn vary the number of pixels simultaneously processed by the engine per clock cycle, which translates to the amount of instantiated processing hardware.

M and N correspond to the height and width of the input pixel array taken in by the FME engine every clock cycle. Figure 9 shows the six various sizes of the input pixel array corresponding to the six scaled FME designs. The array sizes correspond to M x (4N+6) pixels. These variables determine the total number of pixels that are simultaneously processed by the system. This in turn determines the amount of resources instantiated for the hardware engine, trading area and hardware utilization for parallelism and performance. By simultaneously processing larger pixel arrays, we increase parallelization and reduce the total processing time of the 41 motion vectors. For example, the horizontally scaled design in Figure 9 - (c) or the vertically scaled design in (f) will process an 8x8 block in less clock cycles compared to the base design in Figure 9 - (a).

The base design was previously implemented by [13]. The two horizontally scaled

designs, [M=1, N=2] and [M=1, N=4] were implemented by [15] and [16] respectively. Instead of arbitrary increasing the width of the FME engine, the dimensions were chosen so that they correspond to the width of various subblocks. The width of the FME input array is incremented by 4 pixels at a time. This results in a corresponding block width of 4N pixels, which can be effectively mapped to N 4-pixel wide Hadamard transforms shown in Equation 4. An SATD value is defined over a 4-pixel wide subblock, which is the smallest common subblock size. For this reason, processing less than 4-pixels wide chunks in hardware would be inefficient. In our scalable design, when taking into account the surrounding pixels required for the 6-tap filter, the total width of the input array is expressed as 4N+6. Overall, the dimensions of each scalable input pixel array can be expressed  $M \times (4N+6)$ .

Figure 9 - The Input Array Sizes for 6 Scaled FME Designs

The three vertically scaled designs (d), (e) and (f) in Figure 9 were developed in this work. The vertically scaled designs increase parallelism by processing multiple rows at the same time. The design in (d) is capable of handling 20 pixels per clock cycle, whereas the design in (e) can handle 40. The design in (f) takes in 100 pixels per clock cycle, corresponding to the size 4x4 subblock including all of its surrounding pixels.

The naming convention for our scaling is derived with respect to the base design. When compared this way, we observe that the designs in (d), (e) and (f) are just as wide as the base design (a), therefore we consider them to be vertically scaled. Similarly, the designs in (b) and (c) are the same height as the base design but wider, therefore we consider them to be horizontally scaled.

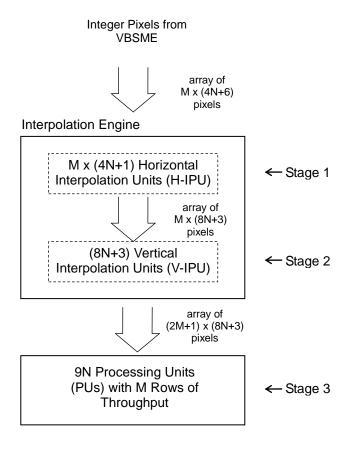

The overall structure of the scalable FME architecture is shown in Figure 10. The FME contains two main components: *the Interpolation Engine* (IE) and *SATD Processing Units* (PUs). The IE is further divided into the horizontal (H-IPU) and vertical interpolation units (V-IPU), which generate half pixels. After interpolation, the PUs calculate SATD values for the nine candidate vector half pixel refinement positions.

Figure 10 - The Scalable FME Architecture

The base design was extended in order to integrate scalability across two different axes. In particular, we modified the IE in order to vary it in width and height corresponding to the scalable variables. To achieve this we extended the connectivity of its components, such as the H-IPUs and V-IPUs. Further, we enhanced the V-IPUs in order to enable them to be used in vertically scaled designs and process multiple rows of pixels per clock cycle. Similarly, in order to match the vertically increased data throughput, we extended the PU design by adding resources and altering the operation of its internal structure.

Finally, the described design was written in VHDL with an *auto-tuning* feature, which enables the user to set the M and N scalable factors at compile time and then instantiates the resources for the corresponding FME engine, based on the designs shown in Figure 10.

#### 3.1 Interpolation Engine

The IE takes integer pixels as input and generates interpolated half pixels as output. The basic building block of the IE is the six-tap Finite Impulse Response (FIR) filter. Multiple FIR filters are aggregated to compose Vertical (V-IPU) and Horizontal Interpolation Units (H-IPU) described next.

### 3.1.1 Horizontal Interpolation Unit

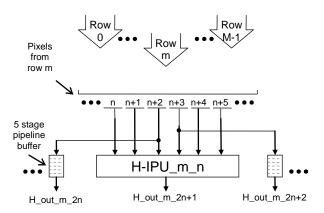

Structurally, our H-IPU design is based on the non-scaled design in [13]. Here each H-IPU contains a single FIR filter whose connectivity is shown in Figure 11. As previously described, each FIR filter takes in a row of six adjacent integer pixels as its input and produces one half pixel as its output. The generated half pixel is positioned between the third and fourth input pixel. The output pixel array from Stage 1 is passed onto Stage 2 for further half pixel generation. The entire pixel array output of Stage 1 consists of an array of M x (8N+3) pixels as shown in Figure 10. In order to align the generated half and original integer pixels in the Stage 1 output array, buffers are placed alongside each H-IPU. Each buffer receives integer pixels and delays them by five clock cycles, equivalent to the number of processing cycles required by the

FIR filters. This way the integer pixels and the half pixels experience the same logic delay and the row-alignment is preserved for Stage 2 processing.

In our design the number of H-IPUs in Stage 1 scales with M and N. Instead of being positioned in a single row, as in the base design, the vertically scalable H-IPU units are arranged in a 2D grid of size M x (4N+1). This allows the 2D grid to process M rows of pixels per clock cycle. In the input integer pixel array, each of the M rows of pixels is mapped onto its own row of H-IPUs for parallel processing. Further, within each row, the 4N+6 integer pixels are mapped onto 4N+1 H-IPUs.

Figure 11 - The H-IPU Connectivity at Row m and Column n

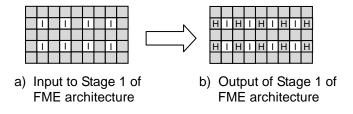

The scalable 2D grid of H-IPUs makes up Stage 1 of the FME architecture. The H-IPUs are used to generate multiple variable length rows of half pixels as is shown in Figure 12. The remaining empty rows are generated by V-IPUs in Stage 2.

Figure 12 – Pixel Interpolation in Stage 1

#### 3.1.2 Vertical Interpolation Unit

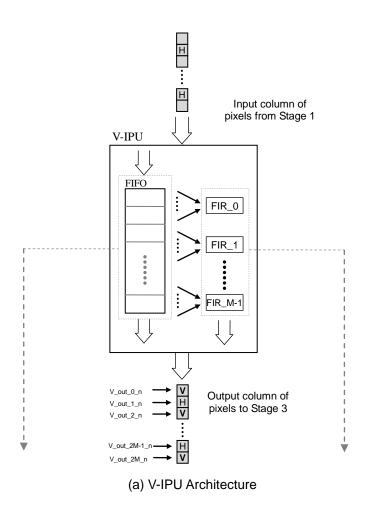

Our scalable V-IPU unit is based on the non-scaled V-IPU from the base design implemented in [13], which contains a single pixel wide FIFO and six FIR filters. Here the V-IPU receives a single pixel into an 8-bit wide FIFO, while the six FIRs calculate a single half pixel per clock cycle. The output pixel column is composed of three pixels, an integer pixel surrounded by two half pixels. One of the half pixels is the newly generated half pixel by the FIR filter, and the other is a buffered half-pixel from the previous clock cycle. This way every output column begins and ends with a half pixel which is required for mapping onto the Stage 3 PUs.

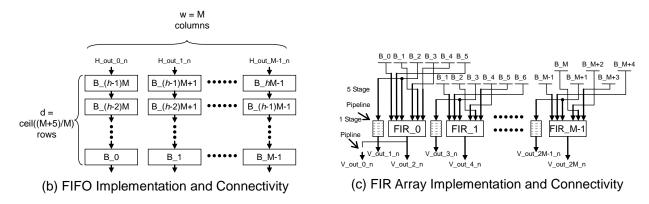

Our scalable V-IPU has enhancements which allow it to process multiple rows of pixels per clock cycle and is shown in Figure 13. First, it contains a variable width and depth FIFO, which can take in multiple pixels per clock cycle. Second, there are M FIR filters which simultaneously generate M half pixels. Finally we connect 8N+3 V-IPUs in a row, which make up Stage 2 of the FME architecture. Here the variable N allows for horizontal scaling while M varies the resources inside the V-IPU allowing for vertical scaling.

The scalable FIFO design is shown in Figure 13 - (b). Its size is determined by the number of input pixels to the V-IPU per clock cycle. In particular, the M filters need to access a total of M+5 pixels while a V-IPU receives only M input pixels per clock cycle. Consequently, the FIFO needs to buffer five pixels from the previous cycles – resulting in a total FIFO size of  $ceil((M+5)/M) \times M$  pixels, shown in Figure 13 - (b). The width of the FIFO, w, is set to M, the number of input pixels per clock cycle. The depth, d, is set as the minimal height needed in order for the FIFO to hold ceil((M+5)/M) pixels at width w.

Figure 13 - The *n*th Scalable V-IPU

Each clock cycle, M new pixels are received by the FIFO, the rest of the pixels shift down, and the bottom pixels are sent out and become part of the V-IPU output column. The FIRs grab the necessary data from the FIFO and produce one half pixel each. The mapping of the pixels between the FIFO and the FIRs is shown in Figure 13 - (c). The first filter, FIR\_0, takes in the top six pixels from the FIFO, and each subsequent FIR has an input pixel array which is shifted down by one pixel.

The V-IPU in the [M=10, N=1] FME design is an exception to the previously described scalable approach for the following reason. In this case the design takes in a 4x4 block of elementary pixels centered inside a 10x10 subblock of surrounding pixels. The V-IPU generates half pixels only around the elementary pixels, hence creating a total of only five half pixels. Therefore, each V-IPU can be reduced by using only five FIR filters, thus saving hardware resources while increasing data throughput. Similarly, for each clock cycle, within the FIFO the entire 10 pixels are flushed and replaced by 10 new ones; therefore the FIFO is reduced to a simple register, 10 pixels in size.

Figure 14 - V-IPU for the [M=10, N=1] Design

The V-IPUs are used to generate the remaining half pixels which are located in between the rows of integer pixels, shown in Figure 15. The newly generated half pixels and the FIFO output pixels make up an output column produced by a single V-IPU. The aggregated columns of all the V-IPUs make up the output from Stage 2 which is the M x (8N +3) pixel array. Finally, the output pixel array from Stage 2 is forwarded to Stage 3, to the 9N Processing Units (PUs) for SATD calculations.

Figure 15 – Pixel Interpolation in Stage 2

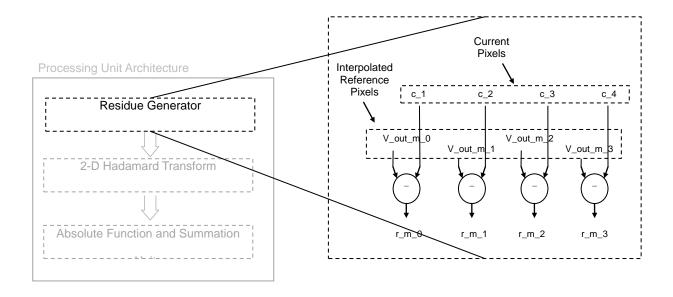

### 3.2 SATD Processing Unit

Each PU has two input streams: the 4x4 subblocks from the *current* frame and the 4x4 subblocks from the *reference* frame. The current frame is the one to be encoded and the reference frames are the potential matches for the subblock from the current frame. The PUs function is to generate SATD values. The SATD represents how good of a match the reference 4x4 pixel subblock is to the current 4x4 subblock.

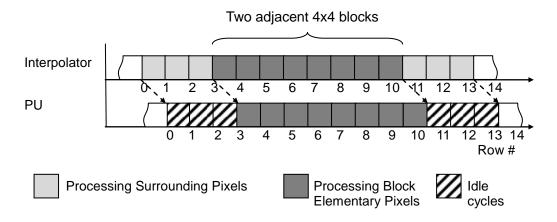

Our PU design is based on the non-scalable design previously implemented in [13], where a single set of 9 PUs processes one row of four pixels per clock cycle. Our scalable version also encompasses the horizontally scaled PU design implemented in [15] and [16]. Here,

2 and 4 sets of PUs were placed adjacently in order to process 8 or 16 elementary pixels at once. We denoted the horizontal scaling using the N scalable variable which instantiates N adjacent sets of 9 PUs. Next we enhanced the PU with additional resources which allow it to process multiple rows of pixels per clock cycle and as a result to be vertically scalable.

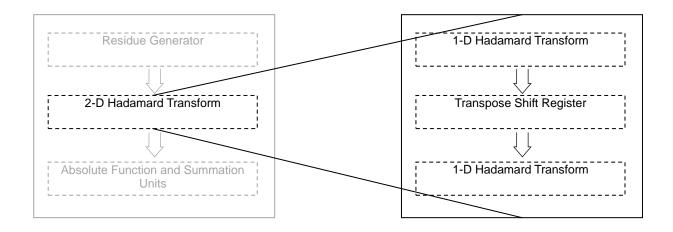

The resulting scalable PU architecture is shown in Figure 16. The PU is composed of three processing blocks: Residue Generators, a 2-D Hadamard Transform and an Absolute Function with Summation Units. The architecture of each of the parts is described in the next sections.

Figure 16 - The Processing Unit Architecture

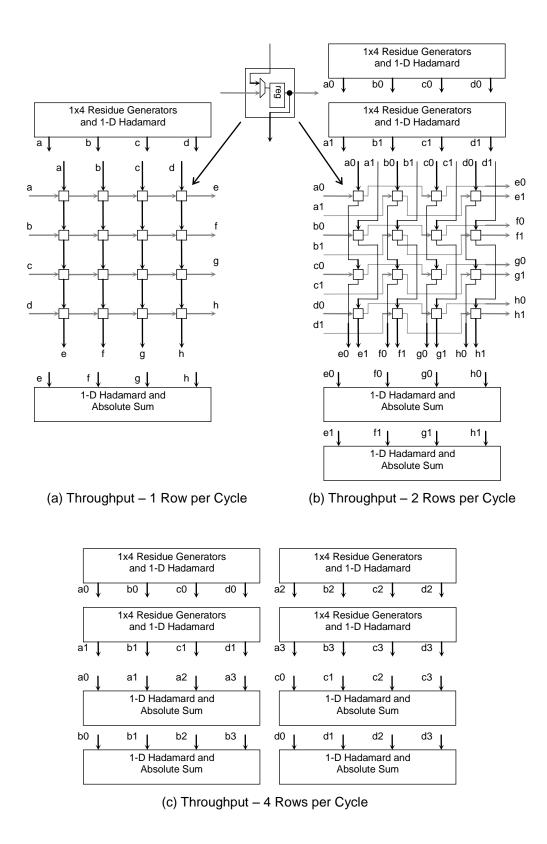

### 3.2.1 Vertical Scaling of the PU

Vertical scaling requires an increase in the PUs throughput. To allow for this the PUs are enriched with additional hardware in order to process the additional rows. In particular, for every additional row, each PU requires an extra set of residue generators, two extra 1-D Hadamard transform units, and one absolute value and summation unit. For example, a PU design with a throughput of two rows per clock cycle is shown in Figure 17 - (b). This PU corresponds to the [M=2, N=1] design and it calculates one SATD every two clock cycles. The PU design with a throughput of four rows per clock cycle is shown in Figure 17 - (c), corresponding to [M=4, N=1] and [M=10, N=1] designs, capable of producing an SATD value every clock cycle.

Figure 17 - The Vertically Scaled PU Designs with Various Data Throughput Rates

### 3.2.2 Residue Generators

When we scale vertically we instantiate M sets of Residue Generators in parallel. Each set of residue generators processes a rows four pixels. Two sets of four pixels are inserted into the residue generator every clock cycle, as shown in Figure 18. One row of four pixels comes from the 4x4 subblock from the current frame, and the other from the 4x4 subblock from the reference frame. The residue generator is composed of four units, each calculating the difference between the corresponding current and reference frame pixels from the input rows. The output of the residue generators is passed onto the 2-D Hadamard transform unit.

Figure 18 - The Residue Generator

#### 3.2.3 The 2-D Hadamard Transform

The 2-D Hadamard transform is implemented in three parts: a single transpose shift register placed between two sets of 1-D Hadamard transform units, as shown in Figure 19. Each row of four residue pixels is sequentially processed by the three parts of the 2-D Hadamard Transform, and the output is passed onto the Absolute Function and Summation Units.

Figure 19 - 2-D Hadamard Transform

## The Transpose Shift Register

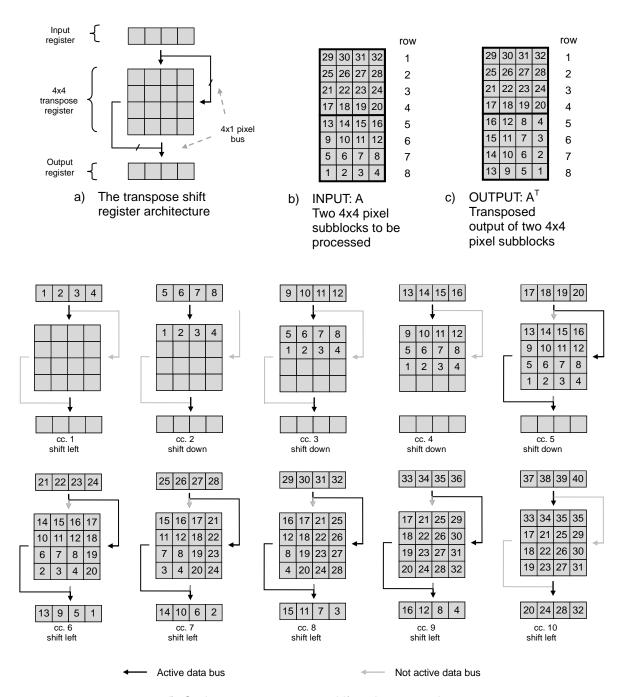

The transpose shift register takes in a 4x4 pixel subblock and outputs its transpose which is then passed onto the second 1-D Hadamard Transform. Two sample input 4x4 subblocks, A, are shown in Figure 20 - (b), and the outputted transpose, A<sup>T</sup>, is shown in Figure 20 - (c).

d) Cycle accurate transpose shift register operation

Figure 20 - Operation of the Transpose Shift Register for the [M=1, N=1] PU

Figure 20 - (c) shows a cycle by cycle sample data flow operation of the transpose shift register. The operation depicted is for a PU from the [M=1, N=1] design, which produces one SATD value every four clock cycles, and shifts a single row/column at a time.

The transpose shift register toggles between a *shift-down* and a *shift-left* mode every time an entire 4x4 subblock has been written into the register. In the shift-down mode, pixels from the 4x4 subblock are written into the register horizontally, as is depicted in Figure 20 - (d), in cc.1 to cc.5. In general, the register shifts in M rows per clock cycle, while the 4x4 block originally stored in the transpose shift unit is read out horizontally M rows per clock cycle. This continues until the entire 4x4 block originally stored in the transpose register unit is completely replaced by the new 4x4 block. At that time the transpose shift register switches to the shift-left mode. Now the next 4x4 block is written into the unit vertically 1 column per clock cycle, as is depicted in Figure 20 - (d), in cc. 6 to 10. In general, the register takes in M columns per clock cycle, while at the same time the stored 4x4 block is read out vertically M columns at a time.

The frequency of the switch between shift-down and shift-right modes is determined upon the throughput, M. The transpose register switches every 4 and 2 clock cycles for the [M=1, N=1] and [M=2, N=1] designs correspondingly. The [M=4, N=1] and [M=10, N=1] design process an entire 4x4 pixel array in a single clock cycle, therefore not requiring a transpose shift register and shift-down/left modes. Instead the 16 pixels are directly mapped between the 1-D Hadamard Transforms and the absolute function and summation units.

As we scale the FME architecture to increase data throughput and so the timing of the switch between the shift modes must be preserved with respect to the transition between adjacent 4x4 subblocks. The effects of this on the scaled designs of FME are discussed in terms of vertical data alignment in Chapter 4.3.3.

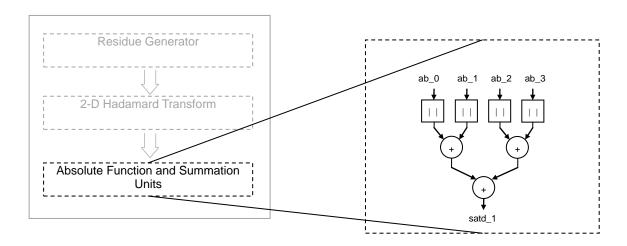

### 3.2.4 Absolute Function and Summation

We instantiate M sets of absolute function and summation units in parallel. After the Hadamard transform, the four output pixels pass though the absolute function units, followed by summation logic. The resulting output value is representative of a single row of four pixels. Four of these output values are accumulated and summed to produce the final SATD for a single 4x4 subblock. Similarly, to calculate the SATD value of a larger subblock, the SATD values of its composing 4x4 subblock are accumulated and summed.

Figure 21 - The Absolute Function and Summation Units

#### 3.2.5 Horizontal Scaling of the PU

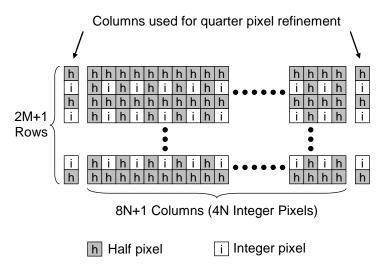

The number of PUs required to simultaneously calculate all of the SATDs for an array of pixels is determined by the width of the Stage 3 input pixel array which is of (2M+1) x (8N+3) size. Rows of (2M+1) x (8N+1) pixels are forwarded to PUs in Stage 3 while the remaining left most and right most two columns can be stored for later use in the quarter pixel calculations, as shown in Figure 22. At half pixel resolution, each row of this array contains (8N+3) integer pixels, out of which 4N are elementary integer subblock pixels belonging to N 4x4 subblocks. Each SATD is defined over an array of 4x4 pixels was shown in Equation 4. To maximize parallelism a set of 9 PUs is used to handle the calculation of nine candidate refinement positions (shown in Figure 23) and their SATD values for one 4x4 block. When scaling horizontally, we simply instantiate N sets of 9 PUs, which are capable of processing multiple 4x4 subblocks side by side. The pixels for each 4x4 subblock are mapped onto a single set of nine PUs, and the nine candidate positions are calculated by the set.

Figure 22 - Pixel Layout at the Output of Stage 2 (V-IPUs)

Figure 23 - Nine Half Pixel Candidate Positions and Their Offset Vectors for One Integer Pixel

In Figure 24, we show how a single 4x4 subblock with its interpolated half pixels is mapped onto a single set of nine PUs. Every one of the nine PUs receives an array of 4x4 pixels, shown in black. The middle PU, #5, receives the original integer pixels. The surrounding eight PUs receive the shifted and interpolated version of the 4x4 original subblock set. The offset vectors for the 4x4 block and the nine PUs correspond to the offset vectors for the single integer pixel and its eight surrounding half pixel candidate positions, shown in Figure 23. Depending on the vertical design in question, M rows of four pixels are forwarded to the array per clock cycle.

Figure 24 - Mapping a 4x4 Subblock to a Single Set of 9 PUs

### 3.3 Chapter Summary

In this chapter we have presented our scalable FME architecture and its two main components: the IE and the PU. We introduced the basic building block of the IE which is the FIR filter, and how it is implemented in order to create H-IPUs and V-IPUs. We showed how the PU is implemented by decomposition into three main parts: Residue Generators, 2-D Hadamard Transform, Absolute Function and Summation Units. We further explored the data flow between the IE and PU and the way the pixels map onto sets of 9 PU. We build upon the architecture details presented in this chapter in order to develop further concepts, such as data alignment with respect to vertical scaling. In particular we show how vertical alignment is influenced by the number of clock cycles it takes for the PU's 2-D Hadamard Transform to process a set of 4x4 pixels.

# **Chapter 4 - Design Space Exploration**

The analysis techniques described in this chapter, along with the comparisons of the FME engines and their pixel processing schedules, set the stage for the next chapter which analyzes the overall scalability of each design. We describe factors used to compare the tradeoffs between the six scaled FME designs. First, we introduce the concept of *block decomposition*, which leads into a discussion of *data redundancy*. Next, we define three factors which influence *hardware utilization*: input data variance, throughput variance and vertical alignment, and derive equations for estimating the overall hardware resource usage. Finally, we calculate and the total number of clock cycles it takes each engine to process a set of 41 subblocks.

### 4.1 Block Decomposition

Block decomposition is a method of breaking up the macro/sub-blocks into smaller block sizes. If the processing hardware is narrower than the subblock width, the subblock must be decomposed into smaller chunks and the chunks processed sequentially. The next two sections describe block decomposition approaches for the vertically and horizontally scaled designs.

### **4.1.1** Block Decomposition for Vertically Scaled Designs

The block decomposition approach depends on the width of the FME unit. Consequently, the base design and two of the vertically scaled designs, [M=2, N=1] and [M=4, N=1], have the same decomposition schedule. The third vertically scaled design, [M=10, N=1], is an exception due to inherent additional design requirements, discussed later in this section.

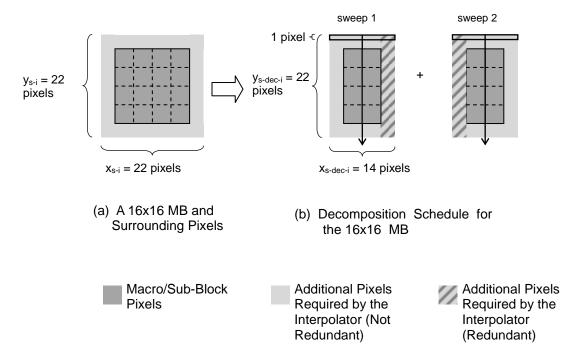

The [M=1, N=1] design is wide enough to process rows of subblocks that are four pixels wide, plus the six surrounding pixels, three on each side. The macro/sub-blocks that are wider than four elementary pixels must be decomposed into a series of 4-pixel wide blocks. For example, Figure 25 shows a decomposition approach for a 16x16 MB. The block is shown with its surrounding pixels, required by the 6-tap FIR filters, resulting in a total of 22x22 a pixel array. When the MB is decomposed, each vertical strip, or sweep, contains some elementary block pixels encircled by surrounding pixels required by the FIR filter. The FIR filter requires six adjacent integer pixels therefore generating half pixels around the edges of the decomposed block requires padding of three extra pixels.

The total pixels in all four sweeps amount to a greater number then in the original 22x22 array, which results in redundant processing described in Section 4.2.

Figure 25 - Decomposition Schedule for a 16 x 16 Block for the [M=1, N=1] Design

In Table 2 we show the decomposition approach for all of the other subblock types, for the same [M=1, N=1] design. The left portion of the table, columns 2 and 3, contains information about the subblocks in their entirety, where  $x_{s-i}$  and  $y_{s-i}$  are subblocks dimensions including their surrounding pixels. The right side of the table, columns 4, 5 and 6, show details of the subblock's decomposition, where  $x_{s-dec-i}$  and  $y_{s-dec-i}$  represent the block's height and width respectively, also including the surrounding pixels. The  $s_i$  term is the number of decomposed smaller blocks, or the number of vertical sweeps performed by the IE.

Note that the  $y_{s\text{-}dec\text{-}i}$  value is the same as the height of the block, which determines the length of each sweep. The  $x_{s\text{-}dec\text{-}i}$  value is the same across all block types because the [M=1, N=1] FME engine is fit for processing rows that are 10 pixels wide. Consequently, block decomposition enables processing of wider subblocks with sequential multiple sweeps. For example, the 16x16 MB requires four sweeps, as shown in Figure 25. On the other hand, the

smallest 4x4 block requires only a single sweep.

Table 2 - The Block Decomposition Schedule for the [M=1, N=1], [M=2, N=1], [M=4, N=1] Designs

| Subblock<br>Type | Before Block<br>Decomposition |           | After Block Decomposition |            | Number<br>of<br>Vertical |

|------------------|-------------------------------|-----------|---------------------------|------------|--------------------------|

|                  | Subblock Dimensions           |           | Subblock Dimensions       |            |                          |

|                  | Width                         | Height    | New Width                 | New Height | Sweeps                   |