Abstract

Real-time Systems often are located in the special environments where the power consumption is a big concern. Upon presence of timing constraints, the low power design on the real-time systems has significant impact on the performance as well as the schedulability of the systems. The system developers are facing the challenges for reducing the power consumption and meeting the timing constraints in the real-time systems.

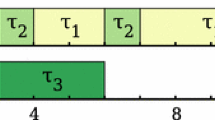

This paper represents one of few attempts to address the issue of the low power design on real-time systems. We present two power reduction methods: one is at the software compilation level and the other at the operating system level. Given a real-time program, an inter-instruction power reduction technique is proposed to transform the program to another one with lower power consumption. In addition, a scheduling algorithm for real-time operating systems is proposed to reschedule real-time programs when the execution time of the programs is changed. Therefore, the proposed scheduling algorithm works together with the proposed power reduction technique to make sure all programs meet their deadlines and to improve the system schedulability. We also evaluate the performance of the proposed inter-instruction reduction method by comparing it with the cold scheduling algorithm and show that the proposed method outperforms the cold scheduling algorithm and reduces more energy power.

Similar content being viewed by others

References

Athas, W. C., Svensson, L., Koller, J. G., Tzartzanis, N., and Chou, E. 1994. Low-power digital systems based on adiabatic-switching principles. IEEE Transactions on VLSI Systems 2(4).

Alidina, M., Monteiro, J., Devadas, S., Ghosh, A., and Papaefthymiou, M. 1994. Precomputation-based sequential logic optimization for low power. IEEE Transactions on VLSI Systems 2(4).

Cong, J., and Koh, C. 1994. Simultaneous driver and wire sizing for performance and power optimization. IEEE Transactions on VLSI Systems 2(4).

Gerber, R., and Hong, S. 1993. Semantics-based compiler transformations for enhanced schedulability. In Proc. of 14 th IEEE Real-Time Systems Symposium, pp. 232–242.

Lee, T. C., Tiwari, V., Malik, S., and Fujita, M. Power analysis and minimization techniques for embedded DSP software. IEEE Transactions on VLSI Systems.

Najm, F. N. 1994. A survey of power estimation techniques in VLSI circuits. IEEE Transactions on VLSI Systems 2(4).

Nielsen, L. S., Niessen, C., Sparso, J., and Berkel, K. 1994. Low-power operation using self-timed circuits and adaptive scaling of the supply voltage. IEEE Transactions on VLSI Systems 2(4).

Saksena, M. C. 1994. Parametric scheduling for hard real-time systems. Dissertation of Ph.D., University of Maryland, College Park, MD.

Saksena, M. C., Silva, J., and Agrawala, A. 1994. Design and implementation of Maruti-II. In Sang Son, Editor, Principles of Real-Time Systems. Prentice Hall. Also available as CS-TR-2845, University of Maryland.

Su, L., Tsui, C. Y., and Despain, A. M. 1994. Low power architecture design and compilation techniques for high-performance processors. In IEEE COMPCON.

Tiwari, V., Malik, S., and Wolfe, A. 1994. Power analysis of embedded software: A first step towards software power minimization. IEEE Transactions on VLSI Systems.

Tiwari, V., Malik, S., Wolfe, A., and Lee, M. T. 1996. Instruction level power analysis and optimization of software. The International Conference on VLSI Design, Banglore, India.

Tiwari, V., and Lee, M. 1997. Power analysis of a 32-bit embedded microcontroller. To appear in the VLSI Design Journal.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Cheng, ST., Chen, CM. & Hwang, JW. Low-Power Design for Real-Time Systems. Real-Time Systems 15, 131–148 (1998). https://doi.org/10.1023/A:1008041928774

Issue Date:

DOI: https://doi.org/10.1023/A:1008041928774