Abstract

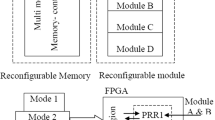

Reconfiguration enables the adaption of Coordinate Rotation DIgital Computer (CORDIC) units to the specific needs of sets of applications, hence creating application specific CORDIC-style implementations. Reconfiguration can be implemented at a high level, taking the entire CORDIC unit as a basic cell (CORDIC-cells) implemented in VLSI, or at a low level such as Field-Programmable Gate Arrays (FPGAs). We suggest a design methodology and analyze area/time results for coarse (VLSI) and fine-grain (FPGA) reconfigurable CORDIC units. For FPGAs we implement CORDIC units in Verilog HDL and our object-oriented design environment, PAM-Blox. For CORDIC-cells, multiple reconfigurable CORDIC modules are synthesized with state-of-the-art CAD tools. At the algorithm level we present a case study combining multiple CORDICs based on a geometrical interpretation of a normalized ladder algorithm for adaptive filtering to reduce latency and area of a fully pipelined CORDIC implementation. Ultimately, the goal is to create automatic tools to map applications directly to reconfigurable high-level arithmetic units such as CORDICs.

Similar content being viewed by others

References

W.H. Mangione-Smith, B. Hutchings, D. Andrews, A. DeHon, C. Ebeling, R. Hartenstein, O. Mencer, J. Morris, K. Palem, V. Prasanna, and H. Spaanenburg, “Seeking Solutions in Configurable Computing,” IEEE Computer Magazine, Dec. 1997.

J.M. Muller, Elementary Functions: Algorithms and Implementation, Birkhauser, 1997.

J.-M. Delosme and S.-F. Hsiao, “CORDIC Algorithms in Four Dimensions, Advanced Signal Processing Algorithms, Architectures and Implementations,” Proc. SPIE 1348, San Diego, CA, July 1990, pp. 349–360.

H.M. Ahmed, “Signal Processing Algorithms and Architectures,” Ph.D. Thesis, E.E. Dept., Stanford, June 1982.

R. Andraka, “A Survey of CORDIC Algorithms for FPGA Based Computers,” Sixth International Symposium on Field Programmable Gate Arrays, Monterey, CA, 1998.

J.E. Volder, “The CORDIC Trigonometric Computing Technique,” IRE Trans. on Electronic Computers, vol. EC-8, no.3, Sept. 1959, pp. 330–334.

J.S. Walther, “A Unified Algorithm for Elementary Functions,” AFIPS Conf, Proc., vol. 38, 1971, pp. 379–385.

T.C. Chen, “Automatic Computation of Exponentials, Logarithms, Ratios and Square Roots,” IBM Journal of Research and Development, July 1972.

J.-M. Delosme, “VLSI Implementation of Rotations in Pseudo-Euclidean Spaces,” Proc. 1983 Int. Conf. on Acoustics, Speech and Signal Processing (ICASSP), Boston, MA, April 1983, pp. 927–930.

D.T.L. Lee and M. Morf, “Generalized CORDIC for Digital Signal Processing,” Proc. 1982 Int. Conf. on Acoustics, Speech and Signal Processing (ICASSP), Paris, France, May 1982, pp. 1748–1751. See also Ph.D. Thesis, E.E. Dept., Stanford, Aug. 1980.

H. Al-Twaijry, “Area and Performance Optimized CMOS Multipliers,” Ph.D. Thesis, Stanford, Aug. 1997.

O. Mencer, M. Morf, and M.J. Flynn, “PAM-Blox: High Performance FPGA Design for Adaptive Computing,” IEEE Symp. on FPGAs for Custom Computing Machines, Napa Valley, CA, 1998. http://umunhum.stanford.edu/PAM-Blox/.

O. Mencer, M. Morf, and M.J. Flynn, “Hardware Software Tri-Design of Encryption for Mobile Communication Units,” IEEE Int. Conf. on Acoustics, Speech and Signal Processing, Seattle, May 1998.

O. Mencer and M. Platzner, “Dynamic Circuit Generation for Boolean Satisfiability in an Object-Oriented Design Environment,” Hawaii Int. Conf. on System Sciences (Config WareTrack), Jan. 1999.

Synopsys FPGA Express, http://www.synopsys.com/products/fpga solution/fpga express.html.

G. De Micheli, Synthesis and Optimization of Digital Circuits, Highstown, NJ: McGraw Hill, 1994.

Synopsys Products, http://www.synopsys.com/products.

J. Turner, Prentice-Hall Signal Processing Series, Ch. 5, 1985.

H.M. Ahmed, P.H. Ang, and M. Morf, “A VLSI Speech Anaysis Chip Set Utilizing Co-ordinate Rotation Arithmetic,” Proc. 1981 Int. Symp. on Circuits and Systems (ISCAS), Chicago, Illinois, April 1981, pp. 737–741.

H.M. Ahmed, P.H. Ang, and M. Morf, “A VLSI Speech Analysis Chip Set Based on Square-Root Normalized Ladder Forms,” Proc. 1981 Int. Conf. on Acoustics, Speech and Signal Processing (ICASSP), Atlanta, GA, March-April 1981, pp. 648–653.

M. Morf and D.T. Lee, “State-Space Structure of Ladder Canonical Forms,” Proc. 18th Conf. on Control and Design, Dec. 1980, pp. 1221–1224.

L. Séméria and G. De Micheli, “Synthesis of Pointers in C: Application of Pointer Analysis to the Behavioral Synthesis from C,” Proceedings of the International Conference on Computer-Aided Design (ICCAD 1998), San Jose, Nov. 1998.

T.J. Callahan and J. Wawrzynek, “Instruction Level Parallelism for Reconfigurable Computing,” FPL'98, Tallinn, Estonia, Sept. 1998, pp. 248–258. Publilshed in Springer-Verlag LNCS 1482.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Mencer, O., Séméria, L., Morf, M. et al. Application of Reconfigurable CORDIC Architectures. The Journal of VLSI Signal Processing-Systems for Signal, Image, and Video Technology 24, 211–221 (2000). https://doi.org/10.1023/A:1008145506415

Published:

Issue Date:

DOI: https://doi.org/10.1023/A:1008145506415