Abstract

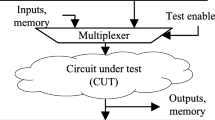

We present a method for obtaining a minimal set of test configurations and their associated set of test patterns that completely tests re-programmable Programmable Logic Arrays (PLAs) including EEPROM, UV-EPROM, and SRAM based re-programmable PLAs typically found in Complex Programmable Logic Devices (CPLDs). The resultant set of test configurations and vectors detect all single and multiple stuck-at faults (including line and transistor faults) as well as all bridging faults in the PLA. Previously proposed test methods proposed for EEPROM based PLAs (IEEE Trans. on CAD, Vol. 13, No. 7, pp.935–939, 1994;Proc. IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems, 1998, pp. 146–154) require additional test hardware as well as a large number of test configurations and vectors for complete testing. Our approach requires no modification to the PLA and only two or four test configurations, depending on the ratio of PLA product terms to inputs.

Similar content being viewed by others

References

V.K. Agarwal, “Multiple Fault Detection in Programmable Logic Arrays,” IEEE Trans. On Computers, Vol. C-29, No. 6, pp. 518–522, 1980.

P. Bose and J. Abraham, “Test Generation for Programmable Logic Arrays,” in Proc. 19th Design Automation Conf, 1982 pp. 574–580.

C. Cha, “A Testing Strategy for PLAs,” in Proc. ACM/IEEE Design Automation Conf., 1978, pp. 326–331.

E. Eichelberger and E. Lindbloom, “A Heuristic Test-Pattern Generator for Programmable Logic Arrays,” IBM J. of Research and Development, Vol. 24, No. 1, pp. 15–22, 1980.

H. Fujiwara, “A New PLA Design for Universal Testability,” IEEE Trans. on Computers, Vol. C-33, No. 8, pp. 745–750, 1984.

D. Ostapko and S. Hong, “Fault Analysis and Test Generation for Programmable Logic Arrays,” IEEE Trans. on Computers, Vol. C-28, No. 9, pp. 617–627, 1979.

D. Pradhan and K. Son, “The Effect of Undetectable Faults in PLAs and a Design for Testability,” in Proc. IEEE International Test Conf., 1980, pp. 359–367.

J. Smith, “Detection of Faults in Programmable Logic Arrays,” IEEE Trans. on Computers, Vol. C-28, No. 11, pp. 848–853, 1979.

R. Rajsuman, “A New Testing Method for EEPLA,” IEEE Trans. on CAD, Vol. 13, No. 7, pp. 935–939, 1994.

A. Munshi, F. Meyer, and F. Lombardi, “A New Method for Testing EEPLA's,” in Proc. IEEE International Symp. on Defect and Fault Tolerance in VLSI Systems, 1998, pp. 146–154.

K. Skahill, VHDL for Programmable Logic, Addison Wesley, Reading, MA, 1996.

J. Oldfield and R. Dorf, Field Programmable Gate Arrays, Wiley Interscience, New York, 1995.

Cypress Data Book CD-ROM, Cypress Semiconductor Corp., 1997.

MACH Family Data Book, Advanced Micro Devices, 1992.

D. Chess and T. Larrabee, “Bridge Fault Simulation Strategies for CMOS Integrated Circuits,” in Proc. ACM/IEEE Design Automation Conf., 1993, pp. 458–462.

Rights and permissions

About this article

Cite this article

Stroud, C.E., Bailey, J.R. & Emmert, J.R. A New Method for Testing Re-Programmable PLAs. Journal of Electronic Testing 16, 635–640 (2000). https://doi.org/10.1023/A:1008377405040

Issue Date:

DOI: https://doi.org/10.1023/A:1008377405040