Abstract

Cell Fault Model (CFM) is a well-adopted functional fault model used for cell-based circuits. Despite of the wide adoption of CFM, no test tool is available for the estimation of CFM testability. The vast majority of test tools are based on the single stuck-at fault model.

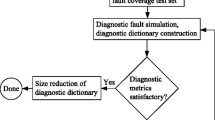

In this paper we introduce a method to calculate the CFM testability of a cell-based circuit using any single stuck-at fault based test tool. Cells are substituted by equivalent cells and Test Generation and Fault Simulation for CFM are emulated by Test Generation and Fault Simulation for a set of single stuck-at faults of the equivalent cells. The equivalent cell is constructed from the original cell with a simple procedure, with no need of knowledge of gate-level implementation, or its function. With the proposed methodology, the maturity and effectiveness of stuck-at fault based tools is used in testing of digital circuits, with respect to Cell Fault Model, without developing new tools.

Similar content being viewed by others

References

W.H. Kautz, “Testing for Faults in Cellular Logic Arrays,” Proc. 8th Annual Symposium of Switching and Automata Theory, 1967, pp. 161–174.

A.D. Friedman, “A Functional Approach to Efficient Fault Detection in Iterative Logic Arrays,” IEEE Trans. on Computers, Vol. 43, No. 12, pp. 1365–1375, Dec. 1994.

D. Gizopoulos, A. Paschalis, and Y. Zorian, “An Effective BIST Scheme for Carry-Save and Carry Propagate Array Multipliers,” Proc. 4th IEEE Asian Test Symposium, Nov. 1995, pp. 286–292.

D. Gizopoulos, A. Paschalis, and Y. Zorian, “An Effective BIST Scheme for Booth Multipliers,” Proc. IEEE Int. Test Conf., 1995, pp. 824–833.

D. Gizopoulos, A. Paschalis, Y. Zorian, and M. Psarakis, “An Effective BIST Scheme for Arithmetic Logic Units,” Proc. IEEE Int. Test Conf., 1997, pp. 868–877.

R.D. Blanton and J.P. Hayes, “Design of a Fast, Easily Testable ALU,” Proc. of the 14th IEEE VLSI Test Symposium, 1996, pp. 9–16.

D. Gizopoulos, A. Paschalis, and Y. Zorian, “An Effective BIST Scheme for Datapaths,” Proc IEEE Int. Test Conf., 1996, pp. 76–85.

M. Gharaybeh, M. Bushnell, and V. Agrawal, “Classification and Test Generation for Path-Delay Faults Using Single Stuckat Fault Tests,” Proc. IEEE Int. Test Conf., 1995, pp. 139– 148.

S.K. Jain and V.D. Agrawal, “Test Generation for MOS Circuit Using D-Algorithm,” Proc. DAC, 1983, pp. 64–70.

S.M. Reddy, V.D. Agrawal, and S.K. Jain, “A Gate-Level Model for CMOS Combinational Logic Circuits with Application to Fault Detection,” Proc. DAC, 1984, pp. 504–509.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Psarakis, M., Gizopoulos, D. & Paschalis, A. Test Generation and Fault Simulation for Cell Fault Model using Stuck-at Fault Model based Test Tools. Journal of Electronic Testing 13, 315–319 (1998). https://doi.org/10.1023/A:1008389920806

Issue Date:

DOI: https://doi.org/10.1023/A:1008389920806