Abstract

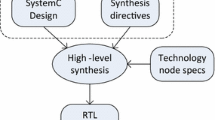

High-level synthesis tools generate register-transfer level designs from algorithmic behavioral specifications. The high-level synthesis process typically consists of dependency graph scheduling, functional unit allocation, register allocation, interconnect allocation and controller generation tasks. Widely used algorithms for these tasks retain the overall control flow structure of the behavioral specification allowing code motion only within basic blocks. Further, high-level synthesis algorithms are oblivious to the mathematical properties of arithmetic and logic operators. Selecting and sharing of RTL library modules are solely based on matching uninterpreted function symbols and constants. Many researchers have noted that these features of high-level synthesis algorithms can be exploited to develop efficient verification strategies for synthesized designs. This paper reports a verification technique that effectively exploits these features to achieve efficient and fully automated verification of synthesized designs and its incorporation in a high-level synthesis tool.

In our technique, a correctness condition generator is tightly integrated with a high-level synthesis tool to automatically generate (1) formal specifications of the behavior and the RTL design including the data path and the controller, (2) the correctness lemmas establishing equivalence between the synthesized RTL design and its behavioral specification, and (3) their proof scripts that can be submitted to a higher-order logic proof checker without further human interaction. This approach is based on the identification, by the synthesis tool during the synthesis process, of the binding between critical specification variables and critical registers in the RTL design, and between the critical states in the behavior and the corresponding states in the RTL design.

We have implemented our verification technique in conjunction with a relatively mature high-level synthesis tool. We report experimental results indicating the effectiveness of the proposed technique and summarize our ongoing work to further strengthen it.

Similar content being viewed by others

References

M. Aagaard and M. Leeser, “A formally verified system for logic synthesis,” Proceedings of 1991 IEEE International Conference on Computer Design, 1991.

M. Aagaard, M. Leeser, and P. Windley, “Towards a super duper hardware tactic,” HOL Theorem Proving System and its Applications, Springer-Verlag, 1993.

S. Basse, Computer Algorithms, Addison-Wesley, 1978.

R.A. Bergamaschi and S. Rajel, “Observable time windows: verifying the results of high-level synthesis,” IEEE Design & Test of Computers, 1997.

R.E. Bryant, “Symbolic boolean manipulation with ordered binary decision diagrams,” Technical Report CMU-CS-92-160, School of Computer Science, Carnegie Mellon University, 1992.

R.E. Bryant, “Binary decision diagrams and beyond: enabling technologies for formal verification,” Embedded Tutorial at International Conference on Computer-Aided Design, 1995.

J.R. Burch and D.L. Dill, “Automatic verification of pipelined microprocessor control,” Proceedings of Computer-Aided Verification, 1994.

R. Camposano and W. Wolf, High-Level VLSI Synthesis, Kluwer Academic Publishers, 1991.

L. Claesen, M. Genoe, E. Verlind, F. Proesmans, and H.D. Man, “SFG-tracing: a methodology of design for verifiability,” Proceedings of Advanced Workshop on Correct Hardware Design Methodologies, 1991.

L. Claesen, F. Proesmans, E. Verlind, and H.D. Man, “SFG-tracing: a methodology for the automatic veri-fication of MOS transistor level implementations from high-level behavioral specifications,” Proceedings of International Workshop on Formal Methods in VLSI Design, 1991.

E. Clarke, E. Emerson, and A. Sistla, “Automatic verification of finite-state concurrent systems using temporal logic specifications,” ACM Transactions on Prog. Lang. Syst., 1986.

F. Corella, “Automated verification of behavioral equivalence for microprocessors,” Research Report, IBM Research division, T.J. Watson Research Center, 1992.

F. Corella, “Automated high-level verification against clocked algorithmic specifications,” Proceedings of Computer Hardware Description Languages and Their Applications, 1993.

F. Corella, R. Camposano, R. Bergamaschi, and M. Payer, “Verification of synchronous sequential circuits obtained from algorithmic specifications,” Proceedings of International Workshop on Formal Methods in VLSI Design, 1991.

G. De-Micheli, Synthesis and Optimization of Digital Circuits, McGraw-Hill, 1994.

R. Dutta, J. Roy, and R. Vemuri, “Distributed design space exploration for high-level synthesis systems,” 29th Design Automation Conference, 1992.

D. Eisnbiegler and R. Kumar, “Formally embedding existing high level synthesis algorithms,” Correct Hardware Design and Verification Methods, Springer, 1995.

F. Feldbusch and R. Kumar, “Verification of synthesized circuits at register transfer level with flow graphs,” Proceedings of IEEE European Design Automation Conference, 1991.

D. Gajski, N. Dutt, A. Wu, and S. Lin, High-Level Synthesis, Introduction to Chip and System Design, Kluwer Academic Publishers, 1992.

S. Govindarajan and R. Vemuri, “Cone-based clustering heuristic for list scheduling algorithms,” Proceedings of the European Design and Test Conference, 1997.

S. Govindarajan and R. Vemuri, “Dynamic bounding of successor force computations in the force directed list scheduling algorithm,” Proceedings of International Conference on Computer Design, 1997.

D. Greve, “Symbolic simulation of the JEM1 microprocessor,” Proceedings of the 2nd International Conference on Formal Methods in Computer-Aided Design, 1998.

W. Hunt, FM8501: A Verified Microprocessor, Springer-Verlag, 1994.

S. Johnson, Synthesis of Digital Designs from Recursion Equations, MIT Press, 1984.

S. Katkoori, J. Roy, and R. Vemuri, “A hierarchical register optimization algorithm for behavioral synthesis,” Proceedings of International Conference on VLSI Design, 1996.

D.W. Knapp, Behavioral Synthesis: Digital System Design Using the Synopsys Behavioral Compiler, Prentice Hall, 1996.

T. Kropf, K. Schneider, and R. Kumar, “A formal framework for high level synthesis,” Theorem Provers in Circuit Design, Springer-Verlag, 1994.

F. Kurdahi and A. Parker, “REAL: A program for REgister ALlocation,” 24th Design Automation Conference, 1987.

N. Mansouri and R. Vemuri, “A methodology for completely automated verification of synthesized RTL designs and its integration with a high-level synthesis tool,” Proceedings of International Conference on Formal Methods in Computer-Aided Design, 1998.

M. McFarland, “An abstract model of behavior for hardware descriptions,” IEEE Transactions on Computers, 1983.

K.L. McMillan, Symbolic Model Checking: An Approach to the State Explosion Problem, Carnegie Mellon University, 1992.

J.S. Moore, “Symbolic simulation: an ACL2 approach,” Proceedings of the 2nd International Conference on Formal Methods in Computer-Aided Design, 1998.

N. Narasimhan, E. Teica, R. Radhakrishnan, S. Govindarajan, and R. Vemuri, “Theorem proving guided development of formal assertions in a resource-constrained scheduler for high-level synthesis,” Proceedings of International Conference on Computer Design (ICCD'98), 1998, pp. 392–399.

N. Narasimhan and R. Vemuri, “Specification of control flow properties for verification of synthesized VHDL designs,” Proceedings of International Conference in Formal Methods in Computer Aided Design, 1996.

N. Narasimhan and R. Vemuri, “Synchronous controller models for synthesis from communicating VHDL processes,” Ninth International Conference on VLSI Design, 1996.

N. Narasimhan and R. Vemuri, “On the effectiveness of theorem proving guided discovery of formal assertions for a register allocator in a high-level synthesis system,” Proceedings of 11th Conference on Theorem Proving in Higher Order Logics (TPHOL'98), 1998.

S. Owre, N. Shankar, and J.M. Rushby, “The PVS specification language (beta release),” 29th Design Automation Conference, 1992.

P. Pualin, J. Knight, and E. Girczyck, “HAL: a multi-paradigm approach to automatic data path synthesis,” 24th ACM/IEEE Desgin Automation Conference, 1986.

S. Rajan, “Correctness transformations in high level synthesis: formal verification,” Proceedings of the International Conference on Computer Hardware Description Languages, 1995.

S. Rajan, J. Joyce, and C. Seger, “From abstract data types to shift registers: a case study in formal specification and verification at differing levels of abstraction using theorem proving and symbolic simulation,” 6th International Workshop on Higher Order Logic Theorem Proving and Its Applications, 1993.

J. Roy, N. Kumar, R. Dutta, and R. Vemuri, “DSS: a distributed high-level synthesis system,” IEEE Design and Test of Computers, 1992.

S. Devadas, T. Ma, and R. Newton, “On verification of sequential machines at differing levels of abstraction,” IEEE Transactions on Computer-Aided Design, 1988.

N. Shankar, S. Owre, and J.M. Rushby, The PVS Proof Checker: A Reference Manual (Beta Release), 1993.

M.K. Srivas and S.P. Miller, “Formal verification of the AAMP5 microprocessor,” Applications of Formal Methods, Prentice Hall International, 1995.

L. Stok and R.V.D. Born, “Easy: multiprocessor architecture optimiztion,” Proceedings of International Workshop on Logic and Architecture Synthesis for Silicon Compilers, 1998.

A. Takach and W. Wolf, Scheduling Constraint Generation for Communicating Processes, Princeton University, 1993.

D. Thomas, C.Y. H. III, T. Kowalski, J. Rajan, and A. Walker, “Automatic data path synthesis,” IEEE Transactions on Computers, 1983.

D. Thomas, E. Lagnese, R. Walker, J. Nestor, J. Rajan, and R. Blackburn, Algorithmic and Register Transfer Level Synthesis: The System Architect's Workbench, Kluwer Academic Publishers, 1990.

D.E. Thomas, R.L. Blackburn, and J.V. Rajan, “Linking the behavioral and structural domains of representation for digital system design,” IEEE Transactions on Computer Aided Design, 1987.

C. Tseng and D.P. Siewiorek, “Facet: a procedure for the automated synthesis of digital systems,” 20th ACM/IEEE Design Automation Conference, 1983.

R. Vemuri, “On the notion of normal form register-level structures and its applications in design-space exploration,” Proceedings of IEEE European Design Automation Conference, 1990.

R. Vemuri, P. Mamtora, P. Sinha, N. Kumar, and J.R.R. Vutukuru, “Experiences in functional validation of a high level synthesis system,” Proceedings of 30th ACM/IEEE Design Automation Conference, 1993.

R. Walker and R. Camposano, A Survey of High-Level Synthesis Systems, Kluwer Academic Publishers, 1990.

P. Windley, The Practical Verification of Microprocessor Designs, Compcon, 1991.

P.J. Windley, “Verifying pipelined microprocessors,” Proceedings of the International Conference on Computer Hardware Description Languages, 1995.

N. Woo, “A global, dymanic register allocation and binding for data path synthesis system,” 27th Design Automation Conference, 1990.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Mansouri, N., Vemuri, R. Automated Correctness Condition Generation for Formal Verification of Synthesized RTL Designs. Formal Methods in System Design 16, 59–91 (2000). https://doi.org/10.1023/A:1008777509016

Issue Date:

DOI: https://doi.org/10.1023/A:1008777509016