Abstract

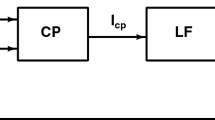

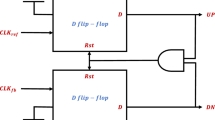

Due to a number of desirable operational and design characteristics, CP-PLL's (Charge Pump Phase locked loops) have, in recent years become a pervasive PLL architecture. CP-PLL architectures are exploited for a variety of applications such as on chip clock generation, CRC (clock recovery circuits) and Radio frequency synthesis applications. This paper describes a simple, digital only, minimally invasive and fully automated test approach for high performance CP-PLL's that can be used to provide more information about the CP-PLL function beyond that obtained through the commonly used FLT (Frequency Lock Test). The test strategy described here allows the estimation of forward path (FP) gain and relative leakage in the forward path loop components. Applications of the test are focussed towards digital only testing of fully embedded CP-PLL's, however further test modifications could yield marked test time improvements for embedded and board level CP-PLL's incorporating multiple CP currents and or multiple loop filter (LF) configurations.

Similar content being viewed by others

References

F. Azais, M. Renovell, Y. Bertrand, A. Ivanov, and S. Tabatabaei, “A Unified in Digital Test Technique for PLL's; Catastropic Faults Covered,” in Proc 5th IMSTW, June 1999.

D. Banerjee, PLL Performance Simulation and Design, Copyright 1998 National Semiconductors, http://www.national.com.

R. Best, Phase Locked Loops, Design Simulation and Applications, 4th edition, Mc-Graw-Hill, ISBN 0071349030.

M. Burbidge, A. Richardson, and A. Lechner, “Test Techniques for Embedded Charge Pump PLL's; Problems, Current BIST Techniques, and Alternative Suggestions,” in Proc 7th IMSTW, 2001, pp. 97-103.

A. Chan and G.W. Roberts, “A Synthesizeable, Fast And High-Resolution Timing Measurement Device Using A Component-Invariant Vernier Delay Line,” in Proc. ITC01 Proc., 2001, pp. 858-867.

M. Dalmia, A. Ivanov, and S. Tabatabaei, “Power Supply Current Monitoring Techniques for Testing PLL's,” in Proc. Asian Test Symposium, 1997, pp. 366-371.

A. DeHon, “In-System Timing Extraction and Control Through Scan-Based, Test-Access Ports,” M.I.T. Transit Project, Transit Note No. 102, 1994.

Fluence, “VCOBIST,” IEEE DAC, June 1999. http://www.fluence.com/bistmaxx/presentvco/index.htm.

F.M. Gardner, “Charge-Pump Phase-Lock Loops,” IEEE Trans. Comm., pp. 1849-1858, 28th Nov. 1980.

K. Jenkins and J. Eckhardt, “Measuring Jitter and Phase Error in Microprocessor Phase-Locked Loops,” IEEE Design and Test of Computers, Vol. 17, Issue 2, pp. 86-93, April-June 2000.

S. Kim and M. Soma, “An Effective Defect-Oriented BIST Architecture for High Speed Phase Locked Loops,” in Proc. IEEE VLSI Test Symposium, April 2000, pp. 231-236.

P. Larson, “Measurements and Analysis of PLL Jitter Caused by Digital Switching Noise,” IEEE Journal of Solid-State Circuits, pp. 1113-1120, July 2001.

B. Razavi (Ed.), Monolithic Phase-Locked Loops and Clock Recovery Circuits: Theory and Design, IEEE Press 1996, ISBN 0780311493.

G.W. Roberts, M. Hafed, and N. Abraskharoun, “A Stand Alone Integrated Test Core For Time And Frequency Based Measurements,” in Proc. Int. Test Conf., 2000, pp. 1031-1041.

M. Sachdev, Defect Oriented Testing for CMOS Analog and Digital Circuits, Kluwer Academic Publishers, pp. 37-38 and 79-81, 1998.

S. Sunter and A. Roy, “BIST for Phased Locked Loops in Digital Applications,” in Proc. IEEE ITC99, 1999, pp. 532-540.

S. Tabatabaei and A. Ivanov, “An Embedded Core for High-Accuracy Testing of IC Timing Circuit Verifications,” in Proc. 8th IMSTW, June 2002, pp. 227-237.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Burbidge, M.J., Poullet, F., Tijou, J. et al. Investigations for Minimum Invasion Digital Only Built-In “Ramp” Based Test Techniques for Charge Pump PLL's. Journal of Electronic Testing 19, 481–490 (2003). https://doi.org/10.1023/A:1024604412648

Issue Date:

DOI: https://doi.org/10.1023/A:1024604412648