Abstract

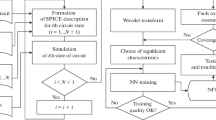

This paper presents a new approach for detecting defects in analog integrated circuits using the feed-forward neural network trained by the resilient error back-propagation method. A feed-forward neural network has been used for detecting catastrophic faults randomly injected in a simple analog CMOS circuit by classification the differences observed in supply current responses of good and faulty circuit. The experimental classification was performed for time and frequency domain, followed by a comparison of results achieved in both domains. It was shown that neural networks might be very efficient and versatile approach for test of analog circuits since an arbitrary fault class or circuit's parameter can be analyzed. Considered defect types and their successful detection by the neural network; and a possible off-chip hardware implementation of the proposed technique are discussed as well. Moreover, optimized hardware architecture of the selected neural network type was designed using VHDL for FPGA realization.

Similar content being viewed by others

References

J.M. Acken, “Testing for Bridging Faults (shorts) in CMOS Devices,” in Proc. Design Autom. Conf., 1983, pp. 717-718.

J. Arguelles, M. Martinez, and S. Bracho, “Dynamic I DD Test Circuit for Mixed-Signal Ics,” Electronics Letters, vol. 30, pp. 485-486, 1994.

J.S. Beasley, A.W. Righter, C.J. Apodaca, S. Pour-Mazafari, and D. Huggett, “IDD Pulse Response Testing Applied to Complex CMOS Ics,” in Proc. Int. Test. Conf., 1997, pp. 32-39.

I.M. Bell, D.A. Camplin, G.E. Taylor, and B.R. Bannister, “Supply Current Testing of Mixed Analogue and Digital ICs,” Electronics Letters, vol. 27, pp. 1581, 1991.

H. Demuth and M. Beale, Neural Network Toolbox User's Guide, The Mathworks Inc, 1998.

A. Germida, Z. Yan, J.F. Plusquellic, and F. Muradali, “Defect Detection using Power Supply Transient Signal Analysis,” in Proc. Int. Test. Conf., 1999, pp. 67-76.

R.P. Gorman and T.J. Sejnowski, “Analysis of Hidden Units in a Layered Network Trained to Classify Sonar Targets,” Neural Networks, vol. 1, pp. 75-89, 1988.

Z. Guo, Zhang Xi Min, J. Savir, and Shi Yun-Qing, “On Test and Characterization of Analog Linear Time-Invariant Circuits Using Neural Networks,” in Proc. 10th Asian Test Symposium, 2001, pp. 338-343.

C.F. Hawkins and J.M. Soden, “Electrical Characteristics and Testing Considerations for Gate Oxide Shorts in CMOS IC's,” in Proc. Int. Test. Conf., 1985, pp. 544-555.

S. Haykin, Neural Networks-A Comprehensive Foundations, Macmillan College Publishing Co., 1994.

B. Kruseman, P. Janssen, and V. Zieren, “Transient Current Testing of 0.25 mm CMOS Devices,” in Proc. Int. Test. Conf., 1999, pp. 47-56.

Y. Maidon, B.W. Jervis, P. Fouillat, and S. Lesage, “Using Artifi-cial Neural Networks or Lagrange Interpolation to Characterize the Faults in an Analog Circuit: An Experimental Study,” IEEE Transactions on Instrumentation and Measurement, vol. 48, no. 5, pp. 932-938, 1999.

A. Materka, “Neural Network Technique for Parametric Testing of Mixed-Signal Circuits,” Electronics Letters, vol. 31, no. 3, pp. 183-184, 1995.

M. Riedmiller and H. Braun, “A Direct Adaptive Method for Faster Backpropagation Learning: The RPROP Algorithm,” in Proc. IEEE Int. Neural Networks, 1993, pp. 586-591.

N. Sbirrazzuoli and D. Brunel, “Computational Neural Networks for Mapping Calorimetric Data: Application of Feedforward Neural Networks to Kinetic Parameters Determination and Signals Filtering,” Neural Computing & Applications, vol. 5, pp. 20-32, 1997.

J. Segura, M. Roca, D. Mateo, and A. Rubio, “Built-in Dynamic Current Sensor Circuit for Digital VLSI CMOS Testing,” Electronics Letters, vol. 30, pp. 1668-1669, 1994.

V. Stopjakova, H. Manhaeve, and M. Sidiropulos, “On-Chip Transient Current Monitor for Testing of Low-Voltage CMOS IC,” in Proc. Design. Autom. and Test in Europe, 1999, pp. 538-542.

S.-T. Su, R.Z. Makki, and T. Nagle, “Transient Power Supply Current Monitoring-A New Test Method for CMOS VLSI Circuits,” JETTA, vol. 6, pp. 23-43, 1995.

S.F. Zornetzer, J.L. Davis, C. Lau, and T. McKenna, An Introduction to Neural and Electronic Networks, 2nd edn., Academic Press, 1995.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Stopjaková, V., Malošek, P., Mičušík, D. et al. Classification of Defective Analog Integrated Circuits Using Artificial Neural Networks. Journal of Electronic Testing 20, 25–37 (2004). https://doi.org/10.1023/B:JETT.0000009311.63472.d6

Issue Date:

DOI: https://doi.org/10.1023/B:JETT.0000009311.63472.d6