Abstract

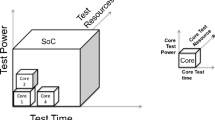

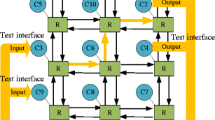

The test scheduling problem is one of the major issues in the test integration of system-on-chip (SOC), and a test schedule is usually influenced by the test access mechanism (TAM). In this paper we propose a graph-based approach to power-constrained test scheduling, with TAM assignment and test conflicts also considered. By mapping a test schedule to a subgraph of the test compatibility graph, an interval graph recognition method can be used to determine the order of the core tests. We then present a heuristic algorithm that can effectively assign TAM wires to the cores, given the test order. With the help of the tabu search method and the test compatibility graph, the proposed algorithm allows rapid exploration of the solution space. Experimental results for the ITC02 benchmarks show that short test length is achieved within reasonable computation time.

Similar content being viewed by others

References

J. Aerts and E.J. Marinissen, “Scan Chain Design for Test Time Reduction in Core-Based ICs,” in Proc. Int. Test Conf. (ITC), 1998, pp. 448-457.

K. Chakrabarty, “Design of System-on-a-Chip Test Access Architecture Under Place-and-Route and Power Constraints,” in Proc. IEEE/ACM Design Automation Conf. (DAC), 2000, pp. 432-437.

K. Chakrabarty, “Design of System-on-a-Chip Test Access Architecture Using Integer Linear Programming,” in Proc. IEEE VLSI Test Symp. (VTS), 2000, pp. 127-134.

K. Chakrabarty, “Test Scheduling for Core-Based Systems Using Mixed-Integer Linear Programming,” IEEE Trans. Computer-Aided Design of Integrated Circuits and Systems, vol. 19, no. 10, pp. 1163-1174, 2000.

R.M. Chou, K.K. Saluja, and V.D. Agrawal, “Scheduling Tests for VLSI Systems Under Power Constraints,” IEEE Trans. VLSI Systems, vol. 5, no. 2, pp. 175-185, 1997.

G.L. Craig, C.R. Kime, and K.K. Saluja, “Test Scheduling and Control for VLSI Built-in Self-Test,” IEEE Trans. Computers, vol. 37, no. 9, pp. 1099-1109, 1988.

F. Glover, E. Taillard and D. de Werra, “A User's Guide to Tabu Search,” Annals of Operations Research, vol. 41, pp. 3-28, 1993.

S.K. Goel and E.J. Marinissen, “Cluster-Based Test Architecture Design for System-on-Chip,” in Proc. IEEE VLSI Test Symp. (VTS), Monterey, 2002, pp. 259-264.

S.K. Goel and E.J. Marinissen, “Effective and Efficient Test Architecture Design for SOCs,” in Proc. Int. Test Conf. (ITC), Baltimore, 2002, pp. 529-538.

M.C. Golumbic, Algorithmic Graph Theory and Perfect Graphs, New York: Academic Press, 1980.

W.-L. Hsu and T.-H. Ma, “Fast and Simple Algorithm for Recognizing Chordal Comparability Graphs and Interval Graphs,” SIAM J. Computing, vol. 28, no. 3, pp. 1004-1020, 1999.

Y. Huang,W.-T. Cheng, C.-C. Tsai, N. Mukherjee, O. Samman, Y. Zaidan, and S.M. Reddy, “Resource Allocation and Test Scheduling for Concurrent Test of Core-Based SOC Design,” in Proc. Tenth IEEE Asian Test Symp. (ATS), Kyoto, pp. 265-270, 2001.

Y. Huang, S.M. Reddy, W.-T. Cheng, and P. Reuter, “Optimal Core WrapperWidth Selection and SOC Test Scheduling Based on 3-D Bin Packing Algorithm,” in Proc. Int. Test Conf. (ITC), Baltimore, 2002, pp. 74-82.

V. Iyengar and K. Chakrabarty, “Precedence-Based, Preemptive, and Power-Constrained Test Scheduling for System-on-a-Chip,” in Proc. IEEE VLSI Test Symp. (VTS), 2001, pp. 368-374.

V. Iyengar and K. Chakrabarty, “Test Bus Sizing for System-ona-Chip,” IEEE Trans. Computers, vol. 51, no. 5, pp. 449-459, 2002.

V. Iyengar, K. Chakrabarty, and E.J. Marinissen, “Test Wrapper and Test Access Mechanism Co-Optimzation for System-on-Chip,” in Proc. Int. Test Conf. (ITC), Baltimore, 2001, pp. 1023-1032.

V. Iyengar, K. Chakrabarty, and E.J. Marinissen, “Integrated Wrapper/TAM Co-Optimization, Constraint-Driven Test Scheduling, and Tester Data Volumne Reduction for SOCs,” in Proc. IEEE/ACM Design Automation Conf. (DAC), New Orleans, 2002, pp. 685-690.

V. Iyengar, K. Chakrabarty, and E.J. Marinissen, “On Using Rectangle Packing for SOC Wrapper/TAM Co-Optimization,” in Proc. IEEE VLSI Test Symp. (VTS), Monterey, 2002, pp. 253-258.

V. Iyengar,K. Chakrabary, and E.J. Marinissen, “Efficient Wrapper/ TAM Co-Optimization for Large SOCs,” in Proc. Design, Automation and Test in Europe (DATE), Paris, 2002, pp. 491-498.

E. Larsson and Z. Peng, “An Integrated System-On-Chip Test Framework,” in Proc. Design, Automation and Test in Europe (DATE), Munich, 2001, pp. 138-144.

E. Marinissen, R. Kapur, and Y. Zorian, “On Using IEEE P1500 SECT for Test Plug-n-Play,” in Proc. Int. Test Conf. (ITC), 2000, pp. 770-777.

E.J. Marinissen, S. Goel, and M. Lousberg, “Wrapper Design for Embedded Core Test,” in Proc. Int. Test Conf. (ITC), 2000, pp. 911-920.

E.J. Marinissen and S.K. Goel, “Analysis of Test Bandwidth Utilization in Test Bus and TestRail Architectures for SOCs,” in Proc. IEEE Int. Workshop on Design and Diagnostics of Electronic Circuits and Systems (DDECS), 2002, pp. 52-60.

E.J. Marinissen, V. Iyengar, and K. Chakrabarty, “A Set of Benchmarks for Modular Testing of SOCs,” in Proc. Int. Test Conf. (ITC), Baltimore, 2002, pp. 519-528.

V. Muresan, X.Wang,V. Muresan, and M. Vladutiu, “AComparison of Classical Scheduling Approaches in Power-Constrained Block-Test Scheduling,” in Proc. Int. Test Conf. (ITC), 2000, pp. 882-891.

C.-P. Su and C.-W. Wu, “Graph-Based Power-Constrained Test Scheduling for SOC,” in Proc. IEEE Int. Workshop on Design and Diagnostics of Electronic Circuits and Systems (DDECS), Brno, Czech Republic, 2002, pp. 61-68.

Y. Zorian, E.J. Marinissen, and S. Dey, “Testing Embedded-Core Based System Chips,” in Proc. Int. Test Conf. (ITC), 1998, pp. 130-143.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Su, CP., Wu, CW. A Graph-Based Approach to Power-Constrained SOC Test Scheduling. Journal of Electronic Testing 20, 45–60 (2004). https://doi.org/10.1023/B:JETT.0000009313.23362.fd

Issue Date:

DOI: https://doi.org/10.1023/B:JETT.0000009313.23362.fd