Abstract

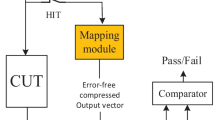

We present a BIST architecture based on a Multi-Input Signature Register (MISR) expanding single input vectors into sequences, which are used for testing of delay faults. Input vectors can be stored on-chip or in the ATE; in the latter case, a low speed tester can be employed though the sequences are applied at-speed to the block-under-test. The number of input vectors (and thus the area demand on-chip or ATE memory requirements) can be traded for the test application time.

We propose several methods for generating input vectors, which differ in test application time, area requirements and algorithm run-time. As all of them require only a two-pattern test as input, IP cores can be handled by these methods.

The block-under-test can be switched off for some amount of time between application of consecutive input vectors. We provide arguments why this approach may be the only way to meet thermal and power constraints. Furthermore, we demonstrate how the BIST scheme can use these cool-down breaks for re-configuration.

Similar content being viewed by others

References

M. Abramovici, M.A. Breuer, and A.D. Friedman, Digital Systems Testing and Testable Design. Computer Science Press, 1990.

R.C. Aitken, “Finding Defects with Fault Models,” in Proc. Int'l Test Conf., 1995, pp. 498-505.

P.H. Bardell, W.H. McAnney, and J. Savir, Built-In Test for VLSI: Pseudorandom Techniques. John Wiley & Sons, 1987.

A. Biere, A. Cimatti, E. Clarke, and Y. Zhu, “Symbolic Model CheckingWithout BDDs,” in Tools and Algorithms for the Constuction and Analysis of Systems, LNCS, vol. 1579. Springer Verlag, 1999.

F. Brglez, D. Bryan, and K. Kozminski, “Combinational Profiles of Sequential Benchmark Circuits,” in Proc. Int'l Symp. Circ. and Systems, pp. 1929-1934, 1989.

J.L. Carter, V.S. Iyengar, and B.K. Rosen, “Efficient Test Coverage Determination for Dealy Faults,” in Proc. Int'l Test Conf., 1987, pp. 418-427.

K. Chakrabarty, “Design of System-on-Chip Test Access Architectures Using Integer Linear Programming,” in Proc. VLSI Test Symp., pp. 127-134, 2000.

K. Chakrabarty, “Test Scheduling for Core-based Systems Using Mixed Integer-Linear Programming,” IEEE Trans. on CAD, vol. 19, no. 10, pp. 1163-1174, 2000.

K. Chakrabarty, B.T. Murray, and V. Iyengar, “Built-in test Pattern Generation for High Performance Circuits Using Twisted-Ring Counters,” in Proc. VLSI Test Symp., 1999, pp. 22-27.

A. Chandra and K. Chakrabarty, “Low-Power Scan Testing and Test Data Compression for System-on-a-Chip,” IEEE Trans. on CAD, vol. 21, no. 5, pp. 597-604, 2002.

C.-A. Chen and S.K. Gupta, “BIST: Test Pattern Generator for Two-Pattern Testing-Theory and Design Algorithms,” IEEE Trans. on Computers, pp. 257-279, 1996.

C.-A. Chen and S.K. Gupta, “Design of Efficient BIST: Test Pattern Generators for Delay Testing,” IEEE Trans. on Computers, pp. 1568-1575, 1996.

F. Corno, M. Rebaudengo, and M. Sonza-Reorda, “Low Power BIST via Nonlinear Hybrid Cellular Automata,” in Proc. VLSI Test Symp., pp. 29-34, 2000.

V. Dabholkar, S. Chakravarty, I. Pomeranz, and S.M. Reddy, “Techniques for Minimizing Power Dissipation in Scan and Combinational Circuits during Test Applications,” IEEE Trans. on CAD, vol. 17, no. 12, pp. 1325-1333, 1998.

K. Furuya and E.J. McCluskey, “Two-Pattern Test Capabilities of Autonomous TPG Circuits,” in Proc. Int'l Test Conf., 1992, pp. 704-711.

S. Gerstendörfer and H. Wunderlich, “Minimized Power Consumption for Scan-Based BIST,” Jour. of Electronic Testing: Theory and Applications, vol. 16, no. 1, pp. 203-212, 2000.

P. Girard, C. Landrault ans V. Moreda, and S. Pravossoudovitch, “An Optimized Test Pattern Generation Method for Delay Fault Testing,” in Proc. VLSI Test Symp., 1997, pp. 94-100.

P. Girard, C. Landrault ans V. Moreda, S. Pravossoudovitch, and A. Virazel, “A scan-BIST Structure to Test Delay Faults in Sequential Circuits,” Jour. of Electronic Testing: Theory and Applications, vol. 14, no. 5, pp. 95-102, 1999.

S. Hellebrand, H.G. Liang, and H.J. Wunderlich, “A Mixed-Mode BIST Scheme Based on Reseeding of Folding Counters,” Jour. of Electronic Testing: Theory and Applications, vol. 17, no. 3/4, pp. 159-170, 2001.

S. Hellebrand, J. Rajski, S. Tarnick, S. Venkataraman, and B. Courtois, “Built-in Test for Circuits With Scan Based on Reseeding of Multiple-Polynomial Linear Feedback Shift Register,” IEEE Trans. on Comp., vol. 44, no. 2, pp. 223-233, 1995.

S. Hellebrand, S.Tarnick, B. Courtois, and J. Rajski, “Generation of Vector Patterns Through Reseeding of Multiple-Polynomial Linear Feedback Shift Registers,” in Proc. Int'l Test Conf., 1992, pp. 120-129.

M. Henftling and H.Wittmann, “Bit Parallel Test Pattern Generation for Path Delay Faults,” in European Design and Test Conf., pp. 521-525, March 1995.

K. Heragu, J.H. Patel, andV.D. Agrawal, “Segment Delay Faults: A New Fault Model,” in Proc. VLSI Test Symp., 1996, pp. 32-39.

A. Hett, C. Scholl, and B. Becker, A.MORE-A Multi-Operand BDD Package. University of Freiburg, 1999.

Y. Huang, W.-T. Cheng, C.-C. Tsai, N. Mukherjee, O. Samman, Z. Yahia, and S.M. Reddy, “Resource Allocation and Test Scheduling for Concurrent Test of Core-Based SOC Design,” in Proc. Asian Test Symp., 2001, pp. 265-270.

T. Kam, T. Villa, R. Brayton, and A. Sangiovanni-Vincentelli, “A fully Implicit Algorithm for Exact State Minimization,” in Proc. Design Automation Conf., 1994, pp. 684-690.

M. Keim, I. Polian, H. Hengster, and B.Becker, “A Scalable BIST Architecture for Delay Faults,” in Proc. European Test Workshop, 1999, pp. 98-103.

B. Könemann, “LFSR-Coded Test Patterns for Scan Designs,” in Proc. European Design & Test Conf., 1992, pp. 237-242.

C.V. Krishna, A. Jas, and N.A. Touba, “Test Vector Encoding Using Partial LFSR Reseeding,” in Proc. Int'l Test Conf., 2001, pp. 885-893.

E. Larsson, K. Arvidsson, H. Fujiwara, and Z. Peng, “Integrated Test Scheduling, Test Parallelization and TAMDesign,” in Proc. Asian Test Symp., 2002, pp. 397-404.

E. Lindbloom, J.A. Waicukauski, B. Rosen, and V. Iyengar, “Transition Fault Simulation by Parallel Pattern Single Fault propagation,” in Proc. Int'l Test Conf., 1986, pp. 542-549.

A.K. Majhi and V.D. Agrawal, “Tutorial: Delay Fault Models and Coverage,” in VLSI Design, 1998, pp. 364-369.

A.K. Majhi, J. Jacob, L.M. Patnaik, and V.D. Agrawal, “On Test Coverage of Path Delay Faults,” in VLSI Design, 1996, pp. 418-421.

M.W. Moskewicz, C.F. Madigan, Y. Zhao, L. Zhang, and S. Malik, “Chaff: Engeneering an Efficient SAT Solver,” in Proc. Design Automation Conf., 2001.

N. Mukherjee, T.J. Chakraborty, and S. Bhawmik, “A BIST Scheme for the Detection of Path-Delay Faults,” in Proc. Int'l Test Conf., 2002, pp. 422-431.

J. Tyszer, N. Zacharia, and J. Rajski, “Decompresseion of Test Data Using Variable-Length Seed LFSRs,” in Proc. VLSI Test Symp., 1995, pp. 426-433.

S. Pilarski and A. Perzyńska, “BIST and Delay Fault Detection,” in Proc. Int'l Test Conf., 1993, pp. 236-242.

I. Polian and B. Becker, “Stop & go BIST,” in IEEE Int'l Online Testing Workshop, 2002, pp. 147-151.

I. Polian and B. Becker, “Configuring MISR-based Two-Pattern BIST using Boolean Satisfiability,” in Proc. IEEE Int'lWorkshop on Design and Diagnostics of Electronic Circuits and Systems (DDECS), 2003, pp. 73-80.

I. Pomeranz and S.M. Reddy, “A Partitioning and Storage-based Built-in Test Pattern Generation Method for Delay Faults in Scan Circuits,” in Proc. Asian Test Symp., 2002, pp. 110-115.

C.P. Ravikumar, G. Chandra, and A. Verma, “Simultaneous Module Selection and Scheduling for Power-Constrained Testing of Core Based Systems,” in VLSI Design, 2000.

C.P. Ravikumar, A. Verma, and G. Chandra, “A Polynomial-Time Algorithm for Power Constrained Testing of Core Based Systems,” in Proc. Asian Test Symp., 1999, pp. 107-112.

G.L. Smith, “Model for Delay Faults Based upon Paths,” in Int'l Test Conf., 1985, pp. 342-349.

C.W. Starke, “Built-in Test for CMOS Circuits,” in Proc. Int'l Test Conf., 1984, pp. 309-314.

M. Sugihara, H. Date, and H. Yasuura, “A Novel Test Methodology for Core-Based System LSIs and a Testing Time Minimization Problem,” in Proc. Int'l Test Conf., 1998, pp. 465-472.

P. Tafertshofer, A. Ganz, and M. Henftling, “A SAT-Based Implication Engine for Efficient ATPG, Equivalence Checking and Optimization of Netlists,” in Proc. Int'l Conf. on CAD, 1997, pp. 648-655.

A.J. van der Goor, Testing Semiconductors Memories, Theory and Practice. ComTex Publishing, 1998.

A. Vuksic and K. Fuchs, “A New BIST Approach for Delay Fault Testing,” in EDAC-ETC-EUROASIC, 1994, pp. 284-288.

S. Wang and S. Gupta, “An Automatic Test Pattern Generator for Minimizing Switching Activity during Scan Testing Activity,” IEEE Trans. on CAD, vol. 21, no. 8, pp. 954-968, 2002.

S. Wang and S. Gupta, “DS-LFSR: A BIST TPG for Low Switching Activity,” IEEE Trans. on CAD, vol. 21, no. 7, pp. 842-851, 2002.

W. Wang and S.K. Gupta, “Weighted Random Robust Path Delay Testing of Synthesized Multilevel Circuits,” in Proc. VLSI Test Symp., 1994, pp. 291-297.

B. Wurth and K. Fuchs, “A BIST Approach to Delay Fault Testing with Reduced Test Length,” in Proc. European Design & Test Conf., 1995, pp. 418-423.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Polian, I., Becker, B. Scalable Delay Fault BIST for Use with Low-Cost ATE. Journal of Electronic Testing 20, 181–197 (2004). https://doi.org/10.1023/B:JETT.0000023681.25483.59

Issue Date:

DOI: https://doi.org/10.1023/B:JETT.0000023681.25483.59