Abstract

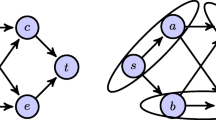

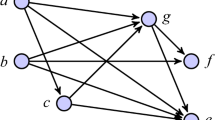

We propose a net clustering based RT-level macro-cell placement approaches. Static timing analysis identifies critical nets and critical primary input/output paths. Net clustering (based on shared macro-cells and net criticality) yields clusters wherein each cluster has strongly interdependent nets. The circuit is modeled as a graph in which each vertex v represents a net and each edge (v,u) a shared cell between nets v and u. The net clusters are obtained by applying a clique partitioning algorithm on the circuit graph. Two approaches to generate placements at RTL are proposed: constructive (cluster growth) approach and iterative improvement (simulated annealing) based approach. In the constructive approach, a cluster-level floorplanning is performed and a cluster ordering is obtained. The cluster ordering is used by a constructive procedure to generate the physical placement. In the case of iterative improvement based approach, a good ordering of clusters is obtained using simulated annealing.

We report experimental results for five RTL datapaths implemented in 0.35 μm technology to demonstrate the efficacy of the proposed approaches. We compared the layouts produced by our approaches with those produced by Flint, an automatic floor planner in Lager IV Silicon Compiler [1]. For constructive placement approach, we obtained an average decrease of 43.4% in longest wirelength and 32.4% in total wirelength. The average area reduction is 7.3%. On the other hand, for the SA-based approach, we obtained an average decrease of 57.6% in longest wirelength and 42.2% in total wirelength. The average reduction in the bounding-box area is 12.3%. As expected, the SA-based approach yielded better optimization results, due to its ability to climb out of local minima.

Similar content being viewed by others

References

R.W. Broderson (Ed.), Anatomy of a Silicon Compiler. Kluwer Academic Publishers, 1992.

R.W. Broderson (Ed.), The National Technology Roadmap for Semiconductors. SIA (Semiconductor Industry Association), 1997.

J. Cong and A. Kahng, “Net Partitions Yield Better Module Partitions,” in Proc. Design Automation Conf., June 1992, pp. 47-52.

J. Cong, K.Y. Khoo, C.K. Koh, and Z. Pan, “Interconnect Design for Deep Submicron ICs,” in Proceedings of International Conference on Computer Aided Design, Nov. 1997, pp. 478-485.

D. Sylvester and K. Kuetzer, “Getting to the Bottom of Deep Submicron,” in Proceedings of International Conference on Computer-Aided Design, 1998, pp. 203-211.

R.H.J.M. Otten and R.K. Brayton, “Planning for Performance,” in Proceedings of the Design Automation Conference, June 1998, pp. 122-127.

P. Chong, Y. Jiang, S. Khatri, F. Mo, S. Sinha, and R. Brayton, “Don't Care Wires in Logic/Physical Design,” in Proceedings of the Design Automation Conference, 2000, pp. 1-9.

A. Salek, J. Lou, and M. Pedram, “A DSM Design Flow: Putting Floorplanning, Technology-Mapping, and Gate Placement Together,” in Proceedings of the Design Automation Conference, 1998, pp. 128-133.

A.B. Kahng et al., “Interconnect Tuning Strategies for High-Performance Ics,” 1997.

J. Cong et al., “Performance Optimization of VlSI Interconnect Layout,” in Integration, the VLSI Journal, 1996, pp. 1-94.

A.E. Caldwell, A.B. Kahng, S. Mantik, I.L. Markov, and A. Zelikovski, “On Wirelength Estimations for Row-Based Placement,” in Proceedings ACM/IEEE Intl. Symp on Physical Design, 1998, pp. 4-11.

A.B. Kahng and S. Muddu, “Efficient Gate Delay Modelling for Large Interconnect Loads,” in Proceedings of the IEEE Multi-Chip Module Conference, 1996, pp. 202-207.

S. Alupoaei and S. Katkoori, “Net-Based Force-Directed Macrocell Placement for Wirelength Optimization,” IEEE Trans. on VLSI Systems, Dec. 2002, pp. 824-835.

Sadiq M. Sait and Habib Youssef, VLSI Physical Design Automation, McGraw-Hill, 1995 chap. 4, p. 143.

C. Sechen et al., “The TimberWolf Placement and Routing Package,” in Proc. Custom Integrated Circuits Conference, May 1984.

M.A. Breuer, “Min-cut Placement,” in J. Design Automation and Fault-Tolerant Computing, 1977, pp. 343-382.

B. Kernighan and A. Dunlop, “A Procedure for Placement of Standard-Cell VLSI Circuits,” IEEE Trans. CAD, vol. CAD-4, 1985, pp. 92-98.

M. Marek-Sadowska and S.P. Lin, “Timing Driven Placement,” in Proceedings of International Conference on Computer Aided Design, Nov. 1989, pp. 94-97.

S. Prasitjutrakul and W.J. Kubitz, “A Timing-Driven Global Router for Custom Chip Design,” in Proceedings of International Conference on Computer Aided Design, Nov. 1990, pp. 48-51.

K. Chaudhary et al., “RITUAL: Performance-Driven Placement of Cell-Based ICs,” in Proc. 3rd Physical Design Workshop, May, 1991.

C.-K. Cheng, J. Huang, X.-L. Hong, and E.S. Kuh, “An Efficient Timing Driven Global Routing Algorithm,” in Proceedings of the Design Automation Conference, 1993, pp. 596-600.

A.E. Dunlop et al., “Chip Layout Optimization Using Critical Path Weighting,” in DAC, 1984, pp. 133-136.

M.A.B. Jackson and E.S. Kuh, “Performance-Driven Placement of Cell Based IC's,” in DAC, 1989, pp. 370-375.

C. Tseng and D.P. Siewiorek, “Facet: A Procedure for the Automated Synthesis of Digital Systems,” in 20th ACM/IEEE Design Automation Conference, 1983, pp. 490-496.

D.F. Wong and C.L. Liu, “A New Algorithm for Floorplan Design,” in Proceedings of the Design Automation Conference, 1986, pp. 101-107.

Electronic Products, “Novel IC Shuffles Parallel Processing Data,” Aug. 1986, pp. 42-50.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Alupoaei, S., Katkoori, S. Net Clustering Based Constructive and Iterative Improvement Approaches for Macro-Cell Placement. The Journal of VLSI Signal Processing-Systems for Signal, Image, and Video Technology 37, 151–163 (2004). https://doi.org/10.1023/B:VLSI.0000017008.38412.54

Published:

Issue Date:

DOI: https://doi.org/10.1023/B:VLSI.0000017008.38412.54