## A Real Time Predictive Maintenance System of Aluminium Electrolytic Capacitors Used in Uninterrupted Power Supplies

Karim Abdennadher, Pascal Venet, Gérard Rojat, Jean-Marie Rétif, Christophe Rosset

### ▶ To cite this version:

Karim Abdennadher, Pascal Venet, Gérard Rojat, Jean-Marie Rétif, Christophe Rosset. A Real Time Predictive Maintenance System of Aluminium Electrolytic Capacitors Used in Uninterrupted Power Supplies. IAS '08, Oct 2008, Edmonton (Alberta), Canada. pp.1 - 6, 10.1109/08IAS.2008.171. hal-00369572

HAL Id: hal-00369572

https://hal.science/hal-00369572

Submitted on 3 Jun 2009

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# A Real time predictive maintenance system of Aluminium Electrolytic Capacitors used in Uninterrupted Power Supplies

Karim Abdennadher\*, Pascal Venet<sup>†</sup>, Gérard Rojat<sup>†</sup>, Jean-Marie Retif<sup>‡</sup>and Christophe Rosset\*

\*Emerging Technologies Department - Critical Power and Cooling Services Schneider Electric - INOVALEE - Montbonnot St Martin - 38334 Saint Ismier, France Email: karim.abdennadher@mgeups.com

<sup>†</sup>Laboratoire AMPERE, Université de Lyon, Université Lyon 1 43, Boulevard du 11 Novembre 1918 Bâtiment Oméga 69622 Villeurbanne Cedex - France Phone: +33(0)4 72 43 11 92 Fax: +33(0)4 72 43 11 93

<sup>‡</sup>Laboratoire AMPERE, INSA de Lyon 20, rue Albert Einstein Bâtiment Léonard de Vinci 69621 villeurbanne Cedex - France

Abstract—This paper presents a low cost method to realize a real time condition monitoring and a predictive maintenance system of an electrolytic capacitor used in Uninterrupted Power Supplies (UPS). This method consists in detecting the changes on real time in equivalent series resistance (ESR) and the capacitance C values of the electrolytic capacitors. Simulation and experimental results are presented to illustrate the proposed monitoring technique. The proposed method can be used in UPS where waveforms are continuously varying in amplitude, frequency and versus temperature. The proposed on line failure prediction method has the merits of using only the existent resources in UPS and with the use of knower algorithms.

Index Terms—Electrolytic capacitors, predictive maintenance, real time, identification, Kalman filter.

#### I. INTRODUCTION

Electrolytic capacitors have been widely used in power electronic systems because they can achieve high capacitance and voltage ratings with volumetrically efficient and low cost. This type of capacitors have been traditionally used for filtering, coupling, timing networks, by-pass and many other applications in power electronics requiring a cost effective and volumetrically efficient component. It's known that the common faults in electrolytic capacitor include initial catastrophic failures due to manufacturing or misapplication defect, and wear-out faults which cannot be avoided. Unfortunately, electrolytic capacitors are one of the weakest components in power electronics converter [1-13]. For example [1], [4], in Uninterrupted Power Supplies (UPS), they are responsible in about 50% cases of power electronics component failures. Electrolytic capacitor has a number of root causes and failure modes. Degradation of this component is due to a combined effect of electrical, thermal, mechanical and environmental stresses. The main wear-out failure mecha-

nism is the evaporation of the electrolyte solution which is accelerated with temperature rise during the operation and due to ripple currents. This causes a decrease in C and an increase of ESR which further increase temperature (losses). Standard [2] suggests that the capacitor should be considered as failed if there is a double increase of the initial ESR value and a 20% decrease in the capacitance one. Hence, the estimation of the ESR and the capacitance by taking into account the temperature is important for condition monitoring of the electrolytic capacitor. The purpose of this paper is to propose a method to detect in real time the changes in the value of the ESR and also the capacitance in order to create a real time predictive system of electrolytic capacitor failures. It is further shown in this paper that the proposed method can be applied even in the non-stationary system such as UPS where capacitor ripple voltage and current are continuously varying in amplitude and frequency. They also depend on the ambient temperature where the converter operates.

Many papers have proposed different methods or algorithms to determine the ESR and/or capacitance C of the electrolytic capacitor [2-13]. However, many parameters such as off-line additional measurements and many computations are required, which makes it complicated, difficult, expensive and impractical for actual application.

Nowadays, UPS dispose of many accurate sensors, numerical treatment systems and powerful computation resources which are used to control and regulate UPS in order to improve its performance and efficiency. The suggested method has the merits of making a real time predictive maintenance system of electrolytic capacitors by using existing resources in the UPS. This predictive maintenance system works in background task and without disturbing the regulation and the operating system.

#### II. ELECTROLYTIC CAPACITOR TECHNOLOGY

#### A. Electrolytic capacitor modeling

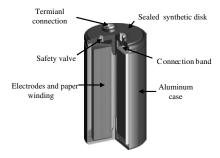

The structure of a screw terminals electrolytic capacitor [16] is shown in Fig.1.

Fig. 1. Structure of a screw terminals electrolytic capacitor [16]

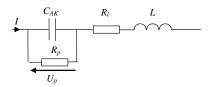

Due to the physical design elements and construction, aluminium electrolytic capacitors are modeled by the electrical equivalent circuit [14], [17] given in Fig.2. This model, which is the most used one, is rather simple and gives a good frequency response.

Fig. 2. Electrical equivalent circuit of an electrolytic capacitor

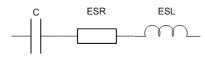

Where  $C_{AK}$  is the ideal capacitance between anode and cathode,  $R_p$  is the parallel resistance which represents all the losses in the dielectric and the leakage between the two electrodes,  $R_l$  is the connection and electrodes serial resistance and L is connection and winding equivalent series inductance. This circuit can be simplified with the normalized representation given in Fig.3. It is a serial combination of an Equivalent Series Resistance which represents all the component losses, a capacitance C and an equivalent serial inductance, ESL, which is due to the wound structure of the capacitor.

Fig. 3. Normalized electrical equivalent circuit of an electrolytic capacitor

From the impedance equality between the circuit elements represented in Fig.2 and those represented in Fig.3, we can conclude the following equations where  $\omega$  is the electrical pulsation.

$$C = C_{AK} \cdot \left(1 + \frac{1}{R_p^2 C_{AK}^2 \omega^2}\right)$$

(1)

$$ESR = R_l + \frac{R_p}{1 + R_p^2 C_{AK}^2 \omega^2}$$

(2)

$$ESL = L (3)$$

This capacitor representation is important because it's directly given from the impedance frequency measurements. Therefore, the resonant frequency  $f_r$  of the capacitor is given by this equation.

$$f_r = \frac{1}{2.\pi \cdot \sqrt{ESL.C}} \tag{4}$$

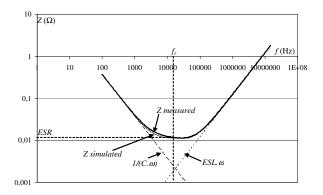

In addition, this simplified equivalent circuit can give a first approximation of the capacitor behavior without taking into account parameters' variation C, ESR and ESL versus frequency. This theory can be demonstrated by the figure given below (Fig.4) which represents the module Z of the complex impedance Z versus frequency, of an aluminum electrolytic capacitor of  $4700~\mu F/500~\rm V$ . As it can be observed from bode-plot, there exist three widely separated frequency bands. Capacitance of the capacitor is dominant in low frequency band. ESL is dominant in high frequency band and ESR is dominant in the mid frequency one.

Fig. 4. Z(f) for aluminum electrolytic capacitor of 4700  $\mu F$  / 500 V

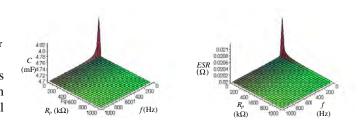

The equations (1) and (2) show that ESR and C can be considered separately from the frequency when this latter is not too low. Therefore, the resistance  $R_p$  has an effect only on very low frequencies (less than several tens of Hz). This is shown in the Fig.5 which represents the effect of  $R_p$  versus frequency f on the ESR and C parameters. It is an example of an electrolytic capacitor with a nominal capacitance value of  $4700~\mu F$  and a nominal equivalent serial resistance of  $20~m\Omega$ .

Fig. 5. Z(f) for aluminum electrolytic capacitor of 4700  $\mu F$  / 500 V [17]

#### B. Electrolytic capacitors aging

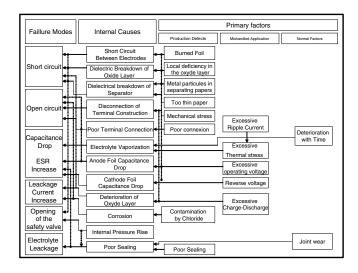

The figure below [17] shows the majority of electrolytic capacitor root causes and failure modes. As it can be seen, the

Fig. 6. Capacitor failures and their causes [17]

estimation of ESR and C can provide at least all the normal and uses failure defects. Therefore, the estimation of these two parameters is important to realize a real time predictive maintenance system of electrolytic capacitor.

#### III. ELECTROLYTIC CAPACITOR MONITORING

#### A. Estimation of ESR and C

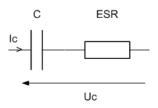

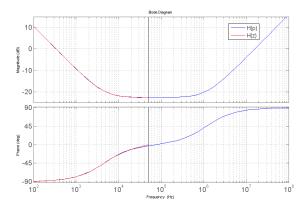

As we have just seen before, the electrolytic capacitors can be modeled as a serial combination of a capacitance, an equivalent series inductance and an equivalent series resistance as showing in Fig.3. The bode-plot of an electrolytic capacitor with equivalent series resistance,  $ESR=74~m\Omega$  equivalent series inductance ESL=10~nH and the capacitance  $C=470~\mu F$  is presented in Fig.8. Therefore, converters in UPS works at low frequency band compared with the resonant frequency's one (4), so ESL is usually neglected and the equivalent model of the capacitor is given through Fig.7.

Fig. 7. Capacitor equivalent model for frequency range used in power converter

The transfer function of this model is given by:

$$H(p) = \frac{Uc(p)}{Ic(p)} = \frac{ESR.C.p + 1}{C.p}$$

(5)

However, converters are controlled by using digital treatments. We can consider the z-transform corresponding of equation (5) to represent the discrete time domain by using the bilinear method of Tustin and which is given by the following equation where Te is the sampling period.

$$H(z^{-1}) = \frac{b_0 + b_1 \cdot z^{-1}}{1 - z^{-1}}$$

$$= \frac{\left(ESR + \frac{Te}{2.C}\right) + \left(\frac{Te}{2.C} - ESR\right) \cdot z^{-1}}{1 - z^{-1}}$$

(6)

The bode-plot in Fig.8 shows that, the continuous and discrete time domain for a sampling period of  $Te=10~\mu s$ , are equivalent if we use the bilinear method discrete time.

Fig. 8. Bode plot of electrolytic capacitor in continuous and discrete time domain

To identify  $b_0$  and  $b_1$  so the two parameters ESR and C, we use different forms of Kalman filter.

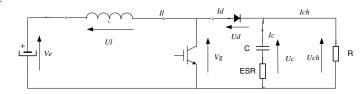

A Matlab simulation was performed using dynamic equation from equivalent circuit shown in Fig.9 a the boost-converter with 50 V DC voltage input, for a switching frequency of 5 kHz and which is regulated to have 200 V DC voltage output.

Fig. 9. Schematic of a boost converter circuit with a DC capacitor circuit

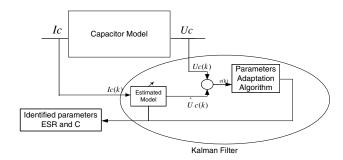

A Recursive Least Square Algorithm which is a particular case of Kalman filter was used like presented in Fig.10.

In practice, we don't have a capacitor current sensor, because it is difficult and expansive to implement in UPS. To perform and regulate the output voltage, we only dispose of one current sensor used to have the input current inductance L of the boost converter. However, we can identify the capacitor current with using Kirchhoff's laws referring to the schematic of the boost

Parameters identification with using Kalman filter

converter given in Fig.9.

$$Ic = Id - Ich \tag{7}$$

When the IGBT is off (the pulse width modular PWM=0), we have Id = Il, so we can conclude the following equation.

$$Id = Il * \overline{PWM} \tag{8}$$

In stationary process, the average capacitor current Ic is equal to zero, so for one regulation period Te, you have the following equation.

$$Ic = Il * \overline{PWM} - avg \left( Il * \overline{PWM} \right) \tag{9}$$

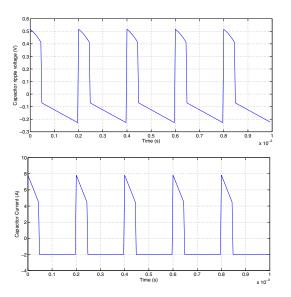

Respectively, simulation results of the capacitor ripple voltage, and capacitor current identified with the use of (9) are shown in Fig.11.

Fig. 11. Matlab Simulation results of capacitor ripple voltage  $\Delta Uc$  and capacitor current Ic

Simulation results presented in this section are summarized in Table I.

#### B. Aging Algorithm

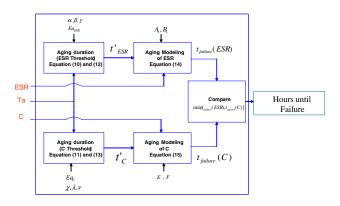

The aging algorithm which takes into account the temperature is given below.

TABLE I SIMULATION RESULTS FOR ESTIMATED PARAMETERS

| ESR <sub>actual</sub> | $ESR_{estimated}$ | % error |

|-----------------------|-------------------|---------|

| 74 $m\Omega$          | 74.2 $m\Omega$    | 0.2     |

| $C_{actual}$          | $C_{estimated}$   | % error |

| $470~\mu F$           | $466~\mu F$       | 0.7     |

Evolution of ESR and C versus ambient temperature  $T_a$  is given by the following equation [14] where  $\alpha, \beta, \gamma$  and  $\chi, \nu, \lambda$ are experimental parameters and depend on the used capacitor.

$$ESR(T_a) = \alpha + \beta \cdot \exp\left(-\frac{T}{\gamma}\right)$$

(10)

$$C(T_a) = \chi + \lambda \cdot \exp\left(-\frac{T}{\nu}\right)$$

(11)

Time until failure compared to failure limits of ESR and C can be calculated by using the equations below [14].

$$\frac{t_{ESR}^{'}}{ta_{ESR}} = \exp\left[\frac{Ea_{ESR}}{k} \cdot \frac{T^{'} - T_a}{(T^{'} + 273) \cdot (T_a + 273)}\right]$$

(12)

$$\frac{t_C'}{ta_C} = \exp\left[\frac{Ea_C}{k} \cdot \frac{T' - T_a}{(T' + 273) \cdot (T_a + 273)}\right]$$

(13)

$$ESR(t_{ESR}) = (ESR(0) + A_1) \cdot \exp(B_1 \cdot t_{ESR})$$

(14)

$$C(t_C) = E.C(0) + F.t_C$$

(15)

$T_a$ : Ambient temperature (25 °C for example). T': Aging temperature (85 °C for example).

$ta_{ESR}$ : Aging time for the ESR limit at  $T_a$ .

$ta_C$ : Aging time for the C limit at  $T_a$ .

$t_{ESR}^{'}$ : life time limit at  $T^{'}$  with ESR aging indicator.  $t_{C}$ : life time limit at  $T^{'}$  with C aging indicator.

$t_{ESR}$ : time until failure with ESR aging indicator.

$t_C$ : time until failure with C aging indicator.

$k = Boltzmann constant (8,617.10^{-5} eV/^{\circ}K).$

$Ea_{ESR}$ : Activation energy with ESR aging indicator.

$Ea_C$ : Activation energy with C aging indicator.

$A_1, B_1, E$  and F are experimental parameters and also depend on the used capacitor.

The time until failure of the capacitor is given by the lower computed time between ESR time failure limit and C time failure limit as showing in Fig.12.

#### C. experimental study

1) Experimental setup: To verify the validity of the proposed method, an experimental study was performed on a Boost-converter with an input DC voltage of 50 V, 470  $\mu F$  -450 V filtering capacitor, an R-load of 100  $\Omega$  and a switching frequency of 5 kHz. Therefore a fixed point DSP controller (TMS320F2812) was used for Il, Uc, Ic and capacitor ripple voltage  $\Delta Uc$  acquisition measurements and switching operations required to perform 200 V DC output voltage. To do that, we choose the two imbricated loop principle, one fast current loop with a Proportional/ Integrator (PI) controller to perform

Fig. 12. Aging algorithm

the current reference and another external voltage loop with a Deadbeat controller to perform the 200 V DC output voltage. Moreover, a recursive least square algorithm (a particular case of Kalman filter) has been implemented to work in background task and to identify the two parameters ESR and C.

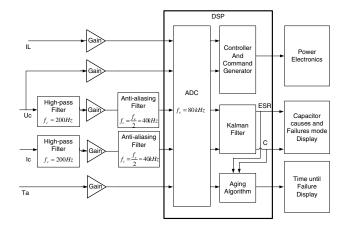

In literature [15], we know that using different cases of Kalman filter provides centered input and output system measurements which are respectively capacitor current and capacitor voltage. Therefore, the capacitor voltage and the capacitor current are passed through a high-pass filter with cut-off frequency of around  $f_c = 200 \ Hz$  to suppress DC component of voltage measurements and without including phase shift. Consequently, we have only the capacitor ripple voltage which is in phase with capacitor current.

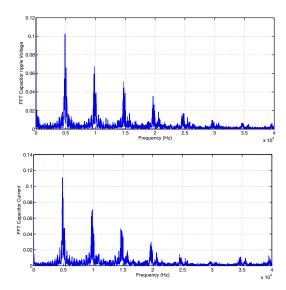

An FFT analysis respectively on the capacitor ripple voltage and capacitor current is shown in Fig.13 and we see that the bandwidth of the system is about 30 kHz and 35 kHz. Therefore and to respect Shannon theorem we choose a sampling frequency  $f_s = 80 \ kHz$ . To eliminate signal distortion an anti-

Fig. 13. FFT analysis of capacitor ripple voltage and capacitor voltage for a sampling frequency  $f_s = 80 \ kHz$

aliasing Filter [15] with a cut-off frequency  $f_c = \frac{f_s}{2} \approx 40kHz$  It can be clearly seen that there is a non significant error

is used as it is shown in the global capacitor condition monitoring scheme Fig.14.

Fig. 14. Real time electrolytic capacitor condition monitoring in UPS

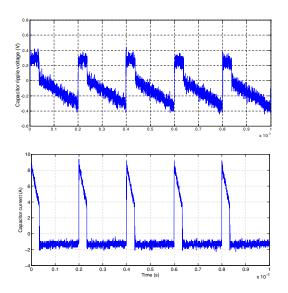

2) Experimental results: The experimental measurements on the scope of Capacitor ripple voltage, and capacitor current are shown in Fig.15

Fig. 15. Capacitor ripple voltage and capacitor current

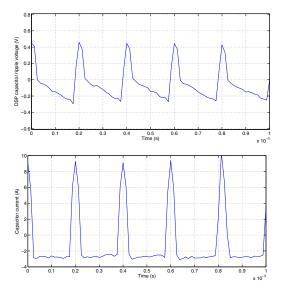

The corresponding numerical DSP measurements (after the Analog to Digital Converter) of capacitor ripple voltage and capacitor current are given in Fig.16.

Experimental results for the estimated parameters are summarized in Table II.

TABLE II EXPERIMENTAL RESULTS FOR ESTIMATED PARAMETERS

| $\mathrm{ESR}_{actual}$ | $ESR_{identified} = [ESR_{min}; ESR_{max}]$ | % error |

|-------------------------|---------------------------------------------|---------|

| 75.1 m $\Omega$         | [71.3 m $\Omega$ ,78.8 m $\Omega$ ]         | +/-5    |

| $C_{actual}$            | $C_{identified}$ =[ $C_{min}$ ; $C_{max}$ ] | % error |

| $472~\mu F$             | [466 μF, 518 μF]                            | +/-10   |

Fig. 16. Capacitor ripple voltage and Capacitor current on DSP with a sampling frequency  $f_s=80\ kHz$

between estimated and actual values of ESR and C. These results are consistent with the measured value using an impedancemeter.

#### IV. CONCLUSION

Due to their large capacity and low cost, electrolytic capacitors with the abilities of energy storage and voltage regulation are used for almost all types of power electronics system. Electrolytic capacitors, which are usually affected by wear-out faults, plays a very important role for the quality and reliability of power-electronics system. Therefore it is important to monitor the condition of an electrolytic capacitor in real-time to predict the failure. A new method is proposed to detect in real time the changes in ESR and capacitance C value by taking into account the ambient temperature in order to create a real-time failure prediction of an electrolytic capacitor. For the proposed method, capacitor current and capacitor ripple voltage measurements using cheap and simple analog circuits are required. Simulation results and hardware experimental show that the proposed electrolytic capacitor failure-prediction technique can be applied to a power-electronics system successfully.

#### REFERENCES

- [1] Military Handbook 217 F, Reliability prediction of electronic equipment, Feb. 28, 1995.

- [2] P. Venet, H. Darnand, and G. Grellet, Dectection of faults of filter capacitors in a converter. Application to predictive maintenance, International Telecommunications Energy conference, pp.229-234, 1993.

- [3] P. Venet, F. Perisse, M.H. El-Husseini, and G. Rojat, Realization of a smart electrolytic capacitor circuit IEEE Industry Applications Magazine, vol. 8, no. 1, pp. 16-20, Jan./Feb. 2002.

- [4] A. Lahyani, P. Venet, G. Grellet, and P.J. Viverge, Failure prediction of electrolytic capacitors during operation of a switchmode power supply, IEEE Transactions on Power Electronics, No. 6, pp. 1197 - 1207, 1998.

- [5] K. Harada, A. Katsuki, and M. Fujiwara, *Use of ESR for deterioration diagnosis of electrolytic capacitor* IEEE Transactions on Power Electronics, vol. 8, no. 4, pp. 355-361, Oct. 1993.

- [6] A.M. Imam, T.G. Habetler, R.G. Harley, and D.M. Divan, Condition monitoring of electrolytic capacitor in power electronic circuits using adaptive filter modeling, Proc. of IEEE PESC, pp. 601-607, Sept. 2005.

- [7] E. Aeloiza, J.H. Kim, P. Enjeti, P. Ruminot, A Real Time Method to Estimate Electrolytic Capacitor Condition in PWM Adjustable Speed Drives and Uninterruptible Power Supplies, pp. 2867 - 2872, 2005.

- [8] A.M. Imam, T.G. Habetler, R.G. Harley, and D.M. Divan, Real-Time Condition Monitoring of the Electrolytic Capacitors for Power Electronics Applications, Proc. of IEEE Applied Power Electronics Conference and Exposition, pp. 1057 - 1061, 2007.

- [9] M.L. Gasperi, Life prediction modeling of bus capacitors in ac variable-frequency drives, IEEE Transactions on Industry Applications, vol. 41, no. 6, pp. 1430-1435, Nov./Dec. 2005.

- [10] V.A. Sankaran, F.L. Rees, and C.S. Avant, Electrolytic capacitor life testing and prediction, Proc. of IEEE IAS Annual Meeting, pp. 1058-1065, Oct. 1997.

- [11] O. Ondel, E. Boutleux, and P. Venet, A decision system for electrolytic capacitors diagnosis, Proc. of IEEE PESC, pp. 4360-4364, June 2004.

- [12] D.C. Lee, J.K. Seok, and J.W. Choi, Online Capacitance Estimation of DC-link Electrolytic Capacitors for Three-phase AC/DC/AC PWM Converters using Recursive Least Squares Method, IEE Proceedings -Electric Power Applications, vol. 152, no. 6, pp. 1503 - 1508, Nov. 2005.

- [13] Kim Myungchul, Lee Kwangwoon, Yoon Jangho, Lee Sang Bin, Yoo Jiyoon, Condition Monitoring of DC Link Electrolytic Capacitors in Adjustable Speed Drives, Industry Applications Conference, 2007. 42nd IAS Annual Meeting. Conference Record of the 2007 IEEE Volume, Issue, 23-27 Sept. 2007 Page(s):237 243

- [14] F. Perisse, P. Venet, G. Rojat, J.M. Retif, Simple Model of Electrolytic Capacitor Taking into Account the Temperature and Aging Time Electrical Engineering (Archiv fur Elektrotechnik), Vol. 88, n 2, January 2006, pp 89-95.

- [15] I.D. Landau, G. Zito, Digital Control Systems Design, Identification and Implementation, Springer Publications, 2006.

- [16] J. Martinez-Vega, Matériaux diélectriques pour le génie électrique 2 -Applications spécifiques, Hermes Editions, 2007.

- [17] F. Perisse, Etude et analyse des modes de défaillances des condensateurs électrolytiques a l'aluminium et des thyristors, appliquées au système de protection du LHC (Large Hardon Collider), Master's thesis, Claude Bernard University, Lyon, France, 2003.