# Specifying and verifying requirements of real-time systems

Ravn, Anders P.; Rischel, Hans; Hansen, Kirsten Mark

Published in:

I E E E Transactions on Software Engineering

Link to article, DOI: 10.1109/32.210306

Publication date: 1993

Document Version

Publisher's PDF, also known as Version of record

Link back to DTU Orbit

Citation (APA):

Ravn, A. P., Rischel, H., & Hansen, K. M. (1993). Specifying and verifying requirements of real-time systems. *I E E Transactions on Software Engineering*, 19(1), 41-55. https://doi.org/10.1109/32.210306

# **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

- You may not further distribute the material or use it for any profit-making activity or commercial gain

- You may freely distribute the URL identifying the publication in the public portal

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Specifying and Verifying Requirements of Real-Time Systems

Anders P. Ravn, Member, IEEE, Hans Rischel, Member, IEEE, and Kirsten Mark Hansen

Abstract-An approach to specification of requirements and verification of design for real-time systems is presented. A system is defined by a conventional mathematical model for a dynamic system where application specific states denote functions of real time. Specifications are formulas in duration calculus, a realtime interval logic, where predicates define durations of states. Requirements define safety and functionality constraints on the system or a component. A top-level design is given by a control law: a predicate that defines an automaton controlling the transition between phases of operation. Each phase maintains certain relations among the system states; this is analogous to the control functions known from conventional control theory. The top-level design is decomposed into an architecture for a distributed system with specifications for sensor, actuator, and program components. Programs control the distributed computation through synchronous events. Sensors and actuators relate events with system states. Verification is a deduction showing that a design implies requirements.

Index Terms— Real-time systems, requirements engineering, specification, verification.

### I. INTRODUCTION

N engineer who is designing an embedded computer A system must have a deep insight in the properties of the controlled physical processes. When the system is safety critical, it becomes particularly important that this insight be made explicit and forms the basis for design. This was already observed by Heninger [12] in connection with the A7 flight program, and the viewpoint is pursued in later work by Parnas, for example [32]-[34] and appears also in [18]. It has led to increased focus on requirements engineering [4]. The challenge, however, is to find suitable mathematical theories and notations that allow a designer to record such insight. It is also crucial, but often neglected, that the theory shall make it practical for a designer to use mathematical reasoning when checking that a design conforms to the requirements. In our work with case studies within the Provably Correct Systems (ProCoS) project [3] we have studied the problem of specifying and verifying total system requirements [13], [36], [37]. This paper describes the resulting approach to

Manuscript received August 1, 1992. This work was partially supported by the Commission of the European Communities (CEC) under the ESPRIT program in the field of Basic Research Action, project 3104: "ProCoS: Provably Correct Systems," and by the Danish Technical Research Council under the "RapID" program. A previous version of this paper was presented at the ACM Sigsoft '91 Conference on Software for Critical Systems, New Orleans, LA, December 1991. Recommended by N. G. Leveson and P. G. Neumann.

The authors are with the Department of Computer Science, Technical University of Denmark, DK 2800 Lyngby, Denmark.

IEEE Log Number 9205026.

T

requirements engineering, design, and verification for real-time control systems.

A central property of such systems is that they can be modeled by states changing over time. The theory of dynamic systems, see, e.g., [23], or more specifically control theory, see, e.g., [7], [22], are rather specialized, however. They concentrate on systems that can be described by a single invariant or control law in the form of a differential equation, or in the discrete case a difference equation with a fixed time step. In order to be really tractable, the equations are restricted to be linear, although some results have been reached for nonlinear systems, e.g., [17]. Dynamic systems theory is thus not readily applicable to systems with varying time steps, nondeterministic state changes, or with control laws that depend on modes of operation. Furthermore, the notations are not well suited for composition of interacting systems, see e.g., part XII of [46].

Composition seems the only way of dealing with the complex state spaces that arise whenever programming is involved, thus we were led to investigate logic where the intimate relationship between conjunction and composition of concurrently active systems [16] can be used as a composition principle. The logic should also be able to specify real-time constraints, and not just partial ordering of actions. There are many realtime logics, but they seem to fall into two broad classes: explicit time or implicit time. With explicit time formalisms, time is an ordinary variable, represented by event occurrence symbols as in RTL [19]. The time variable may also represent a time interval, see, e.g., [43], or it may be a variable in a temporal logic [35]. In explicit time logic, timing constraints are encoded as inequations over arithmetic expressions in time variables. Through some experiments we found this approach to be less satisfactory because there is no clear relationship between a natural language formulation of constraints and the resulting inequations. We observed that the timing constraints seem to be formulated as constraints on the duration of critical states. Implicit time logic, e.g., metric temporal logic [21], [35] or ISL [9] recognize this by using temporal operators that constrain the extent of a state. It is, however, not possible to express critical durations of the following form: "Within any period of length T, the critical state S must only occur c% of the time." Such formulations describe a constraint on the sum of an arbitrary number of extents and leads to a duration concept, i.e., a logic where time is observed through the accumulated presence of a state. It was through joint work in the ProCoS project that duration calculus emerged [47]. It is based on interval temporal logic [1], [2], [10], [29],

0098-5589/93\$03.00 © 1993 IEEE

[42] and the duration concept. Duration calculus gives us the means to describe critical durations, progress from state to state, and stability of a state. Furthermore, it has a set of rules that have been useful when reasoning about timing properties.

Concurrently with development of duration calculus, we experimented with ways of applying the theory in a systematic manner to requirements specification, design, and verification. Through many iterations the following approach has emerged:

- 1) Top-level requirements are specified by constraints on a set of entities X representing the relevant physical states as a function of real time. The constraints are typically a conjunction of formulas. One class of formulas constrain the duration of critical states. Another class of formulas specify progress properties: within a certain time the system should move from one state to another.

- 2) A top-level design is given by some assumptions and a control law. The assumptions record the intrinsic design of the physical system (the Nat relation in [34]). They are requirements that the system imposes on the environment, for instance, that certain states are considered physically impossible or that certain progress properties are ensured by physical processes. The control law consists of two parts:

- A finite state machine or automaton describing how control progresses through a number of phases. This is specified by a formula over a phase control state p.

- b) A set of phase requirements that for each phase define progress and stability constraints to be satisfied during that phase. A phase requirement determines also whether the phase is stable or control shall enter a new phase.

- 3) An architecture is defined. It consists of specifications for a set of concurrently operating sensor, actuator and program components that synchronize through events. This distributed system is controlled by a scheduler. The scheduler maintains a trace state tr, recording the sequence of events passed between components. In order to ensure that a conjunction of component specifications remain consistent, we cannot allow upper bounds on the duration of a phase (this reflects that a set of synchronized state machines can only move when all are ready). Upper bounds are thus rewritten as readiness to progress, using a private state Ref (cf. [16]) for each component. The scheduler ensures progress when all components indicate that they are ready to proceed. The system state X is also distributed as private states for components.

This is an outline of the approach; but we hasten to add that there are still many points that need investigation; we return to some of these points in the conclusion. A similar approach to Requirements Capture and top-level design is found in Parnas' work [34]. Use of finite state automatons to specify designs for safety-critical systems are also investigated in [18] and as a paradigm for fault-tolerant systems in [40]. It is also the basis for the ProCoS program specification language [31]

and the Statechart formalism [15]. The decomposition into an architecture is primarily inspired by Roscoe and Reed's work on timed CSP [38], [41], and He Jifeng's work on real-time semantics [20].

Section II summarizes duration calculus. Section III presents the running example and the (informal) requirements. Section IV formalizes system requirements. Section V introduces a top-level design with a control law. The top-level design is verified in section VI. Section VII specifies the architecture. Verification is in Section VIII, followed by the conclusion in Section IX.

### II. SPECIFICATION LANGUAGE

We use the well-known *time-domain model* of systems and control theory [7], [22], [23] for modeling systems. A system is described by a collection of *states* (often called state variables) that are functions of *time*, modeled by the real numbers.

Properties of systems are expressed by constraining the states over time. We wish to express requirements and design without explicit mentioning of particular time instants, and introduce a notation that is a real-time interval logic based on state durations [14], [47].

### A. Syntax

We assume (upper case) names  $X, Y, \ldots$  for the states together with (notation for) their value domains  $Type_X$ ,  $Type_Y, \ldots$ , given in a suitable specification language, such as  $\mathbf{Z}$  (cf. [44]) or  $\mathbf{VDM}$  (cf. [5]). This language must comprise a number of standard data types with operators and constants, including the type  $\mathbf{R}$  of real numbers and the type  $\mathbf{Bool}$  of Boolean. We denote the Boolean constants by tt and ff (the names true and false are reserved for duration formulas). We use lower-case names  $a, b, \ldots, x, y, \ldots$ , to denote constants and variables of any type. As usual in mathematical logic, a variable is an arbitrary value that may be bound by a quantifier, whereas a constant is fixed in each interpretation.

State Expressions and State Assertions. A state expression may be of any type and is generated by

- 1) Any state, constant and variable is a state expression.

- 2) Any well-formed expression formed from an n-ary operator symbol and state expressions  $S_1, \ldots, S_n$  is a state expression.

A state assertion is a state expression of type Bool.

Durations and Duration Terms. For any state assertion P,  $\int P$  is a duration and of type  $\mathbf{R}$ . A duration term is also of type  $\mathbf{R}$  and generated by

- Durations, real constants, and real variables are duration terms

- 2) Any well-formed expression formed from an n-ary operator symbol of type  $\mathbf{R}$  and duration terms  $r_1, \ldots, r_n$  is a duration term.

The symbol  $\ell$  is used as an abbreviation for  $\int tt$ .

Duration Formulas. Any expression formed from an n-ary predicate symbol on  $\mathbf{R}$  and duration terms  $r_1, \ldots, r_n$  is an atomic duration formula. A duration formula is of type Bool

and generated by

- 1) Atomic duration formulas and the special symbols true and false are duration formulas.

- 2) If  $\mathcal{D}_1$  and  $\mathcal{D}_2$  are duration formulas, so are the expressions  $(\neg \mathcal{D}_1)$ ,  $(\mathcal{D}_1 \vee \mathcal{D}_2)$  and  $(\forall x)\mathcal{D}_1$ , where x is a variable.

- 3) If  $\mathcal{D}_1$  and  $\mathcal{D}_2$  are duration formulas, so is the expression  $(\mathcal{D}_1; \mathcal{D}_2)$ .

### **B.** Semantics

An interpretation  $\mathcal I$  of our formal system corresponds to a particular execution (run) of the system, where each state X denotes a function

$$\mathcal{I}(X):[0,\infty)\to Type_X$$

giving the state as function of time from the start t=0, and where each constant a is interpreted as a value  $\mathcal{I}(a)$  of appropriate type. For given interpretation  $\mathcal{I}$ , a valuation  $\mathcal{V}$  asigns a value  $\mathcal{V}(x)$  to each variable. By evaluating expressions for each point of time, the interpretation extends to state expressions, which denote functions of time. A constant a or variable x is hereby interpreted as the function with constant value  $\mathcal{I}(a)$  or  $\mathcal{V}(x)$ .

An observation interval (or interval for short) is a closed and bounded interval  $[b,e] \subset [0,\infty)$ . For given interval [b,e], the duration  $\int P$  of a state assertion P denotes the real number

$$\int_{b}^{e} \chi_{P}(t) dt$$

where

$$\chi_P(t) = \begin{cases} 1 & \text{for} \quad \mathcal{I}(P)(t) = tt \\ 0 & \text{for} \quad \mathcal{I}(P)(t) = ff \end{cases}$$

which is the measure of the set of points in [b,e] where the interpretation of P has value tt. It is assumed that all state assertions denote integrable functions of time. The interpretation then extends to duration terms and duration formulas on each interval: the interpretation of duration terms and atomic duration formulas is defined on each interval [b,e] by evaluating expressions using the values of subterms on the same interval. The formulas true and false as well as composite duration formulas  $\neg \mathcal{D}$ ,  $\mathcal{D}_1 \vee \mathcal{D}_2$  and  $(\forall x)\mathcal{D}$  are interpreted on each interval [b,e] in the same way as usual logical formulas in predicate logic, cf. [11].

The interpretation of a "chop" formula  $\mathcal{D}_1; \mathcal{D}_2$  on an interval [b,e] use interpretations of the subformulas  $\mathcal{D}_1$  and  $\mathcal{D}_2$  on subintervals of [b,e]. It has the value tt iff a "chop" point m ( $b \leq m \leq e$ ) can be found such that  $\mathcal{D}_1$  is tt on [b,m] and  $\mathcal{D}_2$  is tt on [m,e].

Validity. A duration formula  $\mathcal{D}$  holds on the interval [b,e] in the interpretation  $\mathcal{I}$  iff  $\mathcal{D}$  has value tt on [b,e] for any valuation  $\mathcal{V}$  for  $\mathcal{I}$ .

The formula  $\mathcal{D}$  holds from start for the interpretation  $\mathcal{I}$  iff it holds on any interval of the form [0,T] for the interpretation  $\mathcal{I}$ .

A duration formula  $\mathcal{D}$  is valid (a tautology) iff it holds for every interval [b,e] in any interpretation  $\mathcal{I}$ . (Note that the validity of a chop formula  $\mathcal{D}_1;\mathcal{D}_2$  on an interval

[b,e] may depend on different chop points m for different interpretations.)

It is sufficient for a formula to be valid that it holds from start for every interpretation  $\mathcal I$  (this uses that shifting all functions in an interpretation  $\mathcal I$  a fixed amount of time b yields another interpretation  $\mathcal I'$ , such that  $\mathcal D$  holds on [b,e] for  $\mathcal I$  exactly when  $\mathcal D$  holds on [0,e-b] for  $\mathcal I'$ ).

Finite Variability. Interpretation of states has been confined to integrable functions in order to make the concept of duration well defined. In order to have a well-founded induction, we require that interpretation of any state assertion P has finite variability: any interval [b,e] can be divided into finitely many subintervals with  $\mathcal{I}(P)$  constant on each open subinterval.

# C. Specifications and Refinement

A specification for a system is a duration formula  $\mathcal{D}$ . An interpretation  $\mathcal{I}$  is said to satisfy the specification if  $\mathcal{D}$  holds from start for  $\mathcal{I}$ . For specifications  $\mathcal{D}_1$  and  $\mathcal{D}_2$  we say, that  $\mathcal{D}_2$  is a refinement of  $\mathcal{D}_1$  if any interpretation satisfying  $\mathcal{D}_2$  also satisfy  $\mathcal{D}_1$ . It follows that  $\mathcal{D}_2$  is a refinement of  $\mathcal{D}_1$  if the duration formula

$$\mathcal{D}_2 \Rightarrow \mathcal{D}_1$$

is valid.

### D. Deductions

A primary goal of using mathematical modeling is the ability to *calculate* properties of the model. The calculations for our notation are *deductions*, verifying that the validity of some formulas implies the validity of others.

It is a goal for the work on duration calculus to formalize deductions such that verification is done by calculations without any reference to a semantical model. The work has not yet reached that stage, but a number of useful axioms and deduction rules have been found. They are listed in the Appendix at the end of the paper. It has been proved (cf. [14]) that this formalization of the duration logic is a relative complete extension of real-valued interval temporal logic.

Most verifications for a real-time system consist of case analysis for a moderate number of cases. The individual cases have deductions that are mostly simple calculations. We give manually developed deduction outlines by necessity. The calculations, however, are simple and stereotypic, so there is reasonable hope for assistance from mechanical deduction asistants.

### E. Abbreviations

We use standard abbreviations  $\land$ ,  $\Rightarrow$ ,  $\Leftrightarrow$ ,  $\exists$ , and we introduce abbreviations for commonly used duration formulas, with a state assertion P, duration formulas  $\mathcal{D}$ ,  $\mathcal{D}_1$ , and  $\mathcal{D}_2$ , and a positive time constant t as shown in Table I. The abbreviations have the following semantics:

TABLE I ABBREVIATIONS

| Abbreviation                                          | Formula                                                                                                                            | Legend                                               |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| []                                                    | $\ell = 0$                                                                                                                         | Point                                                |

| $\lceil P \rceil$                                     | $(fP=\ell) \wedge (\ell>0)$                                                                                                        | Almost everywhere P                                  |

| $\diamondsuit\mathcal{D}$                             | $true; \mathcal{D}; true$                                                                                                          | Somewhere $\mathcal{D}$                              |

| $\square \mathcal{D}$                                 | $\neg(\diamondsuit(\neg\mathcal{D}))$                                                                                              | Always $\mathcal{D}$                                 |

| $\mathcal{D}_1 \to \mathcal{D}_2$                     | $ \begin{array}{c} (\mathcal{D}_1; true) \Rightarrow \\ (\mathcal{D}_1 \lor \\ (\mathcal{D}_1; \mathcal{D}_2; true)) \end{array} $ | $\mathcal{D}_2$ follows $\mathcal{D}_1$              |

| $\mathcal{D}_1 \sim t \rightsquigarrow \mathcal{D}_2$ | $(\mathcal{D}_1; true) \Rightarrow \\ ((\ell \le t) \lor \\ ((\ell \le t); \mathcal{D}_2))$                                        | $\mathcal{D}_1$ leads to $\mathcal{D}_2$ in time $t$ |

$\square \mathcal{D}$  holds on [b,e] if  $\mathcal{D}$  holds on any subinterval of [b,e]

$\mathcal{D}_1 \to \mathcal{D}_2$  holds on an interval with  $\mathcal{D}_1$  holding on an initial subinterval if  $\mathcal{D}_2$  holds on some subinterval from the point (if any) where  $\mathcal{D}_1$  ceases to hold

$\mathcal{D}_1 \sim t \leadsto \mathcal{D}_2$  holds on an interval with  $\mathcal{D}_1$  holding on an initial subinterval if  $\mathcal{D}_2$  starts holding within time t.

The following rules of precedence are used:

first:  $\neg$ ,  $\square$ ,  $\diamondsuit$  second:  $\lor$ ,  $\land$ , ; third:  $\Rightarrow$ ,  $\rightarrow$ ,  $\sim$   $t \rightsquigarrow$

The logical operators are overloaded: they are used for state assertions as well as duration formulas, but the meaning can be inferred from the type of the operands, e.g., " $\vee$ " denotes disjunction for state assertions in " $\lceil P_1 \vee P_2 \rceil$ " and disjunction for duration formulas in " $\lceil P_1 \rceil \vee \lceil P_2 \rceil$ ."

## III. A GAS BURNER SYSTEM

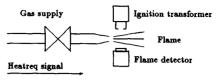

Our example is a simplified version of a computer controlled (on-off) gas burner described in [45]. This is a safety-critical system as an accident may occur if an excesive amount of unburned gas leaks to the environment. Small gas leaks cannot be avoided during ignition. A burning flame may also be blown out causing some gas to leak before the failure is detected. The gas burner is controlled by a thermostat and the gas is ignited by an ignition transformer, cf. Fig. 1. The informal requirements are as follows:

- For safety, gas must never leak for more than 4 s<sup>1</sup> in any period of 30 s at most.

- Heat request off shall result in the flame being off after 60 s.

- 3) Heat request shall after 60 s result in gas burning unless an ignite or flame failure has occurred. An ignite failure

Fig. 1. Gas burner

happens when gas does not ignite after 0.5 s. The flame fails if it disappears while gas is supplied.

The same timing constant has been used in 2) and 3) in order to allow a simple design.

### IV. SYSTEM MODEL AND REQUIREMENTS

In order to formalize the requirements to the gas burner we introduce the following Boolean valued states:

They express the physical state of the thermostat, the flame, the gas supply, and the ignition transformer as depicted in Fig. 1. The informal requirements for the gas burner can then be formalized using duration formulas on the system model.

1) For safety, gas must never leak for more than 4 s in any period of at most 30 s

$$Req_1 \stackrel{\frown}{=} \ell \le 30 \Rightarrow \int (Gas \land \neg Flame) \le 4$$

This is a critical duration constraint.

2) Heat request off shall result in the flame being off after 60 s

$$Req_2 = \lceil \neg Heatreg \rceil \Rightarrow (\lceil \rceil \sim 60 \rightsquigarrow \lceil \neg Flame \rceil)$$

This is a guarded progress constraint. The guard is  $\lceil \neg Heatreq \rceil$  and the progress is from an initial point  $\lceil \rceil$  to  $\lceil \neg Flame \rceil$  within 60 s.

Heat request shall, after 60 s, result in gas burning, unless an ignite or flame failure has occurred

$$\begin{split} Req_3 & \cong \lceil Heatreq \rceil \Rightarrow \\ & (\lceil \rceil \sim 60 \leadsto \lceil Flame \rceil) \\ & \lor \diamondsuit IgniteFail \lor \diamondsuit FlameFail \end{split}$$

An ignite failure happens when gas does not ignite within 0.5 s:

$$IgniteFail \stackrel{\frown}{=} \neg (\lceil Gas \land Ignition \rceil \Rightarrow (\lceil \rceil \sim 0.5 \leadsto \lceil Flame \rceil))$$

The flame fails if it disappears while gas is supplied

$$FlameFail \triangleq \\ \neg (\lceil Gas \rceil \Rightarrow \neg \lozenge (\lceil Flame \rceil; \lceil \neg Flame \rceil))$$

A formula  $\neg \diamondsuit (\lceil P \rceil; \lceil \neg P \rceil)$  means stability of P: P cannot change to  $\neg P$ .

<sup>1</sup> We use seconds as the time unit.

The total system requirements is the conjunction of the critical duration constraint  $Req_1$  and the guarded progress constraints  $Req_2$  and  $Req_3$

$$RegAll \cong Reg_1 \wedge Reg_2 \wedge Reg_3$$

The requirements should hold for any interval

$$Reg \cong \square RegAll$$

### V. CONTROL MODEL AND CONTROL LAW

A control law expresses a top-level design of the system. It consists of a control function and assumptions about the behavior of the environment. The control function defines interaction between the control system and the environment. The assumptions define preconditions for the control law. In order to formalize the control law, the control model is formed. It is the system model with an additional state P that records the phase of operation of the controller.

### A. Gas Burner Phases

We use a simple version of the control law in [45] (especially simplified with respect to error recovery) for the gas burner. It has the following *phases*:

Idle: Awaits heat request; no gas and ignition. It enters the Purge phase on heat request.

Purge: Pauses for 30 s, and then Ignite1 is entered. Ignite1: Starts ignition and gas supply; enters the Ig-

Ignitel: Starts ignition and gas supply; enters the Ignite2 phase after 1 s.

Ignite2: Monitors the flame and enters the Burn phase if flame is sensed within 1 s.

Burn: Ignition is switched off, but gas is still supplied.

The Burn phase is stable until heat request goes off. The Idle phase is then entered and

the gas is turned off.

We use the simple error recovery procedure of returning to Idle. If a flame is not sensed within 1 s in Ignite2 (ignite failure), or if the flame disappears during the Burn phase (flame failure), then the Idle phase is entered and the gas is turned off. The 30 s Purge pause ensures a sufficient distance between periods with leaking gas.

# B. Control Automaton

We describe the possible phase transitions by means of a finite state *automaton* with states corresponding to the phases. The automaton is shown in Fig. 2. The automaton is defined in the control model using the state P giving the current phase of the system.

Its value domain is the finite set of phase names, and the following state assertions describe the individual phases

Fig. 2. Phase transitions for the gas burner.

The automaton is defined by untimed progresss constraints

$$Phases \cong Init \wedge Trans$$

where Init expresses that the automaton starts in the Idle phase

$$Init \stackrel{\widehat{=}}{=} \lceil \rceil \rightarrow \lceil Idle \rceil$$

and Trans defines the phase transitions

$$Trans \widehat{=} \square( \\ (\lceil Idle \rceil \rightarrow \lceil Purge \rceil) \\ \land (\lceil Purge \rceil \rightarrow \lceil Ignite1 \rceil) \\ \land (\lceil Ignite1 \rceil \rightarrow \lceil Ignite2 \rceil) \\ \land (\lceil Ignite2 \rceil \rightarrow (\lceil Burn \rceil \lor \lceil Idle \rceil)) \\ \land (\lceil Burn \rceil \rightarrow \lceil Idle \rceil))$$

i.e. Idle is followed by Purge, Purge is followed by Ignitel, etc., cf. Fig. 2.

Phase Requirements. The predicate PhaseReq specifies the monitoring and control of system states for each phase

$$PhaseReq \triangleq \Box (IdleReq \land PurgeReq \land Ignite1Req \land Ignite2Req \land BurnReq)$$

In the formulas, the constant  $\varepsilon_1$  denotes an upper bound on progress. Any move will be performed within time  $\varepsilon_1$ . The constant  $\varepsilon_2$  gives, on the other hand, a lower bound on stability. The system will not move before time  $\varepsilon_2$ . We assume that  $0 < \varepsilon_2 < \varepsilon_1$ .

The Idle phase is stable at least  $\varepsilon_2$  beyond  $\neg Heatreq$ . The Idle phase is left before Heatreq has lasted  $\varepsilon_1$ . During the Idle phase Gas and Ignition are turned off within  $\varepsilon_1$

$$\begin{split} IdleReq & \; \widehat{=} \\ & \; (\lceil \neg Heatreq \rceil; \ell \leq \varepsilon_2 \Rightarrow \neg \diamondsuit (\lceil \mathtt{Idle} \rceil; \lceil \neg \mathtt{Idle} \rceil)) \\ & \; \wedge (\lceil \mathtt{Idle} \rceil \wedge \lceil Heatreq \rceil \Rightarrow \ell \leq \varepsilon_1) \\ & \; \wedge (\lceil \mathtt{Idle} \rceil \Rightarrow (\lceil \rceil \sim \varepsilon_1 \leadsto \lceil \neg Gas \wedge \neg Ignition \rceil)) \end{split}$$

Notice that  $\ell \leq \varepsilon_1$  in the second clause can be rewritten to the progress constraint

$$\lceil \rceil \sim \varepsilon_1 \leadsto false$$

In conjunction with the untimed phase constraint, it will give a next phase within  $\varepsilon_1$ .

A completed Purge phase lasts approximately 30 s, and which should hold on any interval Gas and Ignition are off within  $\varepsilon_1$

PurgeReg = $(\lceil \neg \text{Purge} \rceil; \ell \leq 30 \Rightarrow \neg \lozenge (\lceil \text{Purge} \rceil; \lceil \neg \text{Purge} \rceil))$  $\land ([Purge] \Rightarrow \ell < 30 + \varepsilon_1)$  $\land ([Purge] \Rightarrow ([] \sim \varepsilon_1 \leadsto [\neg Gas \land \neg Ignition]))$

The first clause denotes an unconditional stability of Purge for at least 30 s.

A completed Ignite1 phase lasts approximately 1 s, and Gas and Ignition are on within  $\varepsilon_1$

Ignite1Reg = $(\lceil \neg \text{Ignite1} \rceil; \ell < 1 \Rightarrow \neg \lozenge (\lceil \text{Ignite1} \rceil; \lceil \neg \text{Ignite1} \rceil))$  $\land (\lceil \text{Ignite1} \rceil \Rightarrow \ell \leq 1 + \varepsilon_1)$  $\land (\lceil \text{Ignite1} \rceil \Rightarrow (\lceil \rceil \sim \varepsilon_1 \leadsto \lceil Gas \land Ignition \rceil))$

The Ignite2 phase does not enter Idle after less than 1 s and it does not enter Burn after less than  $\varepsilon_2$  of Flame. It lasts at most  $1 + \varepsilon_1$  and it is left within  $\varepsilon_1$  if the Flame comes on. The Ignite2 phase maintains Gas and Ignition

Iqnite2Req = $(\lceil \neg Ignite2 \rceil; \ell \leq 1 \Rightarrow \neg \Diamond (\lceil Ignite2 \rangle; \lceil Idle \rceil))$  $\land (\lceil \neg Flame \rceil; \ell \leq \varepsilon_2 \Rightarrow \neg \lozenge (\lceil \neg Burn \rceil; \lceil Burn \rceil))$  $\land (\lceil \text{Ignite2} \rceil \Rightarrow \ell \leq 1 + \varepsilon_1)$  $\land (\lceil \text{Ignite2} \rceil \land \lceil Flame \rceil \Rightarrow \ell \leq \varepsilon_1)$  $\land ([Ignite2] \Rightarrow [Gas \land Ignition])$

Note, that Trans implies that Burn can only be entered from Ignite2. Hence [¬Burn] in the second clause could be replaced by [Ignite2].

The Burn phase persists  $\varepsilon_2$  beyond Heatreg and Flame. It is left within  $\varepsilon_1$  if Heatreg or Flame goes off. During the Burn phase Gas is maintained, but Ignition is switched off within  $\varepsilon_1$

$$\begin{split} BurnReq & \widehat{=} \\ & (\lceil Heatreq \wedge Flame \rceil; \ell \leq \varepsilon_2 \\ & \Rightarrow \neg \diamondsuit \left( \lceil \texttt{Burn} \rceil; \lceil \neg \texttt{Burn} \rceil \right) \right) \\ & \wedge \left( \lceil \texttt{Burn} \rceil \wedge \lceil \neg Heatreq \vee \neg Flame \rceil \Rightarrow \ell \leq \varepsilon_1 \right) \\ & \wedge \left( \lceil \texttt{Burn} \rceil \Rightarrow \lceil Gas \rceil \right) \\ & \wedge \left( \lceil \texttt{Burn} \rceil \Rightarrow \left( \lceil \rceil \sim \varepsilon_1 \leadsto \lceil \neg Ignition \rceil \right) \right) \end{split}$$

### C. Assumptions

The control law also needs assumptions about the physical processes in the system. For the gas burner we have the following assumptions:

1) No gas results in no flame within 0.1 s.

$$Asm_1 \triangleq \lceil \neg Gas \rceil \Rightarrow (\lceil \rceil \sim 0.1 \leadsto \lceil \neg Flame \rceil)$$

2) Gas does not ignite when the ignition transformer is not operating.

$$Asm_2 \stackrel{\frown}{=} \\ \lceil \neg Ignition \rceil \Rightarrow \neg \lozenge (\lceil \neg Flame \rceil; \lceil Flame \rceil)$$

$$Asm \stackrel{\frown}{=} \Box \left( Asm_1 \wedge Asm_2 \right)$$

### VI. CORRECTNESS OF CONTROL LAW

A control law is *correct* if it implements the requirements under the given assumptions. The formalized requirements, assumptions and control function allow correctness to be expressed formally as the implication

$$Asm \land Phases \land PhaseReq \Rightarrow Req$$

We have  $Phases = Init \wedge Trans$ , where Init decomposes into [] or [Idle]: true. It is easy to see that requirements hold for the point interval, thus  $[] \Rightarrow Reg$ . For [Idle]: true. we use that the automaton returns to Idle, such that this case is subsumed by

$$Asm \land Trans \land PhaseReq \Rightarrow Req$$

We now consider separate cases for each requirement:

- 1)  $Asm \wedge Trans \wedge PhaseReq \Rightarrow Req_1$

- 2)  $Asm \wedge Trans \wedge PhaseReq \Rightarrow Req_2$

- 3)  $Asm \wedge Trans \wedge PhaseReq \Rightarrow Req_3$

### A. Verification of Req<sub>1</sub>

We first use PhaseReq to estimate the duration of the critical state

$$Leak \cong Gas \land \neg Flame$$

for each phase.

We define Limits to be the following conjunction of estimates

$$\begin{split} Limits & \widehat{=} \\ & (\lceil \mathtt{Idle} \rceil \Rightarrow \lceil Gas \leq \varepsilon_1) \\ & \wedge (\lceil \mathtt{Purge} \rceil \Rightarrow \lceil Gas \leq \varepsilon_1) \\ & \wedge (\lceil \mathtt{Ignite1} \rceil \Rightarrow \ell \leq 1 + \varepsilon_1) \\ & \wedge (\lceil \mathtt{Ignite2} \rceil \Rightarrow \ell \leq 1 + \varepsilon_1) \\ & \wedge (\lceil \mathtt{Burn} \rceil \Rightarrow \lceil \neg Flame \leq 2 \cdot \varepsilon_1) \end{split}$$

The deduction of

$$Asm \land Trans \land PhaseReq \Rightarrow Limits$$

can be split into simple cases for each conjunct. We take the first one in great detail

$$IdleReq \land \lceil Idle \rceil$$

$$\Rightarrow \lceil \rceil \sim \varepsilon_1 \leadsto \lceil \neg Gas \land \neg Ignition \rceil$$

$$\Rightarrow \lceil \rceil \sim \varepsilon_1 \leadsto \lceil \neg Gas \rceil$$

$$\Rightarrow \lceil Gas \le \varepsilon_1 \lor (\lceil Gas \le \varepsilon_1; \lceil Gas = 0) \rceil$$

$$\Rightarrow \lceil Gas \le \varepsilon_1 \lor \lceil Gas \le \varepsilon_1 + 0 \rceil$$

and omit the deductions for the next three cases. The last case is

$$\Box BurnReq \wedge \Box Asm_2 \wedge \lceil Burn \rceil$$

$$\Rightarrow \Box (\lceil \neg Flame \rceil \Rightarrow \ell \leq \varepsilon_1) \wedge \Box Asm_2$$

$$\wedge (\lceil \rceil \sim \varepsilon_1 \leadsto \lceil \neg Ignition \rceil)$$

$$\Rightarrow \Box (\lceil \neg Flame \rceil \Rightarrow \ell \leq \varepsilon_1) \wedge$$

$$(\lceil \rceil \sim \varepsilon_1 \leadsto \neg \diamondsuit (\lceil \neg Flame \rceil; \lceil Flame \rceil))$$

$$\Rightarrow \ell \leq \varepsilon_1 \vee (\ell \leq \varepsilon_1; \lceil Flame \rceil)$$

$$\vee (\ell \leq \varepsilon_1; (\lceil \neg Flame \rceil \wedge \ell \leq \varepsilon_1))$$

$$\vee (\ell \leq \varepsilon_1; \lceil Flame \rceil \wedge \ell \leq \varepsilon_1))$$

$$\Rightarrow \lceil \neg Flame \rceil \wedge \ell \leq \varepsilon_1))$$

$$\Rightarrow \lceil \neg Flame \rceil \wedge \ell \leq \varepsilon_1)$$

where we have used

$$\neg \diamondsuit (\lceil \neg Flame \rceil; \lceil Flame \rceil)$$

$$\Rightarrow \lceil Flame \rceil \lor \lceil \neg Flame \rceil \lor (\lceil Flame \rceil; \lceil \neg Flame \rceil)$$

The second step in the verification is also a case analysis. The cases are defined by the initial phase of an arbitrary interval. The premise is

$$Pre_1 \stackrel{\frown}{=} Trans \wedge \square Limits \wedge \ell \leq 30$$

in

T

- 1)  $Pre_1 \wedge (\lceil Idle \rceil; true) \Rightarrow \int Leak \leq 2 \cdot \varepsilon_1$

- 2)  $Pre_1 \wedge (\lceil Purge \rceil; true) \Rightarrow \int Leak \leq 2 + 7 \cdot \varepsilon_1$

- 3)  $Pre_1 \wedge (\lceil \text{Ignite1} \rceil; true) \Rightarrow \int Leak \leq 2 + 6 \cdot \varepsilon_1$

- 4)  $Pre_1 \wedge (\lceil \text{Ignite2} \rceil; true) \Rightarrow \int Leak \leq 1 + 5 \cdot \varepsilon_1$

- 5)  $Pre_1 \wedge ([Burn]; true) \Rightarrow \int Leak \leq 4 \cdot \varepsilon_1$

$Pre_1 \wedge (\lceil Idle \rceil; true)$

$\Rightarrow Pre_1 \land$

The calculations follow a pattern, where previous results are used

$$\begin{split} &(\lceil \mathtt{Idle} \rceil) \\ & \vee (\lceil \mathtt{Idle} \rceil; ((\lceil \mathtt{Purge} \rceil; true) \land \ell \leq 30))) \\ \Rightarrow & Limits \land (\lceil \mathtt{Idle} \rceil \lor (\lceil \mathtt{Idle} \rceil; \lceil \mathtt{Purge} \rceil)) \\ \Rightarrow & \int Gas \leq \varepsilon_1 \lor (\int Gas \leq \varepsilon_1; \int Gas \leq \varepsilon_1) \\ \Rightarrow & \int Gas \leq 2 \cdot \varepsilon_1 \\ & Pre_1 \land (\lceil \mathtt{Burn} \rceil; true) \\ \Rightarrow & Pre_1 \land (\lceil \mathtt{Burn} \rceil \lor (\lceil \mathtt{Burn} \rceil; \lceil \mathtt{Idle} \rceil; true)) \\ \Rightarrow & Limits \\ & \land (\lceil \mathtt{Burn} \rceil \lor (\lceil \mathtt{Burn} \rceil; \int Leak \leq 2 \cdot \varepsilon_1)) \\ \Rightarrow & \int Leak \leq 4 \cdot \varepsilon_1 \end{split}$$

The cases for Ignite1 and Ignite2 are similar, and so is

$$\begin{split} & Pre_1 \wedge (\lceil \texttt{Purge} \rceil; true) \\ \Rightarrow & Pre_1 \wedge (\lceil \texttt{Purge} \rceil \\ & \vee (\lceil \texttt{Purge} \rceil; \lceil \texttt{Ignite1} \rceil; true)) \\ \Rightarrow & \int Leak \leq 2 + 7 \cdot \varepsilon_1 \end{split}$$

The case analysis shows that an interval beginning in a Purge phase is most critical, and that  $Req_1$  will be satisfied as long as  $\varepsilon_1 \leq 2/7$ .

### B. Verification of Req2

We start by proving that  $\neg Heatreq$  maintains the Idle phase

$$\begin{split} IdleReq & \land \lceil \neg Heatreq \rceil \land (\lceil \texttt{Idle} \rceil; true) \\ \Rightarrow & \neg \diamondsuit (\lceil Idle \rceil; \lceil \neg Idle \rceil) \\ & \land (\lceil Idle \rceil \lor \diamondsuit (\lceil Idle \rceil; \lceil \neg Idle \rceil)) \\ \Rightarrow & \lceil \texttt{Idle} \rceil \end{split}$$

The deduction of  $Req_2$  is a case analysis, depending on the initial phase of the interval. The premise  $Pre_2$  is defined

$$Pre_2 \cong \lceil \neg Heatreq \rceil \land \square Asm_1 \land \square Trans \land PhaseReq$$

and the cases are

- 1)  $Pre_2 \wedge (\lceil Idle \rceil; true) \wedge \ell > 2$  $\Rightarrow (\ell \leq 0.1 + \varepsilon_1; \lceil \neg Flame \rceil)$

- 2)  $Pre_2 \wedge (\lceil Burn \rceil; true) \wedge \ell > 3$  $\Rightarrow (\ell \leq 0.1 + 2 \cdot \varepsilon_1; \lceil \neg Flame \rceil)$

- 3)  $Pre_2 \wedge (\lceil \text{Ignite2} \rceil; true) \wedge \ell > 5$  $\Rightarrow (\ell < 1.1 + 3 \cdot \varepsilon_1; \lceil \neg Flame \rceil)$

- 4)  $Pre_2 \wedge (\lceil \text{Ignite1} \rceil; true) \wedge \ell > 7$  $\Rightarrow (\ell < 2.1 + 4 \cdot \varepsilon_1; \lceil \neg Flame \rceil)$

- 5)  $Pre_2 \wedge (\lceil Purge \rceil; true) \wedge \ell > 38$  $\Rightarrow (\ell \leq 32.1 + 5 \cdot \varepsilon_1; \lceil \neg Flame \rceil)$

The individual calculations are of the usual form:

$$\begin{aligned} & Pre_2 \wedge (\lceil \mathtt{Idle} \rceil; true) \wedge \ell > 2 \\ \Rightarrow & \Box (Asm_1 \wedge IdleReq) \wedge \lceil \mathtt{Idle} \rceil \wedge \ell > 2 \\ \Rightarrow & \Box Asm_1 \wedge (\ell \leq \varepsilon_1; \lceil \neg Gas \rceil) \\ \Rightarrow & \ell < \varepsilon_1 + 0.1; \lceil \neg Flame \rceil \end{aligned}$$

where we have used that  $\neg Heatreq$  maintains Idle. The other cases are similar and the deductions are omitted.

# C. Verification of Req<sub>3</sub>

Assuming  $\varepsilon_1 < 0.5$ , which is compatible with  $\varepsilon_1 \leq 2/7$ , we deduce that Ignite2 only leads to Idle in case of an IgniteFail.

and that a Burn phase is preceded by Flame. This is shown by contradiction

We also deduce that Burn maintains the Flame unless there is a FlameFail

$$BurnReq \land (\lceil Flame \land Gas \rceil; \lceil Burn \rceil)$$

$$\Rightarrow \lceil Gas \rceil \land (\lceil Flame \rceil; true)$$

$$\Rightarrow \lceil Flame \rceil$$

$$\lor (\lceil Gas \rceil \land \diamondsuit (\lceil Flame \rceil; \lceil \neg Flame \rceil))$$

$$\Rightarrow \lceil Flame \rceil \lor Flame Fail$$

and finally that Heatreq without FlameFail maintains a Burn phase with Flame

```

\Box (BurnReq \land \neg FlameFail) \land \lceil Heatreq \rceil \\ \land (\lceil Gas \land Flame \rceil; \lceil Burn \rceil; true) \\ \Rightarrow \Box (BurnReq \land \neg FlameFail) \land \lceil Heatreq \rceil \\ \land ((\lceil Gas \land Flame \rceil; \lceil Burn \rceil) \\ \lor (\lceil Gas \land Flame \rceil; \lceil Burn \rceil) \\ ; \lceil \neg Burn \rceil; true)) \\ \Rightarrow (\lceil Flame \rceil; \lceil Flame \land Burn \rceil) \\ \lor \diamondsuit (BurnReq \\ \land ((\lceil Burn \rceil \land \lceil Heatreq \land Flame \rceil) \\ ; \lceil \neg Burn \rceil)) \\ \Rightarrow (\lceil Flame \rceil; \lceil Flame \land Burn \rceil)

```

We can now proceed to the main deduction. This is also a case analysis, depending on the initial phase of the interval. We assume that  $\epsilon_1 \leq 1$ . The premise  $Pre_3$  is defined

$$Pre_3 \cong \lceil Heatreq \rceil \wedge Trans \wedge PhaseReq$$

$\wedge \square \neg IaniteFail \wedge \square \neg FlameFail$

and the cases are

1)

$$Pre_3 \wedge (\lceil \texttt{Ignite1} \rceil; true) \wedge \ell > 5$$

$\Rightarrow (\ell \leq 2 + 2 \cdot \varepsilon_1; \lceil Flame \rceil)$

2)  $Pre_3 \wedge (\lceil \texttt{Purge} \rceil; true) \wedge \ell > 36$

$\Rightarrow (\ell \leq 32 + 3 \cdot \varepsilon_1; \lceil Flame \rceil)$

3)  $Pre_3 \wedge (\lceil \texttt{Idle} \rceil; true) \wedge \ell > 37$

$\Rightarrow (\ell \leq 32 + 4 \cdot \varepsilon_1; \lceil Flame \rceil)$

4)  $Pre_3 \wedge (\lceil \texttt{Burn} \rceil; true) \wedge \ell > 38$

$\Rightarrow (\ell \leq 32 + 5 \cdot \varepsilon_1; \lceil Flame \rceil)$

5)  $Pre_3 \wedge (\lceil \texttt{Ignite2} \rceil; true) \wedge \ell > 40$

$\Rightarrow (\ell \leq 33 + 6 \cdot \varepsilon_1; \lceil Flame \rceil)$

The individual calculations are

$$\begin{split} Pre_3 \wedge (\lceil \texttt{Ignite1} \rceil; true) \wedge \ell > 5 \\ \Rightarrow Pre_3 \wedge ((\ell \leq 1 + \varepsilon_1 \wedge \lceil \texttt{Ignite1} \rceil) \\ & ; (\ell \leq 1 + \varepsilon_1 \wedge \lceil \texttt{Ignite2} \rceil) \\ & ; (\lceil \texttt{Burn} \rceil \vee \lceil \texttt{Idle} \rceil); true) \\ \Rightarrow Pre_3 \wedge (\\ & (\ell \leq 2 + 2 \cdot \varepsilon_1 \wedge (true; \lceil Flame \wedge Gas \rceil)) \\ & ; \lceil \texttt{Burn} \rceil; true) \\ \Rightarrow \ell < 2 + 2 \cdot \varepsilon_1; \lceil Flame \rceil \end{split}$$

where we have used the above results about Ignite2 and Burn.

The second case can, as usual, be reduced using the previous result:

$$\begin{split} & Pre_3 \wedge (\lceil \texttt{Purge} \rceil; true) \wedge \ell > 36 \\ \Rightarrow & Pre_3 \\ & \wedge (\ell \leq 30 + \varepsilon_1; ((\lceil \texttt{Ignite1} \rceil; true) \wedge \ell > 5)) \\ \Rightarrow & \ell \leq 32 + 3 \cdot \varepsilon_1; \lceil Flame \rceil \end{split}$$

and the third follows the pattern

$$Pre_{3} \wedge (\lceil \mathtt{Idle} \rceil; true) \wedge \ell > 37$$

$$\Rightarrow \Box IdleReq \wedge \ell > 37$$

$$\wedge (\lceil \mathtt{Idle} \wedge Heatreq \rceil; \ell \leq 32 + 3 \cdot \varepsilon_{1}$$

$$: \lceil Flame \rceil)$$

$$\Rightarrow \ell < 32 + 4 \cdot \varepsilon_{1}; \lceil Flame \rceil)$$

The last cases have a surprise, because the observation may start just after a FlameFail in the Burn phase

$$\begin{split} &Pre_3 \wedge (\lceil \mathtt{Burn} \rceil; true) \wedge \ell > 38 \\ \Rightarrow & Pre_3 \wedge (\lceil \mathtt{Burn} \rceil; true) \wedge \ell > 38 \\ & \wedge ((\lceil \neg Flame \rceil; true) \vee (\lceil Flame \rceil; true)) \\ \Rightarrow & (Pre_3 \wedge (\lceil \mathtt{Burn} \rceil; true) \\ & \wedge (\lceil \neg Flame \rceil; true)) \vee \lceil Flame \rceil \\ \Rightarrow & (Pre_3 \wedge \ell > 38 \\ & \wedge (\ell \leq \varepsilon_1; \lceil \mathtt{Idle} \rceil; true)) \vee \lceil Flame \rceil \\ \Rightarrow & \ell \leq 32 + 5 \cdot \varepsilon_1; \lceil Flame \rceil \end{split}$$

and

$$\begin{split} & Pre_3 \wedge (\lceil \texttt{Ignite2} \rceil; true) \wedge \ell > 40 \\ \Rightarrow & Pre_3 \wedge \ell > 40 \wedge (\ell \leq 1 + \varepsilon_1; \lceil \texttt{Burn} \rceil; true) \\ \Rightarrow & \ell \leq 33 + 6 \cdot \varepsilon_1; \lceil Flame \rceil \end{split}$$

In summary: the control law specifies a correct design if the constants  $\varepsilon_1$  and  $\varepsilon_2$  are chosen such that

$$\varepsilon_1 < 2/7$$

and  $0 < \varepsilon_2 < \varepsilon_1$

Notice that the latency  $\varepsilon_2$  can be arbitrarily small.

The control law can almost directly be used to implement the system with a processor that accesses sensor and actuator states. The progress constraints map to assignments, whereas stability constraints map to delays, either unconditionally or in a sensor-reading loop.

There is, hovewer, an element of parallel processing in sensor readings. This indicates that a further decomposition of the design is useful.

### VII. ARCHITECTURE

An architecture specifies a collection of selected components together with an interconnection scheme. A component is either a subsystem or an elementary component: a program, a sensor, an actuator or a timer. A program implements a state machine that takes the system through specified phases. In the general case, state transitions may depend on values computed from data collected in previous phases. A sensor monitors a physical system state, and it is ready to communicate the

.....

TABLE II

GAS BURNER ARCHITECTURE

| Component              | Alphabet          | Private States                                                                                          |

|------------------------|-------------------|---------------------------------------------------------------------------------------------------------|

| Heat request sensor HS | {HeatOn. HeatOff} | Ref <sub>HS</sub> : PaHS<br>Heatreq: Bool                                                               |

| Flame sensor<br>FS     | {FlOn. FlOff}     | $egin{aligned} \mathtt{Ref}_{\mathbf{FS}} : P lpha \mathtt{FS} \ Flame : Bool \end{aligned}$            |

| Gas actuator<br>GA     | {GasOn. GasOff}   | $egin{aligned} 	exttt{Ref}_{	exttt{GA}} : 	exttt{P} lpha 	exttt{GA} \ Gas : 	exttt{Bool} \end{aligned}$ |

| Ignition actuator IA   | {IgnOn. IgnOff}   | $egin{aligned} \mathtt{Ref_{IA}} : P lpha \mathtt{IA} \ Ignition : \mathbf{Bool} \end{aligned}$         |

| l s timer T1           | {Set1. Out1}      | $\mathtt{Ref}_{\mathtt{T1}}: \mathtt{P}\alpha\mathtt{T1}$                                               |

| 30 s timer <b>T</b> 30 | {Set30. Out30}    | $Ref_{T30} : PaT30$                                                                                     |

| Program P              | Event             | $\mathtt{Ref}_{\mathtt{P}}: \mathtt{P} \alpha \mathtt{P}$                                               |

state value to a program when requested to do so. An actuator controls a physical system state, and it is ready to change the state to a communicated value from a program when so requested. A timer implements delays giving lower bounds on the duration of phases.

The interconnection scheme that we propose aims at a distributed system, where the components execute concurrently and synchronize through instantaneous, shared events. The synchronous communication paradigm is inspired by CSP [16].

The interconnection scheme uses a set of events, Event, called the system alphabet. Each component C synchronizes on a subset  $\alpha C \subseteq$  Event called the C-component alphabet.

Each component has a designated state  $Ref_{\mathbb{C}}$ , which records the subset of  $\alpha \mathbb{C}$  that is refused at a given time. Events that are not in  $\alpha \mathbb{C}$  are never refused.

A scheduler observes the refusal states for all components and allows the components to move whenever no one refuses an event. Whenever such a move occurs, it is recorded in a history or trace of events

It is the only shared state in the architecture and it is only *read* by components. Refusal states are private for components, and the system states are distributed among sensors and actuators.

### A. Architecture of the Gas Burner

For the gas burner we use the architecture shown in Table II. In this case, where there is only one program component, system and program have the same alphabet

$$\mathtt{Event} = \alpha \mathtt{HS} \cup \alpha \mathtt{FS} \cup \alpha \mathtt{GA} \cup \alpha \mathtt{IA} \cup \alpha \mathtt{T1} \cup \alpha \mathtt{T30}$$

The events have the informal meaning: heat request on, heat request off, ..., set 30 s timer, expiration of 30 s timer.

We let e range over Event and s over Event\* in the following, and we denote the projection of tr on a component alphabet  $\alpha C$  by  $tr_C$

$$\mathsf{tr}_\mathtt{C} \mathrel{\widehat{=}} \mathsf{tr} \upharpoonright \alpha \mathtt{C}$$

# B. General Properties

Trace tr accumulates the history of events for the system, i.e., an event occurring at time t is appended to the previous value of tr. The trace is empty initially

$$Inittr = [] \rightarrow [tr = \langle \rangle]; true$$

and tr is an *increasing* function of time (in the prefix ordering of sequences of events)

$$TrIncr = [tr = s_1]; [tr = s_2] \Rightarrow [s_1 \leq s_2]$$

This constraint allows a finite set of events to happen at one time.

Event e is not appended to trace if it is refused by any component C

$$WfRef \; \widehat{=} \; \lceil \bigvee_{\mathtt{C} \in \mathtt{Comp}} \mathtt{e} \in \mathtt{Ref}_{\mathtt{C}} \rceil \Rightarrow \mathsf{stable} \, (\mathtt{tr} \, \upharpoonright \, \{\mathtt{e}\})$$

where Comp is the finite set of components and where

stable

$$(\operatorname{tr} \upharpoonright A) = \exists s : A^* \bullet [\operatorname{tr} \upharpoonright A = s]$$

expresses stability for the projection  ${\tt tr} \upharpoonright {\tt A}$  of the trace  ${\tt tr}$  on a subset  ${\tt A} \subseteq {\tt Event}.$

Constraints WfRef and TrIner allow a finite set of events to occur instantaneously and does not force anything to happen. The actual occurrence of events is controlled by a *Scheduler*.

The general properties of trace and refusals are collected in the formula

$$General \cong Inittr \wedge \Box (TrIncr \wedge WfRef)$$

# C. Scheduler

The scheduler is the synchronization agent for the distributed system

$$Scheduler \cong \square \ (TrOne \land TrStep \land Progress)$$

Progress is ensured by insisting that the the trace tr remains stable at most  $\delta_1$  when some event e is not refused by all components

$$Progress \, \widehat{=} \quad \text{ stable } (\mathtt{tr}) \wedge \lceil \bigwedge_{\mathtt{C} \in \mathtt{Comp}} \mathtt{e} \not \in \mathtt{Ref}_{\mathtt{C}} \rceil \Rightarrow \ell < \delta_1$$

It follows that if an event e is accepted by all components for time  $\delta_1$  then the trace becomes extended with some event (which may be different from e).

We shall not use true concurrency,<sup>2</sup> so we introduce special constraints that force events to happen one at a time and with a minimal distance  $\delta_2$

$$TrOne = \lceil tr = s_1 \rceil; \lceil tr = s_2 \rceil$$

$\Rightarrow \lceil \#s_2 \leq \#s_1 + 1 \rceil$

<sup>2</sup>If we allow true concurrency, the refusal shall distinguish between e.g., willingness to participate in each of two events and willingness to participate in both events simultaneously. This distinction is possible with a more complicated definition of the refusal.

and

$$TrStep \triangleq \lceil \texttt{tr} \neq \texttt{s}_1 \rceil; \lceil \texttt{tr} = \texttt{s}_1 \rceil; \lceil \texttt{tr} \neq \texttt{s}_1 \rceil$$

$$\Rightarrow \ell > \delta_2$$

where # denotes the length of a sequence. Consistency dictates, that  $\delta_2 < \delta_1$ .

### D. Program

In order to specify the program for the gas burner we introduce the following regular expression over the alphabet Event

where "pref" denotes the prefix closure operation on a regular expression.

The program is specified by a refusal constraint: the program refuses an event e if and only if the event does not extend the program trace  $tr_P$  (= tr) to a member of ptrace

$$Program = [e \in Ref_P] \Leftrightarrow [tr^{(e)} \notin ptrace]$$

It can be verified that trace tr always belongs to ptrace

$Scheduler \land General \land Program \Rightarrow PTrace$

where

$$Ptrace = \Box([] \lor [tr \in ptrace])$$

In order to express the phase in terms of the trace, we introduce the projection  $tr_{In} = tr \upharpoonright In$  of trace tr onto the subalphabet

In

$$\triangleq$$

{Fl0n, Fl0ff, Heat0n,

Heat0ff, Out1, Out30}

It is obvious that  $\mathtt{tr}_{\mathtt{In}}$  will have the projected property of Ptrace

$$PInTrace \triangleq \Box ( [ ] \lor [ tr_{In} \in inptrace ] )$$

where the regular expressions

$$\label{eq:continuous} \begin{split} &\text{incycle} = \texttt{HeatOn.Out30.Out1.} \\ & & (\texttt{FlOn.(HeatOff} + \texttt{FlOff}) + \texttt{Out1)} \\ & & \text{inptrace} = \texttt{pref(incycle*)} \end{split}$$

are the projections of cycle and ptrace on In.

The phases are now described by

$$\begin{split} &\text{Idle} \Leftrightarrow \text{tr}_{\text{In}} \in \text{incycle}^* \\ &\text{Purge} \Leftrightarrow \text{tr}_{\text{In}} \in \text{incycle}^*.\text{HeatOn} \\ &\text{Ignite1} \Leftrightarrow \text{tr}_{\text{In}} \in \text{incycle}^*.\text{HeatOn.Out30} \\ &\text{Ignite2} \Leftrightarrow \text{tr}_{\text{In}} \in \text{incycle}^*.\text{HeatOn.Out30.Out1} \\ &\text{Burn} \Leftrightarrow \text{tr}_{\text{In}} \in \text{incycle}^*.\text{HeatOn.Out30.Out1.FlOn} \end{split}$$

Fig. 3. Phase transitions and in-events.

It follows that the phase changes correspond to occurences of the in-event as shown in Fig. 3, i.e.,

$General \wedge Scheduler \wedge Program \Rightarrow Phases$

### E. Sensors

The heat request sensor (HS) is specified as a conjunction

$$HeatReqSensor \cong \Box(HSRef \wedge HSReady)$$

of a stability constraint: The HeatOn event is refused if Heatreq has been on for less than time  $\delta_2$  and the HeatOff event is refused if Heatreq has been off for less than time  $\delta_2$

$$\begin{split} HSRef & \; \widehat{=} \\ & \; (\lceil \neg Heatreq \rceil; \ell \leq \delta_2 \Rightarrow \lceil \text{HeatOn} \in \text{Ref}_{\text{HS}} \rceil) \\ & \; \land (\lceil Heatreq \rceil; \ell \leq \delta_2 \Rightarrow \lceil \text{HeatOff} \in \text{Ref}_{\text{HS}} \rceil) \end{split}$$

and a progress constraint: The HeatOn event is not refused when has Heatreq been on for time  $\delta_1$  and the HeatOff event is not refused when Heatreq has been off for time  $\delta_1$

$$\begin{split} HSReady & \widehat{=} \\ & (\lceil Heatreq \rceil \Rightarrow (\lceil \rceil \sim \delta_1 \leadsto \lceil \text{HeatOn} \not\in \text{Ref}_{\text{HS}} \rceil)) \\ & \wedge (\lceil \neg Heatreq \rceil \Rightarrow (\lceil \rceil \sim \delta_1 \leadsto \lceil \text{HeatOff} \not\in \text{Ref}_{\text{HS}} \rceil)) \end{split}$$

Flame sensor (FS ) has a similar specification

$$FlameSensor \cong \Box(FSRef \wedge FSReady)$$

where

$$FSRef = (\lceil \neg Flame \rceil; \ell \leq \delta_2 \Rightarrow \lceil FlOn \in Ref_{FS} \rceil)$$

$$\land (\lceil Flame \rceil; \ell \leq \delta_2 \Rightarrow \lceil FlOff \in Ref_{FS} \rceil)$$

and

$$\begin{split} FSReady & \widehat{=} \\ & (\lceil Flame \rceil \Rightarrow (\lceil \rceil \sim \delta_1 \leadsto (\lceil \mathsf{FlOn} \not \in \mathsf{Ref}_{\mathsf{FS}} \rceil)) \\ & \wedge (\lceil \neg Flame \rceil \Rightarrow (\lceil \rceil \sim \delta_1 \leadsto (\lceil \mathsf{FlOff} \not \in \mathsf{Ref}_{\mathsf{FS}} \rceil)) \end{split}$$

# F. Actuators

The gas actuator (GA) is specified as a conjunction

$$GasActuator \cong \Box(GAReady \land GAAct)$$

of two progress constraints: the gas actuator never refuses GasOn or GasOff events

$$GAReady = \lceil Ref_{GA} = \{\} \rceil \lor \lceil \rceil$$

and, for an empty trace, the gas is off. Otherwise, the value stabilizes  $\delta_1$  after the latest GasOn or GasOff event

$$\begin{split} GAAct & \cong \\ & (\lceil \mathtt{tr}_{\mathtt{GA}} = \langle \rangle \rceil \Rightarrow \lceil \neg Gas \rceil) \\ & \wedge (\lceil \mathtt{last}(\mathtt{tr}_{\mathtt{GA}}) = \mathtt{GasOff} \rceil \\ & \Rightarrow (\lceil \rceil \sim \delta_1 \leadsto \lceil \neg Gas \rceil)) \\ & \wedge (\lceil \mathtt{last}(\mathtt{tr}_{\mathtt{GA}}) = \mathtt{GasOn} \rceil \\ & \Rightarrow (\lceil \rceil \sim \delta_1 \leadsto \lceil Gas \rceil)) \end{split}$$

where last(s) denotes the last element in the (nonempty) sequence s.

The ignition actuator (IA) has a similar specification

$$IgnitionActuator \cong \Box(IAReady \land IAAct)$$

where

$$IAReady = [Ref_{IA} = \{\}] \vee []$$

and

$$\begin{split} IAAct & \widehat{=} \\ & (\lceil \mathtt{tr}_{\mathtt{IA}} = \langle \rangle \rceil \\ & \Rightarrow \lceil \neg Ignition \rceil) \\ & \wedge (\lceil \mathtt{last}(\mathtt{tr}_{\mathtt{IA}}) = \mathtt{IgnOff} \rceil \\ & \Rightarrow (\lceil \rceil \sim \delta_1 \leadsto \lceil \neg Ignition \rceil)) \\ & \wedge (\lceil \mathtt{last}(\mathtt{tr}_{\mathtt{IA}}) = \mathtt{IgnOn} \rceil \\ & \Rightarrow (\lceil \rceil \sim \delta_1 \leadsto \lceil Ignition \rceil)) \end{split}$$

### G. Timers

IT

The 1-s timer (T1) is specified as a conjunction

$$Timer1 \triangleq \Box (T1Ready \land T1Ref)$$

of two progress constraints: the timer never refuses the settimer event Set1, and accepts the time-out event Out1 at most 1 s after the last set-timer event.

$$T1Ready \stackrel{\frown}{=} ( \lceil \rceil \lor \lceil \mathsf{Set1} \not\in \mathsf{Ref}_{\mathsf{T1}} \rceil ) \\ \land \lceil \mathsf{last}(\mathsf{tr}_{\mathsf{T1}}) = \mathsf{Set1} \rceil \land \mathsf{stable}(\mathsf{tr}_{\mathsf{T1}}) \\ \Rightarrow (\lceil \rceil \sim 1 \leadsto \lceil \mathsf{Out1} \not\in \mathsf{Ref}_{\mathsf{T1}} \rceil )$$

and a refusal constraint: The time-out event Out1 is only accepted 1 s after a set timer event Set1.

$$T1Ref = [tr_{T1} = s]; [tr_{T1} = s^{\langle Set1 \rangle}]; [Out1 \notin Ref_{T1}] \Rightarrow \ell > 1$$

From the timer specification it is easy to deduce

The other timer has a similar specification

$$Timer30 \cong \Box (T30Ready \wedge T30Ref)$$

vhere

and

$$T30Ready \stackrel{\frown}{=}$$

$$(\lceil \rceil \lor \lceil \texttt{Set30} \not\in \texttt{Ref}_{\texttt{T30}} \rceil)$$

$$\land \lceil \texttt{last}(\texttt{tr}_{\texttt{T30}}) = \texttt{Set30} \rceil \land \texttt{stable}(\texttt{tr}_{\texttt{T30}})$$

$$\Rightarrow (\lceil \rceil \sim 30 \rightsquigarrow \lceil \texttt{Out30} \not\in \texttt{Ref}_{\texttt{T30}} \rceil)$$

$$T30Ref \stackrel{\frown}{=}$$

$$\lceil \texttt{tr}_{\texttt{T30}} = \texttt{s} \rceil; \lceil \texttt{tr}_{\texttt{T30}} = \texttt{s} ^{\land} \langle \texttt{Set30} \rangle \rceil$$

$$; \lceil \texttt{Out30} \not\in \texttt{Ref}_{\texttt{T30}} \rceil$$

$$\Rightarrow \ell > 30$$

# H. Composition

The *composite* system is specified by the conjunction of the component specifications, the scheduler specification and the general properties

$$System \cong$$

$Program \wedge HeatReqSensor \wedge FlameSensor$

$\wedge GasActuator \wedge IgnitionActuator \wedge Timer1$

$\wedge Timer30 \wedge Scheduler \wedge General$

### VIII. CORRECTNESS OF ARCHITECTURE

We have already argued that the program implements the automaton

$$General \wedge Scheduler \wedge Program \Rightarrow Phases$$

It remains to verify that the architecture refines the Phase requirements.

Here we use that *Program* is the only component that delays output events, i.e., events in the set

Out

$$\hat{=}$$

Event\In

The scheduler ensures that the delay is, at most,  $\delta_1$ . Thus we have

$$System \Rightarrow Outprogress$$

where

$$Outprogress \,\widehat{=}\, \Box \, (\lceil \mathtt{tr} = \mathtt{s} \wedge \mathtt{nextOut} \, (\mathtt{s}) \rceil \Rightarrow \ell < \delta_1)$$

and

$$nextOut(s) \stackrel{\frown}{=} \exists e : Out \bullet s ^{\frown} \langle e \rangle \in ptrace$$

From Outprogress it follows that a sequence of n out-events will take at most  $n \cdot \delta_1$  time units to complete.

Each phase is defined by a sequence of out-events and is terminated by a single in-event or a choice between in-events, cf. the definition of ptrace and inptrace. The transition to a next phase will only happen when both the program and the sensor or timer are ready.

Using these facts about the trace and the results about Outprogress we have the following:

$$System \Rightarrow$$

$$\Box (LIdle \land LPurge \land LIgnite1 \land LIgnite2 \land LBurn)$$

where the lemmas for the phases are

```

LIdle \stackrel{\frown}{=}

(\lceil \text{Ignite1} \rceil \Rightarrow (\lceil \rceil \sim 3 \cdot \delta_1 \leadsto

(stable(tr) \land \lceil last_2(tr) = \langle IgnOff, GasOff \rangle \rceil

\land [HeatOn \notin Ref_P]))

\land ([Idle]; [\neg Idle] \Rightarrow \lozenge [HeatOn \notin Ref_{HS} \land Idle])

LPurge \stackrel{\frown}{=}

([Purge] \Rightarrow [last_2(tr_{GA \cup IA}) = \langle IgnOff, GasOff \rangle])

\land ([Purge] \Rightarrow ([] \sim 2 \cdot \delta_1 \leadsto

(stable(tr) \land [last(tr) = Set30]

\land [Out30 \notin Ref_P]))

∧([Purge]; [¬Purge]

\Rightarrow \Diamond [\text{Out30} \notin \text{Ref}_{\text{T30}} \land \text{Purge}])

LIgnite1 \stackrel{\frown}{=}

(\lceil \text{Idle} \rceil \Rightarrow (\lceil \rceil \sim 4 \cdot \delta_1 \leadsto

(stable(tr) \land [last_3(tr) = \langle Set1, IgnOn, GasOn \rangle]

\land [Out1 \notin Ref_P]))

\land ([Ignite1]; [\neg Ignite1])

\Rightarrow \Diamond [Out1 \notin Ref_{Ti} \land Ignite1])

LIgnite2 \cong

(\lceil \mathtt{Ignite2} \rceil \Rightarrow \lceil \mathtt{last}_2(\mathtt{tr}_{\mathtt{GA} \cup \mathtt{IA}}) = \langle \mathtt{Ign0n}, \mathtt{Gas0n} \rangle \rceil)

(\lceil \texttt{Ignite2} \rceil \Rightarrow (\lceil \rceil \sim 3 \cdot \delta_1 \leadsto

(stable(tr) \land [last(tr) = Set1]

\land [FlOn \notin Ref_P \land Out1 \notin Ref_P])))

\land ([Ignite2]; [Idle])

\Rightarrow \Diamond \lceil \text{Out1} \notin \text{Ref}_{\text{T1}} \land \text{Ignite2} \rceil)

∧([Ignite2];[Burn]

\Rightarrow \Diamond [Fl0n \notin Ref_{FS} \land Ignite2])

LBurn \stackrel{\frown}{=}

(\lceil Burn \rceil \Rightarrow \lceil last(tr_{GA}) = GasOn \rceil)

\land ([Burn] \Rightarrow ([] \sim 2 \cdot \delta_1 \leadsto

(stable(tr) \land [last(tr) = IgnOff]

\land \lceil FlOff \not\in Ref_P \land HeatOff \not\in Ref_P \rceil)))

\land ([Burn]; [\neg Burn] \Rightarrow

\lozenge \lceil (\text{FlOff} \notin \text{Ref}_{\text{FS}} \lor \text{HeatOff} \notin \text{Ref}_{\text{HS}})

∧ Burn])

```

We have used  $last_n(s)$ ,  $n \ge 1$  to denote the subsequence formed by the last n elements of s ( $last_n(s)$  s only defined when  $\#s \ge n$ ).

We can now illustrate the verification of phase contraints by

$System \Rightarrow IdleReq.$

Stability under  $\neg Heatreq$  is verified by deduction to a contradiction. We assume that  $\varepsilon_2 \leq \delta_2$

$$\begin{split} & HSRef \wedge \square LIdle \wedge (\lceil \neg Heatreq \rceil; \ell \leq \varepsilon_2) \\ & \wedge \diamondsuit (\lceil \texttt{Idle} \rceil; \lceil \neg \texttt{Idle} \rceil) \\ \Rightarrow \square LIdle \wedge \lceil \texttt{HeatOn} \in \texttt{Ref}_{\texttt{HS}} \rceil \\ & \wedge \diamondsuit (\lceil \texttt{Idle} \rceil; \lceil \neg \texttt{Idle} \rceil) \\ \Rightarrow \diamondsuit (\lceil \texttt{HeatOn} \in \texttt{Ref}_{\texttt{HS}} \rceil \wedge \lceil \texttt{HeatOn} \not \in \texttt{Ref}_{\texttt{HS}} \rceil) \\ \Rightarrow & false. \end{split}$$

Progress to Purge is shown by a similar deduction where we assume that  $4 \cdot \delta_1 < \epsilon_1$

$$\begin{split} &Scheduler \wedge \square \, LIdle \wedge HSReady \\ & \wedge \lceil \mathtt{Idle} \rceil \wedge \lceil Heatreq \rceil \wedge \ell > \varepsilon_1 \\ \Rightarrow &Scheduler \wedge \\ & (\lceil \rceil \sim 3 \cdot \delta_1 \leadsto (\lceil \mathtt{HeatOn} \not\in \mathtt{Ref}_\mathtt{P} \rceil \wedge \mathsf{stable}(\mathtt{tr})) \\ & \wedge (\lceil \rceil \sim \delta_1 \leadsto \lceil \mathtt{HeatOn} \not\in \mathtt{Ref}_\mathtt{HS} \rceil) \wedge \ell > \varepsilon_1 \\ \Rightarrow &false. \end{split}$$

Progress to  $\neg Gas$  and  $\neg Ignition$  follows from

$$\Box LIdle \wedge GAAct \wedge IAAct \wedge \lceil Idle \rceil$$

$$\Rightarrow (\lceil \rceil \sim 4 \cdot \varepsilon_1 \leadsto \lceil \neg Gas \rceil)$$

$$\wedge (\lceil \rceil \sim 4 \cdot \varepsilon_1 \leadsto \lceil \neg Ignition \rceil)$$

Stability of Purge is verified as follows:

$$□ T30Ref ∧ □ LPurge ∧ ( [¬Purge]; ℓ ≤ 30)$$

$$∧ ◊ ( [Purge]; [¬Purge] )$$

$$⇒ ◊ (ℓ ≤ 30$$

$$∧ ( [tr = s]; [tr = s ^ ⟨Set30⟩]$$

$$; [0ut30 \notin Ref_{T30}] )$$

$$∧ T30Ref )$$

$$⇒ false.$$

Verification of progress in Ignite1 requires  $3 \cdot \delta_1 < \varepsilon_1$ .

For Ignite2 we have a new kind of deduction in order to verify  $\lceil Gas \land Ignition \rceil$  throughout the phase. We look for a contradiction of

$$\Diamond [\neg (Gas \land Ignition) \land Ignite2]$$

First, we have, from the properties of ptrace,

We can now deduce

$$System \land \lozenge \lceil \neg (Gas \land Ignition) \land \texttt{Ignite2} \rceil \Rightarrow \square(LIgnite1 \land LIgnite2 \land GAAct \land AAAct) \land \lozenge (\lceil \texttt{Purge} \rceil; \lceil \texttt{Ignite1} \rceil \qquad ; (\lceil \texttt{Ignite2} \rceil \land \lozenge \lceil \neg (Gas \land Ignition) \rceil))) \Rightarrow \square(GAAct \land IAAct) \land \\ \lozenge (\ell \ge 1 - 3 \cdot \delta_1 \\ \land \lceil \texttt{last}_2(\texttt{tr}_{\texttt{GA} \cup \texttt{IA}}) = \langle \texttt{IgnOn}, \texttt{GasOn} \rangle \rceil \\ \land (true; \lceil \neg (Gas \land Ignition) \rceil)) \Rightarrow false.$$

provided that  $\delta_1 \leq 1 - 3 \cdot \delta_1$ ; i.e.,  $4 \cdot \delta_1 \leq 1$  or  $\delta_1 < 1/4$ .

Maintenance of Gas in the Burn phase requires a similar argument.

In summary: whenever  $\delta_1$  is chosen such that  $5 \cdot \delta_1 < \varepsilon_1 < 2/7$  the distributed system will work. Notice that the minimal latency  $\delta_2$  can be arbitrarily small because  $\varepsilon_2$  has no lower bound. In other words: a faster computer will not invalidate the architecture. This is achieved by using explicit timers to implement delays.

### IX. CONCLUSION

We have illustrated an approach to requirements engineering and design of real-time systems using mathematical specifications of system requirements and system design. We have demonstrated how mathematical reasoning is used in verifying that designs satisfy requirements and in proving that a more detailed distributed design satisfies an abstract centralized design.

Duration calculus has been our tool. This logic combines central properties of integral calculus with the serial composition ability of interval logic and the parallel composition properties of usual logic. Furthermore, it has a conventional dynamic system as model, which gives a strong link to well established mathematical theories used in control engineering.

The approach is still developing as we gain more understanding of the abilities of duration calculus, and as we see how good design principles are reflected in the formulas. We now discuss some issues in the three stages of the approach.

# A. System Model and Requirements

As presented here, the requirements are straightforward formalizations of user expectations. It would be useful to have a more systematic approach for eliciting these expectations. One possibility that we would like to investigate is to derive the safety requirements from the results of a systematic safety analysis of the system. This could, for instance, be done by formalizing the results of fault tree analysis, cf. the approach in the British Ministry of Defence draft standard for software in safety critical systems [27], [28] or the approach suggested in [39].

# B. Control Model and Law

T

The use of a finite state machine to give the control structure is not new, but we see it as a strength that the paradigm is used by other researchers (see the introduction). Our main reason for chosing such a restricted structure is that we would like a design to be consistent. It is fairly obvious that the specification of the automaton Phases has a model. We have taken some pains to give the phase-state constraints PhaseReq a form that ensures consistency. The system states HeatReq and Flame occurs only in the premise of the individual phase requirements, and only in the form of single occurrences of mutually exclusive state assertions, e.g.  $\neg HeatReq$  and Heatreq. These states are thus free to vary in a model. The controlled states Ignition and Gas occur in the same form, but in the consequence for the individual phase requirements. It is thus posible to assign consistent values

for each phase. We can also check that upper bounds on the duration of a single phase are higher than the possible lower bounds. For example, for Ignite2 we have an upper bound of  $1+\varepsilon_1$  and lower bounds of 0 or 1. Thus the Phases and PhaseReq constraints have a reasonable model. The assumptions Asm might spoil this, but we have used a form where premisses contain mutually disjoint assertions on the controlled states, and consequences are constraints on the free state Flame. This leaves Heatreq unconstrained, as we expect it to be.

We are less concerned with consistency of top-level requirements. In fact, we expect them to be inconsistent at the start of a development—user expectations are generally too high. They will be relaxed during the design verification activity because it would be impossible to find a consistent design that satisfies all of them.

The control law specification could be used directly for development of a program with shared variables, linking to such approaches as [6], [8], and [24]. We might add that a control law can be refined by expanding a phase into subphases, e.g., the division of the Ignite phase. We do not foresee problems with such serial refinements. They are analogous to refinement of sequential programs.

The present formulation of control laws would also aid in a generalization to hybrid systems [25], [26], and [30], where continuous physical states can be constrained by differential equations in the individual phases or in the assumptions. This requires an extension of the duration concept to properties of continuous states and a notation for initial values in an interval for such states. Such an extension was introduced in [37].

### C. Verification

With the restricted form of predicates used in the verification, there is some indication that these might be decidable. This would allow mechanical support for the tedious parts of the calculations. If a finite state machine is inadequate or inconvenient, it is possible to add further control state variables and thus get the full power of a Turing machine. This will, however, make verification more difficult because the phases may be interrelated in nonobvious ways. It would also make mechanized verification support difficult.

# D. Architecture, Components, and Scheduling

We have not pursued the state machine approach for a distributed architecture because of the involved proof obligations for shared variables. We have also refrained from pursuing an asynchronous event approach because timing constraints would have to be formulated as constraints on arrival and departure time for elements in unbounded buffers. We have seen dynamic buffer systems in practice, and they have not convinced us that arguments for timeliness are assisted by having global buffer pools. In the presentation, we have tried to build on the fundamental work by Reed on Timed CSP [38]. We have, however, yet to fully clearify the relations between our model and his hierarchy. The concept of a scheduler as an explicit component is elaborated in [48].

.....

we have

### APPENDIX **DEDUCTION SYSTEM, VERIFICATION**

General duration calculus is undecidable, and hence we cannot expect to find a complete set of axioms and deduction rules. The deductions in this paper may, hovewer, be based on the set of axioms and deduction rules given as follows.

A suitably decorated P, r or  $\mathcal{D}$  in the formulas denotes a state assertion, a nonnegative real number or a formula in duration calculus. Symbols ff and tt are the truth values for state assertions. Note that general laws of the propositional and predicate calculus are not included, whereas some laws of interval temporal logic are.

```

Axiom 1: \int ff = 0

Axiom 2: \int P \geq 0

Axiom 3: \int P_1 + \int P_2 = \int (P_1 \vee P_2) + \int (P_1 \wedge P_2)

Axiom 4: If r_1 \geq 0 and r_2 \geq 0, then

(\int P = r_1); (\int P = r_2) \Leftrightarrow \int P = (r_1 + r_2)

Axiom 5: If P_1 \Leftrightarrow P_2 is a valid state assertion, then

\int P_1 = \int P_2 is an axiom.

```

The following induction rule is sound due to the finite variability of states.

```

Induction Rule: If \mathcal{D}(\lceil \rceil) is deduced, and

\mathcal{D}(X \vee (X; [P]) \vee (X; [\neg P])) is deducible from \mathcal{D}(X),

then \mathcal{D}(true) is deduced.

```

It has a dual backward induction rule.

The following are rules of interval logic used in calculations. Interval Law 1: Monotonic: If  $\mathcal{D}_1 \Rightarrow \mathcal{D}'_1$  and  $\mathcal{D}_2 \Rightarrow \mathcal{D}'_2$ then  $\mathcal{D}_1; \mathcal{D}_2 \Rightarrow \mathcal{D}_1'; \mathcal{D}_2'$ .

```

Interval Law 2: Associative:

(\mathcal{D}_1; \mathcal{D}_2); \mathcal{D}_3 \Leftrightarrow \mathcal{D}_1; (\mathcal{D}_2; \mathcal{D}_3)

Interval Law 3: False-Zero:

false \Leftrightarrow \mathcal{D}; false \Leftrightarrow false; \mathcal{D}

Interval Law 4: Point-Unit: \mathcal{D} \Leftrightarrow \mathcal{D}; \square \Leftrightarrow \square; \mathcal{D}

Interval Law 5: Chop-And:

(\mathcal{D}_1; (\mathcal{D}_3 \wedge \ell = r)) \wedge (\mathcal{D}_2; (\mathcal{D}_4 \wedge \ell = r))

\Rightarrow (\mathcal{D}_1 \wedge \mathcal{D}_2); (\mathcal{D}_3 \wedge \mathcal{D}_4)

((\mathcal{D}_1 \wedge \ell = r); \mathcal{D}_2) \wedge ((\mathcal{D}_3 \wedge \ell = r); \mathcal{D}_4)

\Rightarrow (\mathcal{D}_1 \wedge \mathcal{D}_3); (\mathcal{D}_2 \wedge \mathcal{D}_4)

Interval Law 6: Chop-Or:

(\mathcal{D}_1 \vee \mathcal{D}_2); \mathcal{D}_3 \Leftrightarrow \mathcal{D}_1; \mathcal{D}_3 \vee \mathcal{D}_2; \mathcal{D}_3

\mathcal{D}_1; (\mathcal{D}_2 \vee \mathcal{D}_3) \Leftrightarrow \mathcal{D}_1; \mathcal{D}_2 \vee \mathcal{D}_1; \mathcal{D}_3

Interval Law 7: Chop-Neg:

\neg(\mathcal{D}_1; (\mathcal{D}_2 \wedge \ell = r))

\Leftrightarrow (true; (\neg \mathcal{D}_2 \land \ell = r)) \lor (\neg \mathcal{D}_1; \ell = r) \lor \ell < r

\neg((\mathcal{D}_1 \wedge \ell = r); \mathcal{D}_2)

\Leftrightarrow ((\neg \mathcal{D}_1 \land \ell = r); true) \lor (\ell = r; \neg \mathcal{D}_2) \lor \ell < r

Interval Law 8: Exists-Chop:

```

$(\exists v: T \bullet \mathcal{D}_1); \mathcal{D}_2 \Leftrightarrow \exists v: T \bullet \mathcal{D}_1; \mathcal{D}_2 \text{ provided } v \text{ does not}$ occur free in  $\mathcal{D}_2$ .

$\mathcal{D}_1$ ;  $(\exists v : T \bullet \mathcal{D}_2) \Leftrightarrow \exists v : T \bullet \mathcal{D}_1$ ;  $\mathcal{D}_2$  provided v does not occur free in  $\mathcal{D}_1$ .

The following derived laws have been useful:

```

Law 1: Dur-Range: 0 \le \int P \le \ell

```

Law 2: Dur-Negation:

$$\int \neg P = \ell \Leftrightarrow \int P = 0$$

Law 3: Dur-Chop-Add: Given a predicate over reals  $R(r_1, \ldots, r_m)$ , which is preserved under addition, i.e.,  $R(r_1,\ldots,r_m)\wedge R(r'_1,\ldots,r'_m)\Rightarrow R(r_1+r'_1,\ldots,r_m+r'_m),$

```

R(\int P_1, \ldots, \int P_m); R(\int P_1, \ldots, \int P_m)