# Substrate Optimization Based on Semi-Analytical Techniques

Edoardo Charbon, *Member*, *IEEE*, Ranjit Gharpurey, Robert G. Meyer, *Fellow*, *IEEE*, and Alberto Sangiovanni-Vincentelli, *Fellow*, *IEEE*

Abstract—Several methods are presented for highly efficient calculation of substrate noise transport in integrated circuits. A three-dimensional Green's function-based boundary element method, accelerated through use of the fast Fourier transform, allows the computation of sensitivities with respect to all substrate parameters at a considerably higher speed than any methods reported in the literature. Substrate sensitivities are used in a number of physical optimization tools, such as placement and trend analysis. The aim is a fast and accurate estimation of the impact of technology migration and/or layout redesign on substrate noise and, ultimately, on the circuit's overall performance. The suitability of the approach is shown through industrial-strength mixed-mode integrated circuits fabricated on a standard CMOS process.

Index Terms—Boundary element methods, convergence of numerical methods, discrete Fourier transients, integrated circuit noise, noise, noise generators, noise measurement, numerical analysis, numerical stability, optimization methods, phase noise, sensitivity, semiconductor device noise, switching circuits, switching transients.

#### I. INTRODUCTION

NCREASED chip size, device density, and feature miniaturization, as well as overall higher frequencies of operation, have made the problem of substrate noise critical in the design of integrated circuits.

Accurately characterizing substrate noise is problematic for various reasons. The noise results from superposition of a large number of local and remote sources, each attenuated and delayed in a unique way. Modeling signal attenuation and delay individually may be extremely time-consuming and would require accurate *ad hoc* characterization of all the sources, which is in itself a hard problem [1]. The interaction of substrate noise with sensitive devices is often difficult to evaluate due to the complexity of the effects of noise on performance, especially with erratic noise waveforms. Moreover, reduced distances between high-swing high-frequency noise sources and sensitive circuitry exacerbates the problem, thus making the design task even more challenging.

To combat the effects of substrate noise, heavily overdesigned structures are generally adopted, thus seriously limit-

Manuscript received September 16, 1997; revised April 18, 1998. This paper was recommended by Associate Editor D. Ling.

- E. Charbon is with Cadence Design Systems, Inc., San Jose, CA 95134 USA (e-mail: charbon@cadence.com).

- R. Gharpurey is with Texas Instruments, Inc., Dallas, TX 75080 USA.

- R. G. Meyer and A. Sangiovanni-Vincentelli are with the University of California at Berkeley, Berkeley, CA 94720 USA.

Publisher Item Identifier S 0278-0070(99)01006-4.

ing the advantages of innovative technologies. For this reason, recently a serious effort has been made to model substrate noise sources and transport mechanisms, thus allowing designers to detect potential problems before fabrication. Specific guidelines have also been drafted for more aggressive, substrate-aware design practices.

At a macroscopic level, substrate noise is characterized by intrinsic and switching noise. Intrinsic noise is a background spurious signal originated in active and passive devices through various physical phenomena, namely thermal, shot, and flicker noise. Switching noise originates mostly in digital blocks where frequent state transitions, occurring in gates across the chip, result in current pulses absorbed from and transmitted to supply/ground lines through direct feedthrough and load charge/discharge. Such pulsing currents are partially injected into the substrate through impact ionization and capacitive coupling.

Generally, switching noise is by far the most destructive of all substrate noise types. It can be broadcasted over great distances, acting on all transistors by modulating threshold voltage and gain, and directly coupling with signal voltages, thus increasing the average delay of digital blocks. Switching noise has an especially detrimental effect on analog and mixedsignal circuits. In these circuits the presence of sensitive structures and large noise injectors on the same chip makes it imperative for the designer to accurately and efficiently estimate the strength of substrate noise at various locations. Evidently, CAD tools able to provide accurate injection and substrate transmission models are key to successful design flows. Furthermore, efficient substrate analysis, coupled with layout optimization, provides higher guarantees to reduce the design cycle, while ensuring satisfaction of tighter performance specifications.

Anisotropic substrates were first studied by Fukahori [2], who discretized the space into a resistive/capacitive mesh. DC/steady-state analysis was carried out by direct solution of the system of simultaneous thermal and electrical equations. Transient analysis was performed by using variable time-step trapezoidal integration techniques. In the dc analysis, direct LU factorization was later replaced with the incomplete Choleski conjugate gradient iterative method (ICCG). Transient analysis on the contrary was accelerated with frequency domain solutions such as asymptotic waveform evaluation (AWE) [3], [4].

Recently, attempts to introduce the effects of substrate in the design of medium-sized IC's have been made using numerical finite-difference methods (FDM's). These techniques are versatile and general in nature, since they can handle lateral and vertical resistivity variations and arbitrary substrate geometries. However, to obtain accurate substrate characterization, a fine mesh is required, thus making storage and computational efforts often prohibitive. To overcome the formidable computational complexity of the problem, sparse nonuniform grids are often used. The grid size is made fine in areas close to substrate contacts and coarse in distant regions [5], [6]. The use of nonuniform or coarse grids, however, involves speed-accuracy tradeoffs, which are often difficult to evaluate a priori. Boundary element methods (BEM's) can also be used for parasitic and substrate extraction. In [7]–[9], the use of the Green's Function was proposed for a finite uniform medium and later for a multilayer substrate, with zero normal electric field boundary conditions, exploiting the technique of the separation of variables. Image-chargebased concepts have been used, in order to avoid the series computation involved in the method.

Traditionally, the analysis of substrate noise has been performed after the completion of physical design as a verification step. Experience has shown the extreme time complexity required to accurately model substrate and to estimate performance degradations due to switching noise. In many design problems, however, a dynamic substrate noise analysis would be preferable, since it could drive the design toward solutions more resilient to substrate noise. Recently, this problem was addressed by a number of authors who proposed heuristics to speed up substrate analysis during physical assembly phases, e.g., [6] and [10]. The approaches have in common the use of an FDM for the evaluation of the electric field on a coarse grid spanning the workspace, combined with AWE for an efficient solution of the resulting system of simultaneous algebraic equations. A potential problem with this approach is a strict requirement of alignment between grid and layout objects. Thus, unless specific tessellation [11] or analytical approximations [12], [13] are used, iterative algorithms based on progressive and often minimal modifications may not fully take advantage of the algorithms.

In this paper we propose a set of fast semi-analytical techniques for substrate analysis, which have been further accelerated for use within optimization loops. The algorithm at the heart of the substrate analysis package SUBRES, is a Green's Function-based BEM for multilayered substrates accelerated using the discrete cosine transform (DCT), which is efficiently computed via the fast Fourier transform (FFT). SUBRES generates a network accurately modeling contact-to-contact resistances in arbitrarily-shaped doping regions. The method can be further accelerated if accuracy can be traded off for circuit complexity. We show how upperbounds to accuracy degradation can be computed exactly.

Sensitivities of all the network components with respect to a number of technology parameters are computed using analytical manipulations of the Green's Function expressions and coded directly in the FFT, thus allowing fast evaluations on demand. Computing sensitivities of substrate coupling is useful for a number of reasons. First, it allows the evaluation of the impact of slight imperfections in the fabrication process on the circuit's performance and, ultimately, its yield. Second,

it can be used as a quality factor for the selection of the best cost-effective technology on the basis of a class of circuits one wants to fabricate with given specifications. Furthermore, one can characterize the *trend* of circuit performance when engineering changes are performed on substrate geometry, technology parameters, or design. Third, the technique can be used during optimization to help the decision process providing guidance to the best possible improvement. Hence, the effects of technology migration/scaling can be carried out efficiently for a given chip without the need of performing a large number of complete substrate extractions. Fourth, sensitivities can be used to build performance models accounting for discrete parasitics as well as substrate effects. We show how these models can be efficiently built and used in demanding optimization algorithms at little computational cost.

The paper is organized as follows. In Section II substrate evaluation techniques based on a DCT accelerated BEM are described. Section III outlines the techniques used for sensitivity analysis and sensitivity-based optimization. A number of design optimization problems are presented in Section IV. In Section V the suitability of the approach is illustrated with a medium-sized mixed-signal IC designed using substrate-aware optimization and fabricated on a standard CMOS process.

#### II. MODELING SUBSTRATE TRANSPORT

# A. Problem Formulation and Solutions

In general, silicon substrates are composed by one or more lightly doped epitaxial layers and a highly doped "core." Hence, differently conductive areas are present in the vertical section of the chip, while lateral resistivity variations are due to device and well implants as well as other integrated components. The latter are junctions with the substrate, and, in many cases, they may be considered equipotential. There are, however, situations in which this assumption is not adequate; in these cases it is advisable to partition such structures into separate contacts. Calculating resistances between any contact locations on the substrate requires the computation of electric potential  $\Phi(x,y,z,t)$  at any location (x,y,z) in the bulk. From Maxwell's equations one can show that

$$\frac{1}{\rho}\nabla \bullet \nabla \Phi(x, y, z, t) + \epsilon \frac{\partial}{\partial t} \left(\nabla \bullet \nabla \Phi(x, y, z, t)\right) = 0 \quad (1)$$

holds, where  $\epsilon$  and  $\rho$  are, respectively, the local dielectric permittivity and resistivity of the substrate. In the electrostatic case, (1) reduces to the Laplace equation

$$\nabla^2 \Phi = 0 \tag{2}$$

with either Dirichlet or Neumann<sup>1</sup> boundary conditions or a combination of the two on the surfaces. Equation (2) can be solved using Green's Function-based BEM's [14].

Let  $\Phi(\mathbf{r})$  be the potential at point  $\mathbf{r}=(x,y,z)$  resulting from a localized charge density  $\rho(\mathbf{r}')$ , and  $\Psi(\mathbf{r},\mathbf{r}')$  the potential at  $\mathbf{r}$  due to a point charge placed at a point  $\mathbf{r}'$ . Then,  $\Phi(\mathbf{r})$

<sup>&</sup>lt;sup>1</sup> Dirichlet conditions impose a given potential, Neumann conditions a given electric field.

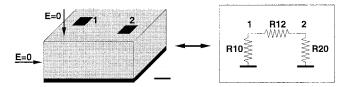

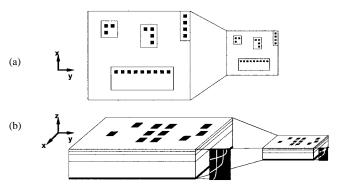

Fig. 1. Substrate boundaries and contact resistance modeling.

can be expressed as

$$\Phi(\mathbf{r}) = \int_{V} \rho(\mathbf{r}') \Psi(\mathbf{r}, \mathbf{r}') d^{3}\mathbf{r}' + \epsilon \oint_{S} \left( \Psi \frac{\partial \Phi}{\partial n} - \Phi \frac{\partial \Psi}{\partial n} \right) ds'$$

(3)

where  $\cdot/\partial n$  symbolizes the derivative with respect to  $\hat{\mathbf{n}}$ , the unit outward normal vector to surface S enclosing volume V.  $\Psi(\mathbf{r},\mathbf{r}')$  is called *Green's Function*. If the Green's Function is known, (3) allows one to determine the potential at any point in the volume V due to a known arbitrarily distributed charge density. Image-based techniques and the method of separation-of-variables (SOV) are two different approaches for evaluating the Green's Function. The methods are described in detail in [15, Ch. 3].

In the electrostatic case, the problem of computing the resistance between a substrate contact and all the others can be translated into that of computing the charge at the contact when set at a potential of 1 V, while the other contacts and the backplane are grounded. The reason for this is the following. Capacitance  $C_{ij}$  between contacts i and j is defined as the ratio of the charge on contact j to the potential of contact i, or  $C_{ij} = Q_j/\Phi_i$ . By Stokes Theorem

$$C_{ij} = \frac{1}{\epsilon} \oint_{S} E \bullet \hat{\mathbf{n}} \, ds \tag{4}$$

where  $\hat{\mathbf{n}}$  is the unit outward normal vector to the surface S which encompasses the contact. E is the electric field in the medium. Similarly, the resistance between contacts is defined as

$$R_{ij} = Y_{ij}^{-1} = \left[ -\sigma \oint_{S} E \bullet \hat{\mathbf{n}} \, ds \right]^{-1} = -\frac{1}{\sigma \epsilon} \frac{\Phi_{i}}{Q_{i}} \tag{5}$$

where  $\sigma$  is the medium conductivity. Note that in both the resistive and the capacitive cases the potential satisfies the Laplace equation, thus the problems can be interchanged freely.

At frequencies up to 4–5 GHz, substrate susceptance is typically much smaller than the conductance, hence it may be ignored and all substrate impedances may be considered real. Consider the problem of computing the resistance between contacts 1 and 2, and toward ground in Fig. 1. This represents a mixed-boundary problem, since zero potential in the chip's backplane is assumed (Dirichlet condition) and vanishing normal electric field on the other faces (Neumann condition). Under these conditions, (3) simplifies to

$$\Phi(\mathbf{r}) = \int_{V} \rho(\mathbf{r}') G(\mathbf{r}, \mathbf{r}') d^{3}\mathbf{r}'$$

(6)

where V is the chip's volume region and G the Green's Function. The potential of a contact is computed as the

Fig. 2. Multilayer doping profiles.

result of averaging all internal contact partitions. Hence, using (6), the potential of contact i can be derived as  $\bar{\Phi}_i = \frac{1}{V_i} \int_{V_i} \int_{V_j} \rho_j G \, dv_j \, dv_i$ ,  $V_i$  and  $V_j$  being the volumes of contacts i and j and  $\rho_j$  the charge distribution on j. If a uniform charge distribution  $\rho_j = Q_j/V_j$  is chosen over j, we obtain

$$\bar{\Phi}_i = \frac{Q_j}{V_j V_i} \int_{V_i} \int_{V_j} G \, dv_j \, dv_i. \tag{7}$$

The solution to (6) for each contact pair yields the *coefficient of* potential matrix  $\mathbf{P}$ . The relation between matrix  $\mathbf{P}$  and vector  $\mathbf{\bar{\Phi}}$ , the average potential at each contact, and  $\mathbf{Q}$ , the charge associated with all contacts, is described as

$$\bar{\Phi} = PQ$$

and  $Q = c\bar{\Phi}$  (8)

where  $\mathbf{c} = \mathbf{P}^{-1}$  is called *coefficient of induction* matrix. For a contact i, the capacitance to ground  $C_i$  and all mutual capacitances  $C_{ij}$  are characterized as

$$C_i = \sum_{j=1}^{N} c_{ij}, \quad C_{ij} = -c_{ij}$$

(9)

where N is the size of matrix  $\mathbf{c}$  [15]. Using (4) and (5) in combination with relations (9), all mutual and ground resistances can be easily derived.

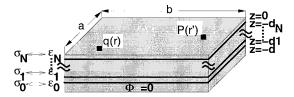

#### B. Computing the Green's Function in Multilayered Substrates

The full derivation of the Green's Function for multilayered problems can be found in [15] and [16]. Here, we shall outline the basic steps to justify the sensitivity analysis and some optimization techniques proposed in this paper. Fig. 2 shows the multilayered structure for which a Green's Function must be computed. The figure shows for each layer i its conductivity  $\sigma_i$  and the permittivity  $\epsilon_i$  associated with the equivalent electrostatic problem. Consider the case in which the point-charge at  $\mathbf{r}=(x,y,0)$  and the observation point at  $\mathbf{r}'=(x',y',0)$  are localized to a layer with dielectric permittivity  $\epsilon_N$ . The Green's Function corresponds to an infinite series of sinusoidal functions

$$G(r,r') = G_0|_{z=z'=0} + \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} f_{mn} C_{mn} \cos\left(\frac{m\pi x}{a}\right) \times \cos\left(\frac{m\pi x'}{a}\right) \cos\left(\frac{n\pi y}{b}\right) \cos\left(\frac{n\pi y'}{b}\right)$$

(10)

where  $C_{mn}=0$  for m=n=0,  $C_{mn}=2$  for m=0 or n=0, but  $m\neq n$ , and  $C_{mn}=4$  for all m,n>0. Parameters a,b, and d are the dimensions of substrate in x-, y-, and z-direction (see Fig. 2). Formulae for terms  $G_0|_{z=z'=0}$  and  $f_{mn}$  can be found in [15] and [17].

From (7), adapted for surface contacts, one can derive an expression for the average potential at contact i due to the charge on contact j. Consequently, the entry  $p_{ij}$  of matrix  $\mathbf{P}$ , computed as the ratio of  $\overline{\Phi}_i$  and  $Q_j$ , becomes

$$p_{ij} = \frac{\bar{\Phi}_i}{Q_j} = \frac{1}{S_i S_j} \int_{S_i} \int_{S_i} G(s_j, s_i) \, ds_j \, ds_i \qquad (11)$$

where  $S_i$  and  $S_i$  are the surfaces of the contacts.

Replacing (10) into (11) and integrating, one obtains an explicit formula for  $p_{ij}$

$$p_{ij} = G_0|_{z=z'=0} + \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} k_{mn} \times \frac{\left[\sin\left(m\pi\frac{a_2}{a}\right) - \sin\left(m\pi\frac{a_1}{a}\right)\right] \left[\sin\left(m\pi\frac{a_4}{a}\right) - \sin\left(m\pi\frac{a_3}{a}\right)\right]}{(a_2 - a_1)(a_4 - a_3)} \times \frac{\left[\sin\left(n\pi\frac{b_2}{b}\right) - \sin\left(m\pi\frac{b_1}{b}\right)\right] \left[\sin\left(m\pi\frac{b_4}{b}\right) - \sin\left(m\pi\frac{b_3}{b}\right)\right]}{(b_2 - b_1)(b_4 - b_3)}$$

(12)

with

$$k_{mn} = \frac{a^2 b^2 f_{mn} C_{mn}}{m^2 n^2 \pi^4}.$$

Parameters  $(a_1, a_2)$  and  $(b_1, b_2)$  are the x- and y-coordinates of node i, and  $(a_3, a_4)$  and  $(b_3, b_4)$  those of node j. Appropriately rewriting the second term of (12), after proper scaling, as a cosine series we obtain

$$\sum_{m=0}^{\infty} \sum_{n=0}^{\infty} k_{mn} \cos\left(m\pi \frac{a_{1,2} \pm a_{3,4}}{a}\right) \cos\left(n\pi \frac{b_{1,2} \pm b_{3,4}}{b}\right)$$

(13)

which is a compact representation of a sum of 64 terms forming all possible combinations of signs and indexes. By replacing the ratios of contact coordinates and the substrate dimensions with ratios of integers  $\tilde{p}$ ,  $\tilde{q}$  and summing over finite limits  $\tilde{P}$  and  $\tilde{Q}$ , term (11) becomes

$$K(\tilde{p}, \tilde{q}) = \sum_{m=0}^{\tilde{P}-1} \sum_{n=0}^{\tilde{Q}-1} k_{mn} \cos\left(m\pi \frac{\tilde{p}}{\tilde{P}}\right) \cos\left(n\pi \frac{\tilde{q}}{\tilde{Q}}\right)$$

(14)

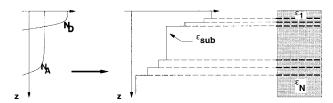

a two-dimensional (2-D) DCT of  $k_{mn}$ . Hence, the computation of  $p_{ij}$  ultimately requires only a simple DCT [15], [16]. Several techniques exist for efficient computation of the DCT, e.g., FFT-based techniques only require a computation complexity  $O(\tilde{P}\tilde{Q}\log_2\tilde{P}\tilde{Q})$ . Note that the value of  $k_{mn}$  is solely dependent on the properties of the substrate in z-direction. Hence, for a given substrate structure, the DCT needs be derived **only once**. Any modification in the relative position of one or more nodes is captured completely by the Fourier transform, thus only matrix **P** needs be calculated and inverted. However, due to the relatively small size of **P**, typically 50–5000, this process does not require a significant CPU time. Nonabrupt doping profiles can be analyzed at low CPU cost by simply discretizing in z-direction with a gradually changing value of permittivity as shown in Fig. 3.

Fig. 3. Discretization of nonabrupt doping profiles.

## C. Substrate Extraction Algorithm

The DCT of  $k_{mn}$  is computed for each location in a Manhattan grid covering the whole substrate surface. To generate matrix  $\mathbf{P}$ , it is necessary to compute the parameter  $p_{ij}$  for all the pairs of partition elements composing each contact. If no scheme is used for its reduction (see Section II-D), the size of  $\mathbf{P}$  and  $\mathbf{c}$  is

$$|\mathbf{P}| = N = \sum_{i=1}^{N_c} \mathcal{P}_i$$

where  $N_c$  is the total number of contacts and  $\mathcal{P}_i$  the number of partitions in contact i.

Due to the dense nature of  ${\bf P}$ , the inversion is the most time-consuming operation of the whole algorithm. Several inversion techniques, both direct and iterative, have been implemented by us and in [15]. Among the direct methods, an LU decomposition-based algorithm of complexity  $O(N^3)$  has been used for relatively small configurations of less than approximately 1000 partitions. Larger circuits required the use of various accuracy-driven simplification schemes.

After the computation of  ${\bf c}$ , the actual resistive or conductive networks  ${\bf R}$  and  ${\bf Y}$  are calculated.  ${\bf R}$  and  ${\bf Y}$  are  $N_c \times N_c$  matrices. Assuming appropriate scaling of  ${\bf c}$ , one can easily show that a direct relation exists between  ${\bf c}$  and  ${\bf Y}$  via mapping  ${\bf X}$

$$\mathbf{Y} = \mathbf{X}^{\mathbf{T}} \mathbf{c} \mathbf{X}, \text{ with } \mathbf{X} = [\mathbf{e}_{1}, \mathbf{e}_{2}, \cdots, \mathbf{e}_{N_{c}}]$$

(15)

where  $\mathbf{e_i} = [0, \dots, 0, 1, \dots, 1, 0, \dots, 0]^T$ . The indexes of the nonzero entries of  $\mathbf{e_i}$  are associated with the contact. Due to the structure of  $\mathbf{X}$ , (15) only involves  $(N-1)^2$  summations. The elements of matrix  $\mathbf{R}$  are computed simply using the relation  $R_{ij} = 1/Y_{ij}$ . For simplicity but without loss of generality, in what follows we will assume that  $N_c = N$ , i.e., every contact is modeled in terms of one partition.

## D. Schemes for Efficient Solution of Large Substrate Problems

Many authors who have dealt with the substrate problem have also proposed methods for the reduction of its size to improve the overall computation efficiency and to reduce the mesh of extracted parasitics. A classical approach consists of creating *active extraction windows* around each contact encompassing all the structures which are **not** ignored in the computation of the resistive network associated with the contact. However, it is not clear how inaccuracies can be bounded by a particular selection of window size and shape.

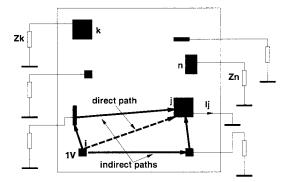

In [16] an alternative method was proposed. The aim of the method is to make matrix  $\mathbf{P}$  sparse, with bounded accuracy reduction. Consider the scenario depicted in Fig. 4. n contacts

Fig. 4. Direct and indirect current-flow paths.

are laid out on the substrate surface. Each contact k is loaded with impedance  $Z_k$ . Suppose that contact j is grounded while i is at 1 V and that the ratio  $Y_{ij} = I_j/V_i$  is sought. If  $Z_k = 0$ ,  $\forall k \neq i$ , then the direct path dominates in the computation of  $Y_{ij}$ , thus it cannot be ignored. On the contrary, when  $Z_k \neq 0$ , for some  $k \neq i$ , then a bound on the conductances associated with k can be derived for which the direct path can be ignored, without violating predetermined accuracy constraints.

Let matrix  $\mathbf{P}$  be known. By (9) and (4)  $\mathbf{Y}$ , i.e., the matrix which relates the voltages of all contacts to the currents flowing out of them, can be easily derived. Let  $\mathbf{Y}_L$  be the vector of the load admittances at each contact, for simplicity assume that  $Y_L$  is purely resistive, i.e.,  $\mathrm{Imag}\{Y_L\} = 0$ . Equation (16) represents the effects of loading on the circuit

$$[\mathbf{Y} + \mathbf{diag}(\mathbf{Y}_L)]V = I. \tag{16}$$

V and I are the vectors of contact potentials and currents, respectively. One can show that if condition

$$\left| \sum_{k=1}^{N} Y_{jk} V_k \right|_{k \neq i, k \neq j} > |Y_{ji}| V_0 \tag{17}$$

is met, component  $Y_{ji}$  can be set to zero. Note that  $V_0$  is normalized to 1 V. For each component of Y set to zero, a precise value can be computed for the lost accuracy of all currents  $I_k$  [15]. Hence the process can be applied until the cumulative inaccuracies reach a predetermined value.

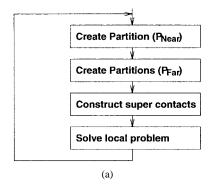

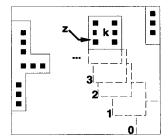

The procedure is most suited for an iterative solution scheme. Fig. 5(a) shows the complete extraction scheme. Consider each contact separately, call it *subject*. First, a partition  $P_{\text{Near}}$  is defined around the subject containing all such contacts which **do not** satisfy (17). Second, larger partitions  $P_{\text{Far}}$ , containing the remaining contacts, are created with geometrically increasing size.<sup>2</sup> See Fig. 5(b).

Third, all contacts contained in each partition  $P_{\rm Far}$  are replaced by a single contact, or *super-contact*, placed in the center of the partition and with an area equal to the sum of the areas of all the original contacts. The location and area of

Fig. 5. (a) Simplified substrate extraction scheme. (b) Partitioning of substrate.

the super-contact are

$$x_{\rm sc} = \frac{x_{\rm left} + x_{\rm right}}{2}, \quad y_{\rm sc} = \frac{y_{\rm left} + y_{\rm right}}{2},$$

$$A_{\rm sc} = \sum_{k \in P_{\rm Far}} A_k \tag{18}$$

where  $x_{\text{left/right}}$  and  $y_{\text{left/right}}$  are the left/right x- and ycoordinates of the partition boundary, respectively. Fourth, a

simplified equation is derived for the subject j. The original

equation is replaced as follows:

$$Y_{j.} \bullet V = I_{j} \to \tilde{Y}_{j.} \bullet \tilde{V} = I_{j}$$

(19)

where  $Y_j$  denotes the jth row of matrix  $\mathbf{Y}$ ,  $\tilde{Y}_j$  is a vector of size s < |Y| resulting from replacing the required number of contacts by super-contacts.  $\tilde{V}$  is the vector of the potentials on the remaining contacts and super-contacts. Potential vector  $\tilde{V}$  is evaluated and the iteration proceeds to the next subject. The algorithm terminates when every contact has been considered.

To obtain some bounds on the maximum attainable simplification rate, consider the following extreme cases: 1) every contact satisfies (17); 2) no contact satisfies (17). In case 1),  $P_{\text{Near}} = \emptyset$ , hence only super-contacts exist and the size of matrix  $\mathbf{Y}$  is reduced by one or the size of  $\mathbf{P}$  is decreased by the number of partitions internal to the subject. In 2), matrix  $\mathbf{Y}$  is not simplified, and neither is  $\mathbf{P}$ , hence the complexity of the problem remains that of inverting  $\mathbf{P}$ . However, this is generally not the case in real substrate problems, where complexity reduction in schematics is typically a factor of ten [15].

## III. SUBSTRATE-AWARE OPTIMIZATION

In this paper we often refer to low- and high-resistivity substrate. The distinction is necessary for two reasons. First, these

$<sup>^2 \</sup>text{The formula for the computation of the size is the following: } d_{k+1} = \alpha(d_k), \text{ where } \alpha = 5 \text{ in our prototype. Since in these partitions all the contacts satisfy (17), the growth criterion does not affect the accuracy in any way and it was chosen so as to facilitate partition computations.}$

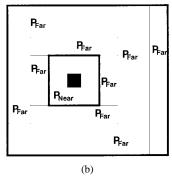

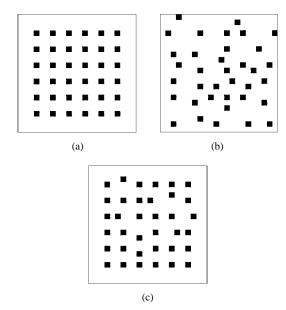

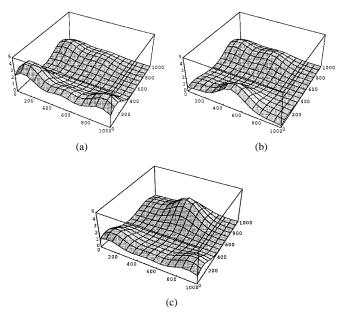

Fig. 6. Typical IC substrates: (a) high-resistivity and (b) low-resistivity.

substrate types are used mainly in BiCMOS and CMOS applications, respectively. Second, switching noise transport mechanisms are substantially different in the two substrate types, thus resulting in different design guidelines to obtain isolation. Typical substrate implementations generally used in IC fabrication are shown in Fig. 6. Injection of switching currents into substrate follow similar mechanisms. For a full description of injection and reception mechanism, see [15] and [17].

#### A. Sensitivity Analysis

The relation between circuit performance K and technology, via substrate-related parasitics, is obtained using the following expression:

$$\Delta K = \sum_{\ell} \frac{\partial K}{\partial T_{\ell}} \Delta T_{\ell}, \quad \text{with} \quad \frac{\partial K}{\partial T_{\ell}} = \sum_{i,j} \frac{\partial K}{\partial Y_{ij}} \frac{\partial Y_{ij}}{\partial T_{\ell}}$$

(20)

where (i,j) represents a contact pair,  $Y_{ij}$  the substrate conductive coupling between i and j, and  $T_\ell$  a technology parameter. Hence, assuming  $\frac{\partial K}{\partial Y_{ij}}$  exists,  $^3\Delta K$  can be easily evaluated as a linear function of technology parameters  $T_\ell$ , provided that term  $\frac{\partial Y_{ij}}{\partial T_\ell}$  has been computed. Assume that the capacitive problem has been solved and that the equivalent resistive network has been computed from the coefficient of induction matrix  ${\bf c}$ . Furthermore, let  ${\bf c}$  be scaled in such a way that the node-to-node conductance  $Y_{ij}$  and the ground conductance  $Y_{ii}$  can be computed directly using

$$Y_{ii} = \sum_{j=1}^{N} c_{ij}, \quad Y_{ij} = -c_{ij}.$$

(21)

Let us define  $\mathbf{Y}$  as an  $N \times N$  matrix consisting of  $Y_{ii}$  on the diagonal and  $Y_{ij}$  everywhere else. Let us call  $\partial \mathbf{Y}/\partial T_\ell$  the sensitivity of matrix  $\mathbf{Y}$  with respect to technology parameter  $T_\ell$ . The components of the sensitivity matrix are terms  $\partial Y_{ii}/\partial T_\ell$  on the diagonal and  $\partial Y_{ij}/\partial T_\ell$  everywhere else. The terms are computed using

$$\frac{\partial Y_{ii}}{\partial T_{\ell}} = \sum_{j=1}^{N} \frac{\partial c_{ij}}{\partial T_{\ell}}$$

and  $\frac{\partial Y_{ij}}{\partial T_{\ell}} = -\frac{\partial c_{ij}}{\partial T_{\ell}}$ . (22)

Recall that N is the size of matrix  $\mathbf{c}$ . In order to derive  $\partial c_{ij}/\partial T_{\ell}$ , (8) is differentiated on both hand-sides and solved with respect to  $\partial \mathbf{Q}/\partial T_{\ell}$ . Using the fact that  $\partial \mathbf{\bar{\Phi}}/\partial T_{\ell}$  vanishes, we obtain

$$\frac{\partial \mathbf{Q}}{\partial T_{\ell}} = -\mathbf{P}^{-1} \left( \frac{\partial \mathbf{P}}{\partial T_{\ell}} \mathbf{Q} \right). \tag{23}$$

Using the definition of  $c_{ij}$

$$\frac{\partial c_{ij}}{\partial T_{\ell}} = \frac{1}{\Phi_i} \frac{\partial Q_i}{\partial T_{\ell}} \tag{24}$$

where  $\partial Q_i/\partial T_\ell$  is computed using (23). Now, only the derivative  $\partial \mathbf{P}/\partial T_\ell$ , i.e.,  $[\partial p_{ij}/\partial T_\ell]_{i,j=1,\dots,N}$ , remains to be computed. From (12), assuming zero-depth contacts and  $T_\ell \neq \epsilon_N, d, a$  or b

$$\frac{\partial p_{ij}}{\partial T_{\ell}} = \frac{\dot{\Gamma}_{N}\beta_{N} - \Gamma_{N}\dot{\beta}_{N}}{ab\epsilon_{N}\beta_{N}^{2}} + \sum_{m=0}^{\infty} \sum_{n=0}^{\infty} \dot{k}_{mn} \\

\times \frac{\left[\sin(m\pi\frac{a_{2}}{a}) - \sin(m\pi\frac{a_{1}}{a})\right] \left[\sin(m\pi\frac{a_{4}}{a}) - \sin(m\pi\frac{a_{3}}{a})\right]}{(a_{2} - a_{1})(a_{4} - a_{3})} \\

\times \frac{\left[\sin(n\pi\frac{b_{2}}{b}) - \sin(m\pi\frac{b_{1}}{b})\right] \left[\sin(m\pi\frac{b_{4}}{b}) - \sin(m\pi\frac{b_{3}}{b})\right]}{(b_{2} - b_{1})(b_{4} - b_{3})} \tag{25}$$

where  $\dot{\Gamma}_N = \partial \Gamma_N/\partial T_\ell$ ,  $\dot{\beta}_N = \partial \beta_N/\partial T_\ell$ , and  $\dot{k}_{mn} = \partial k_{mn}/\partial T_\ell$ . Expressions for  $\Gamma_N$ ,  $\beta_N$ ,  $k_{mn}$  for all-depth contacts have been derived in [15]. The calculation of the derivatives can be found in the Appendix.

The first term of (25) can be easily calculated from the formulae in the Appendix, while the second term can be efficiently computed using the DCT by replacing  $k_{mn}$  with  $k_{mn}$  in (14). The DCT can be computed for each location in the grid and repeated for all parameters  $T_\ell, \ell=1,\cdots,N_T$ , where  $N_T$  is the number of technology parameters considered. Notice that this calculation need be performed **only once** for a given substrate structure.

To generate matrices  $\partial \mathbf{c}/\partial T_\ell$  and  $\partial \mathbf{P}/\partial T_\ell$ , it is necessary to compute sensitivities  $\partial p_{ij}/\partial T_\ell$  and  $\partial c_{ij}/\partial T_\ell$  for all pairs of partition elements composing each contact. Every sensitivity measure requires additional  $N\times N$  storage. As an example, assume  $N_T=10$ , i.e., ten technology parameters  $T_\ell$  are considered; moreover, assume that a grid of  $1024\times 1024$  points is used. Then the total storage needed by our approach is 41.9 MByte, which is relatively low considering that a  $1-\mu m$  resolution would be achieved on a  $1\times 1$  mm chip size.

#### B. Constraint Generation for Substrate Parasitic Effects

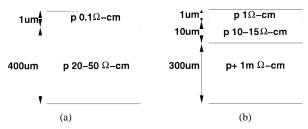

Constraint generation in a strict sense requires that parasitics be entities associated with one or more physical structures of the layout. In the case of switching noise, the physical location and transmissions paths through the substrate may not be known before floorplanning. For this reason, the constraint generation process cannot take place before the layout is, at least in part, generated, i.e., when constraints are mostly needed. To address this issue we introduce the concept of *local noise generators*. A local noise generator is defined as a voltage or current source producing the equivalent of the cumulative noise contributed to by the real noise generators located in the substrate. The generator should simulate as closely as possible the waveform felt at an arbitrary location, including distortions, attenuations, and group delays which transformed the original noise signal.

Consider sensing node n (see Fig. 7). Let us call  $g_n(t, \mathbf{\Pi})$  a waveform felt at n, where t is the time and  $\mathbf{\Pi}$  is a vector of all

<sup>&</sup>lt;sup>3</sup>This term can be computed numerically in an efficient manner, during circuit simulation.

Fig. 7. The principle and modeling of local generators.

the parameters relevant to it. Let us define  $G_n$  as a local noise generator producing waveform  $g_n$ . Due to the diverse nature of its parameters,  $\Pi$  can be split into its basic components  $\Pi = [\mathbf{W}^T \ \mathbf{G}^T \ T \ V_0]^T$ . W represents process-dependent and  $\mathbf{G}$  layout-related parameters, T is the temperature, and  $V_0$  the local substrate potential. One can also define vector  $\Delta \Pi = [\Delta \mathbf{W}^T \ \Delta \mathbf{G}^T \ \Delta T \ \Delta V_0]^T$  as the variation of  $\Pi$  from nominal. Consider performance measure  $K_i$ , its degradation from nominal is given by the product of the ith row of sensitivity matrix  $\mathbf{S}_{\Pi}$  and vector  $\Delta \Pi$

$$\Delta K_i = (\mathbf{S}_{i,\mathbf{\Pi}})^T \mathbf{\Delta} \mathbf{\Pi} \tag{26}$$

where vector  $\mathbf{S}_{i,\mathbf{\Pi}} = [\mathbf{S}_{i,\mathbf{W}} \ \mathbf{S}_{i,\mathbf{G}} \ \mathbf{S}_{i,T} \ \mathbf{S}_{i,V_0}]^T$  represents the sensitivity of  $K_i$  with respect to all the parameters of interest. Suppose now that the exact waveform felt at n is not available, and only an estimate can be derived. Moreover, suppose that a range can be set for  $\mathbf{\Pi}$  such as  $\mathbf{\Pi}^{(\min)} \leq \mathbf{\Pi} \leq \mathbf{\Pi}^{(\max)}$ . Assuming that  $\mathbf{S}_{i,\mathbf{\Pi}}$  exists and has been computed, bounds on all parameter variations  $\Delta\mathbf{\Pi}^{(\text{bound})}$  can be calculated using, for example, constrained optimization as shown in [18]. Hence, the amount of noise at the sensing nodes can be constrained a priori, without a precise knowledge of the structure of the layout being built.

Let us now generalize the problem by considering a large number of sensing nodes. From a theoretical standpoint, at each receptor a different waveform could be felt. However, since the size of the analog section of a mixed-signal circuit is small compared to the distance to the noise sources, it is assumed that all the substrate nodes are reached by an identical waveform at different times. Suppose M sensing nodes exist, each of them connected to a local generator  $G_m(t-\tau_m, \Pi_m)$ , with  $m=1,\cdots,M$ , where  $\tau_m$  is the propagation delay between nodes. Due to the highly nonlinear dependence of performance on phase, an additive linearization around a nominal value could inaccurately model the parasitic effects of substrate.

The problem can be effectively addressed by deriving a set of worst-case sensitivities as described in [19]. Call  $\Pi'$  the array of all design parameters for which  $K_i$  is not strongly nonlinear and  $\bar{\mathbf{S}}$  the corresponding sensitivity matrix. Hence, the total linearized worst-case variation of  $K_i$ , due to node m, is derived as

$$\Delta K_i|_m = \left(\bar{\mathbf{S}}_{i,\mathbf{\Pi}'_m}\right)^T \Delta \mathbf{\Pi}'_m. \tag{27}$$

Fig. 8. Evaluation of constraint violations.

Using the same formalism of (26) and considering all the sensing nodes m in the circuit, we can define the matrices

$$\bar{\mathbf{S}}_{i,\mathbf{\Pi}'} = \begin{pmatrix} \left(\bar{\mathbf{S}}_{i,\mathbf{\Pi}'_0}\right)^T \\ \vdots \\ \left(\bar{\mathbf{S}}_{i,\mathbf{\Pi}'_{M-1}}\right)^T \end{pmatrix} \quad \text{and} \quad \Delta\mathbf{\Pi}' = \begin{pmatrix} (\Delta\mathbf{\Pi}'_0)^T \\ \vdots \\ (\Delta\mathbf{\Pi}'_{M-1})^T \end{pmatrix}.$$

(28)

Thus, the degradation of performance  $K_i$  is expressed as

$$\Delta K_i = \operatorname{trace}(\bar{\mathbf{S}}_{i,\Pi'} \Delta \Pi'). \tag{29}$$

Equation (29) models the contributions of all sensing nodes onto performance  $K_i$ . Bounds on the parameters associated with each sensing node  $\Delta\Pi_n^{\text{(bound)}}$  can be computed using constrained optimization provided that conservative upper and lower bounds on the realization of  $\Pi$  are also available for each sensing node n.

The use of worst-case sensitivity matrix  $\bar{\mathbf{S}}_{i,\mathbf{\Pi}'}$  has the advantage of reducing the parameter space of  $\mathbf{\Pi}$ . Moreover, nonlinear behavior in a certain range of performance can be accurately modeled.

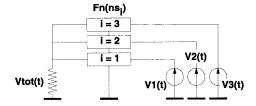

Due to the mechanism of noise modeling obtained using local generators, constraints on noise parameters can be derived independently of a particular IC process. Hence, constraint generation is required only once for a given circuit. During physical assembly, process-dependent substrate extraction, in combination with estimates of the sources of switching noise, is used to enforce the bounds. Furthermore, the effect of substrate noise can be evaluated locally, taking into consideration neither the exact floorplan nor the actual position of the noise sources. Once the substrate has been extracted, a transfer function  $F_n(ns_i)$  can be computed relating each noise source  $ns_i$  to receptor n. Assuming that approximations or exact waveforms are known for each noise source, waveform  $g_n(t, \mathbf{\Pi}_n)$  and the corresponding parameter  $\mathbf{\Pi}_n$  can be easily evaluated for each node n. Thus a simple check can be performed to verify that constraints  $\Delta\Pi_n^{(\text{bound})}$  and consequently the original specifications have been met (see Fig. 8).

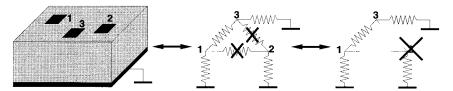

Fig. 9. Sensitivity of resistive macro-model from transformation of a componenet and its contacts.

## C. Substrate Transport Evaluation in Iterative Algorithms

Due to its "global" effects felt everywhere in the chip, substrate noise cannot be translated into a compact analytical model accounting for the entire substrate area. Hence, even if a small incremental modification is performed on the chip, the whole substrate analysis needs to be reevaluated. Unlike traditional approaches based on FDM's, SUBRES exploits the locality of incremental changes avoiding the resolution of the entire substrate at each optimization iteration. The techniques proposed hereafter are designed for very fast estimation of variations and trends within computationally expensive algorithms.

The first technique exploits the fact that small adjustments in the configuration of layout elements results in a small change in the coefficient of potential matrix  ${\bf P}$ . Let  ${\bf P}'$  be the potential matrix associated with the new configuration. Note that in  ${\bf P}'$ , only row r and column c will differ from  ${\bf P}$ . Let  $\delta {\bf P}_r$ , be the rth row and  $\delta {\bf P}_c$  the cth column of  ${\bf P}'$ , then  ${\bf P}'={\bf P}+\delta {\bf P}_c+\delta {\bf P}_r$ . For simplicity, consider only the modification due to  $\delta {\bf P}_r$ . Using the Sherman–Morrison formula,  ${\bf P}'^{-1}$  can be computed directly as

$$\mathbf{c}' = \mathbf{P}'^{-1} = \mathbf{c} + \delta \mathbf{c}, \text{ with } \delta \mathbf{c} = -\frac{\mathbf{c}_{.r}(\mathbf{c}\delta \mathbf{P}_{r.})}{1 + \delta \mathbf{P}_{r.}\mathbf{c}_{.r}}$$

(30)

where  $\mathbf{c}_{.r}$  is the rth column of  $\mathbf{c}$ . The computation of the entire resistive network is dominated by the Sherman–Morrison update, completed in  $O(N^2)$  time for each contact partition being moved.

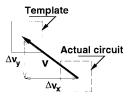

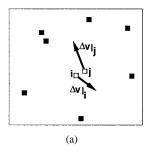

The second technique, known as *Gradient Based Method*, is based on the concept of *sensitivity to relocation*. Suppose that a contact or a collection of contacts z is to be relocated on the substrate surface from location  $\mathbf{x}_0$  to  $\mathbf{x}_k$  going through intermediate locations  $\mathbf{x}_1, \dots, \mathbf{x}_{k-1}$  (see Fig. 9). One can easily show that

$$[\mathbf{c}]_k = [\mathbf{c}]_0 + \sum_{n=1}^k [\delta \mathbf{c}]_n$$

where  $[\mathbf{c}]_0$  is the coefficient of induction matrix associated with location  $\mathbf{x}_0$ , and  $[\delta \mathbf{c}]_{n+1} = [\mathbf{c}]_{n+1} - [\mathbf{c}]_n$  is the (n+1)th update of  $\mathbf{c}$ . The updates  $[\delta \mathbf{c}]_{n+1}$  can be computed using the Sherman–Morrison formula in  $O(N^2)$  time.

To further speed up the computation, one can exploit the "gradient" information of resistive and conductive networks  $\mathbf{R}$  and  $\mathbf{Y}$ , contained in  $[\delta \mathbf{c}]_1$ . Assume that a single contact z is relocated in direction  $\mathbf{v}$  by an amount  $|\mathbf{v}| \to 0$ . Let us

Fig. 10. Computation of update matrix  $\delta c$  based on contact displacement relative to template.

define the vector  $\nabla_{\mathbf{v}}\mathbf{Y}$  to be

$$\nabla_{\mathbf{v}}\mathbf{Y} = [\mathbf{A} \quad \mathbf{B}]^T$$

where  $\mathbf{A} = \partial \mathbf{Y}/\partial v_x$ ,  $\mathbf{B} = \partial \mathbf{Y}/\partial v_y$ , and  $\mathbf{v} = [v_x v_y]^T$ . The components of matrix  $\mathbf{A}$  are defined as  $A_{ij} = \partial \mathbf{Y}_{ij}/\partial \mathbf{v}_x$ , those of  $\mathbf{B}$  as  $B_{ij} = \partial \mathbf{Y}_{ij}/\partial \mathbf{v}_y$ . Recall that, since  $N_c = N$ ,  $Y_{ij}$  is defined as the mutual conductance between contact partitions i and j for a given substrate configuration and that  $Y_{ii}$  is the ground conductance of i. The minimum step size in x- and y-direction corresponds to a unit of the grid of the DCT. Hence, matrix  $\partial \mathbf{Y}/\partial \mathbf{v}_{\mathbf{x}}$  can be approximated by first computing differences  $\delta p_{i,j\pm 1}$  and  $\delta p_{i\pm 1,j}$  using

$$\delta p_{i,j\pm 1} = p_{i,j\pm 1} - p_{i,j}$$

, and  $\delta p_{i\pm 1,j} = p_{i\pm 1,j} - p_{i,j}$ . (31)

Then, each component  $\partial Y_{ij}/\partial v_x$  is calculated by replacing term  $c_{ij}$  with  $\delta c_{i,j+1}$  in (4), (5), (8), and (9). Notice that term  $\delta c_{i,j+1}$  is derived directly from matrix  ${\bf c}$  and  $\delta p_{i,j+1}$  using the Sherman–Morrison formula. Moreover, the direct replacement of  $c_{ij}$  in the equations is legitimated by the fact that all manipulations are linear. The same method is used to derive  $\partial {\bf Y}/\partial v_y$ . The time complexity of the operation is  $O(N^2)$  since the Sherman–Morrison formula needs to be repeated for all the contacts or partitions involved in the move.

Let us assume that  $\partial \mathbf{Y}/\partial v_x$  and  $\partial \mathbf{Y}/\partial v_y$  have been computed at the zeroth step of our incremental algorithm. Call  $[\partial \mathbf{Y}/\partial v_x]_0$  and  $[\partial \mathbf{Y}/\partial v_y]_0$  these matrices. Assuming that the moving partition, contact, or collection of contacts remains close enough to its position at step 0, then the conductance matrix at steps  $1 \leq n \leq k$  can be approximated as

$$[\mathbf{Y}]_{n} \approx [\mathbf{Y}]_{0} + \left[\frac{\partial \mathbf{Y}}{\partial v_{x}}\right]_{0} \Delta v_{x} + \left[\frac{\partial \mathbf{Y}}{\partial v_{y}}\right]_{0} \Delta v_{y}$$

$$= [\mathbf{Y}]_{0} + \left[\nabla_{\mathbf{v}} \mathbf{Y}^{\mathbf{T}}\right]_{0} \Delta \mathbf{v}$$

(32)

where  $\Delta \mathbf{v} = [\Delta v_x, \Delta v_y]^T$  is the vector representing the move of contact or partition z from step 0 to n.

The Green's Function and its DCT are well behaved functions everywhere in the workspace [15]. Hence, necessarily terms  $\delta p_{i,j\pm 1} < \infty$  and  $\delta p_{i\pm 1,j} < \infty$ . No "high-frequency" components are present in the function, making it an ideal candidate for a highly accurate use of a gradient-based method. In fact, in our experiments the method has shown a 1% accuracy when the move occurred in the vicinity (less than five steps away) of the position at step 0, while a 10% accuracy was reached when the move was up to one-tenth of the chip size.

## D. Template-Based Substrate Extraction

In Section II a technique was presented to speed-up the extraction process and to simplify the schematic based on the

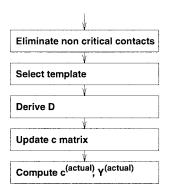

Fig. 11. Block diagram of the template-based substrate extraction algorithm.

knowledge of contact loading. In this section we discuss a method for further reduction of the extraction time of large circuits that share a set of recurring contact patterns.

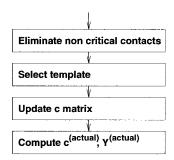

Fig. 11 illustrates the technique through a block diagram. First, a set of templates with  $N_c$  or more contacts, for which an extracted schematic exists, is compared to the sample layout. Among the available ones, a template is selected and its precomputed coefficient of induction matrix  $\mathbf{c}^{\text{(template)}}$  is used to compute  $\mathbf{c}^{\text{(actual)}}$ , the matrix associated with the actual circuit. Each progressive update matrix  $\delta \mathbf{c}$  is computed based on the displacement  $\mathbf{v} = [\Delta v_x \ \Delta v_y]^T$  of each contact nonoverlapping exactly with a corresponding contact in the template, as shown in Fig. 10. Finally, the partial conductance matrix  $\mathbf{Y}^{\text{(actual)}}$  is computed directly from  $\mathbf{c}^{\text{(actual)}}$  using (15)

$$\mathbf{Y}^{(\text{actual})} = \mathbf{X}^{\mathbf{T}} \mathbf{c}^{(\text{actual})} \mathbf{X}. \tag{33}$$

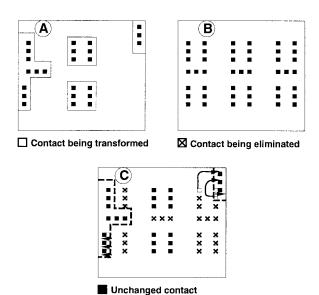

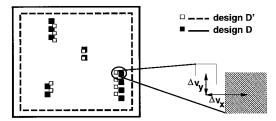

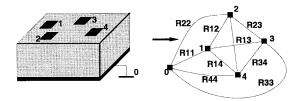

Fig. 12(A) shows an example of physical layout being extracted. The template selected for this circuit is shown in Fig. 12(B). The procedure of eliminating and aligning some of the contacts of the template onto the actual circuit is shown in Fig. 12(C). In order to derive bounds on the time complexity of the procedure, consider the following cases. First, assume the worst-case scenario, i.e., no contact exists which overlaps exactly with a contact in the template. In this case, N updates are needed for complete substrate evaluation, the resulting complexity is therefore  $O(N^3)$ . This case is equivalent to a full inversion of matrix P, hence no improvement is achieved over the nonsimplified substrate extraction. Second, consider the case in which the sample and the template are identical. In this case no computation is needed, hence the extraction complexity is zero. The second scenario, or one as near as possible to it, is most desirable.

Since the complexity of computing an update of matrix  ${\bf c}$  is independent of the transformation involved, an effective criterion for selecting the template is one aimed at maximizing  $N_o$ , the number of contacts exactly overlapping a contact in the actual circuit layout. Consequently, assuming that  $N_o < N$  contacts differ in location from corresponding contacts of a template, the complexity of the procedure could be a fraction of that needed to invert  ${\bf P}$ .

In real circuits, however, a large number of contacts rarely overlaps to those on the template. To cope with this problem, we propose a criterion based on performance sensitivities for the template selection and the minimization of updates needed for full extraction given predefined accuracy constraints. The

Fig. 12. Speed-up mechanism for the extraction of large substrates.

modified template-based substrate extraction algorithm is described in Fig. 14. For simplicity but without loss of generality, let us consider only one performance function K. Assume that the matrix  $S_{Y_{ij}}$  of the sensitivities of K with respect to all partial conductances  $Y_{ij}$  has been computed or estimated. Moreover, assume that estimates exist for the maximum values of all substrate conductances. 4 Using a fraction of the specified maximum degradation of K as threshold, all conductances, whose cumulative effect on performance is lower than the threshold, are eliminated from the schematic. All nodes connected to one or zero conductances are also eliminated as illustrated in Fig. 13. The resulting substrate configuration must be then compared with a set of templates and the best template must be selected. This problem is solved using optimization. A by-product of the selection procedure is the set D of all contacts that need be extracted in all details. The displacements of the contacts in D, relative to the selected template, are identified, and updates needed for the computation of c<sup>(actual)</sup> are computed using the Sherman–Morrison formula. Partial conductance matrix  $\mathbf{Y}^{(\mathbf{actual})}$  is finally derived directly from  $\mathbf{c}^{(\mathbf{actual})}$  using (33).

Hereafter, the template selection procedure is illustrated. Let us consider matrix update  $\delta \mathbf{c}|_i$  representing the move of contact i from its location in the template to that of the actual circuit. The coefficient of induction matrix  $\mathbf{c}^{(\mathbf{actual})}$  associated with the actual circuit is computed as

$$\mathbf{c}^{(\text{actual})} = \mathbf{c}^{(\text{template})} + \sum_{i \in D} \delta \mathbf{c} \bigg|_{i}$$

(34)

where D is the set of all the contacts whose locations in the template and in the actual circuit are nonidentical and hence need to be extracted in full detail. Combining (34) and (33),

<sup>&</sup>lt;sup>4</sup>Rough estimates of the maximum/minimum value of substrate conductances can be easily computed from a simple set-up of two contacts located at chip edges or in close proximity.

Fig. 13. Elimination of all noncritical conductances and contacts.

Fig. 14. Block diagram of the modified template-based substrate extraction algorithm.

one obtains

$$\mathbf{Y}^{(\text{actual})} = \mathbf{Y}^{(\text{template})} + \sum_{i \in D} \mathbf{X}^{\mathsf{T}} \delta \mathbf{c} \bigg|_{i} \mathbf{X}$$

(35)

where  $\mathbf{Y}^{(template)} = \mathbf{X}^T \mathbf{c}^{(template)} \mathbf{X}$  is the precomputed partial conductance matrix of the template. Let us define the error matrix, i.e., the update needed to translate  $\mathbf{Y}^{(template)}$  into  $\mathbf{Y}^{(actual)}$ , as

$$\epsilon = \mathbf{Y}^{(\text{actual})} - \mathbf{Y}^{(\text{template})} = \sum_{i \in D} \epsilon \bigg|_{i}$$

(36)

where  $\epsilon|_i = \mathbf{X}^{\mathbf{T}} \delta \mathbf{c}|_i \mathbf{X}$  is the error matrix due to the displacement of contact i in the actual circuit relative to the template.<sup>5</sup> Assume one could calculate  $\epsilon|_i$ ,  $\forall i \in D$  a priori. Using the sensitivity<sup>6</sup> of performance K with respect to matrix  $\mathbf{Y}$ , performance degradation  $\Delta K$  due to the displacement of contacts in the actual circuit relative to the template can be calculated as

$$\Delta K = \mathbf{e}^T \left( \frac{\partial K}{\partial Y_{ij}} \odot \epsilon \right) \mathbf{e}$$

(37)

where **e** is an  $N \times 1$  unity vector such that  $\mathbf{e} = [1, \dots, 1]^T$ . The  $\odot$  operator is defined as follows:  $\mathbf{A} = \mathbf{B} \odot \mathbf{C} \Leftrightarrow a_{ij} = b_{ij}c_{ij}$ . Combining (36) and (37), one obtains

$$\Delta K = \sum_{i \in D} \mathbf{e}^T \left( \frac{\partial K}{\partial Y_{ij}} \odot \epsilon \Big|_i \right) \mathbf{e}.$$

Let us define weighted extraction inaccuracy  $A_K$  of an extracted schematic with respect to performance K as the relative amount by which K varies if some or all parasitics are

inexactly estimated. The weighted extraction inaccuracy is expressed as

$$A_K = \frac{|\Delta K| + \epsilon_p + \epsilon_r}{K_v} \tag{38}$$

where  $\epsilon_p$  and  $\epsilon_r$  are the errors due to inaccurate parasitic and performance models, respectively, and  $K_v$  is the nominal performance value. Moreover, (38) reduces to  $A_K \approx \frac{|\Delta K|}{K_v}$  if  $\epsilon_p + \epsilon_r + \ll |\Delta K|$ . Suppose now that a constraint on the weighted accuracy  $\overline{A}_K$  has been set

$$A_K \le \bar{A}_K. \tag{39}$$

Then, (38) and (39) can be used as a criterion for selecting the appropriate template Problem (40) is *guaranteed* to have

$$\begin{array}{c} \textit{minimize: } D \\ \text{all templates} \end{array} \tag{40}$$

subject to

$$A_K \leq \bar{A}_K.$$

a solution, since a template with at least  $N_c$  contacts, all of them not overlapping with the actual circuit's contacts, exists by construction. Hence, arbitrarily small values of  $A_K$  can be achieved by simply extending D to include all the contacts  $i, 1 \leq i \leq N_c$ . Problem (40) is solved by exhaustively calculating the minimum set D needed for each template for a given inaccuracy  $A_K$ . The procedure of calculating  $A_K$  and D has a time complexity of  $O(N^2)$ , while the overhead of computing  $S_{Y_{ij}}$  is generally not accounted for since the evaluation is performed beforehand during circuit synthesis. Hence, a circuit with  $N_c$  contacts and a specification on  $A_K$  (39) can be extracted in  $O([N_T + |D|]N^2)$  time, where  $N_T$  is the number of template circuits and |D| the size of set D.

The final issue to be addressed is the efficient calculation of estimate  $\epsilon|_i$ , which can be computed exactly from update  $\delta \mathbf{c}|_i$  using mapping  $\mathbf{X}$  of (35). However, a more efficient computation of  $\epsilon|_i$  can be obtained using the approximation of (32). Consider all the contacts  $i \in D$ , assume that the locations of i in the template and in the actual circuit are *close enough*. Then, a 2-D Taylor expansion for  $\delta \mathbf{c}|_i$  can be constructed as

$$\delta \mathbf{c}|_{i} \approx \frac{\partial \mathbf{c}}{\partial v_{x}}\Big|_{i} \Delta v_{x} + \frac{\partial \mathbf{c}}{\partial v_{y}}\Big|_{i} \Delta v_{y} = \nabla_{\mathbf{v}} \mathbf{c}|_{i} \Delta \mathbf{v}|_{i}$$

(41)

where vector  $\Delta \mathbf{v}|_i = [\Delta v_x \ \Delta v_y]^T$  represents the displacement needed to bring i from the template location to the location in the actual circuit. Term  $\nabla_{\mathbf{v}} \mathbf{c}|_i = [\frac{\partial \mathbf{c}}{\partial v_x}|_i, \frac{\partial \mathbf{c}}{\partial v_y}|_i]^T$  is calculated using the Sherman–Morrison formula as in (32) and is valid for *small* displacements of contact i. Assume

<sup>&</sup>lt;sup>5</sup>Assume all the other contacts are **not** displaced.

<sup>&</sup>lt;sup>6</sup>The sensitivity of K with respect to matrix  $\mathbf{Y}$  is an  $N_c \times N_c$  matrix, whose terms in the ith row and jth column are given by the expression  $\partial K/\partial Y_{ij}$ .

Fig. 15. (a) Displacement of contacts i and j in a single landscape. (b) Partitioning of substrate to minimize the number of different contaacts for which  $\nabla_{\mathbf{v}} \mathbf{c}$  need be computed explicitly.

now that there exists a contact j in the vicinity of i which is displaced by  $\Delta \mathbf{v}|_j$ , where  $|\Delta \mathbf{v}|_j|$  is also *small*. Assuming that the surrounding objects' relative distances from i and j are similar, one can estimate the cumulative effects of the displacement of the contacts as

$$\delta \mathbf{c}|_{i,j} \approx \nabla_{\mathbf{v}} \mathbf{c}|_i \Delta \mathbf{v}|_i + \nabla_{\mathbf{v}} \mathbf{c}|_i \Delta \mathbf{v}|_j$$

(42)

where vectors  $\Delta \mathbf{v}|_i$  and  $\Delta \mathbf{v}|_j$  relate to the displacements of i and j as shown in Fig. 15(a). Ideally, one would like to be able to compute  $\mathbf{c}|_i$  using (42) for each contact  $i=1,\cdots,N_c$ . However, far contacts "see" a completely different landscape, which causes term  $\delta \mathbf{c}|_i$  to change by moving within the workspace. To improve the accuracy of (42), one could partition the workspace in order to minimize the number of contacts for which a new  $\nabla_{\mathbf{v}}\mathbf{c}$  needs be computed. Fig. 15(b) shows such a partitioning. Notice that only one contact per partition, the pole, is used for the computation of  $\nabla_{\mathbf{v}}\mathbf{c}$ .

The problem of minimizing the number of partitions of Fig. 15(b) can be time-consuming, since it requires the estimation of each contact displacement to select the best candidates for the partitions and its poles. The complexity of this partitioning would nullify the efforts for an efficient substrate extraction. In addition, the needed parasitic estimate accuracy  $\epsilon_p$  in (38) is not high. Hence, in our experiments a single contact was used to estimate  $\delta \mathbf{c}|_i, \forall i$  with an error of 50% or less. Moreover, this error could be modeled as term  $\epsilon_p$  in (38) and hence accounted for while determining D.

#### IV. APPLICATIONS

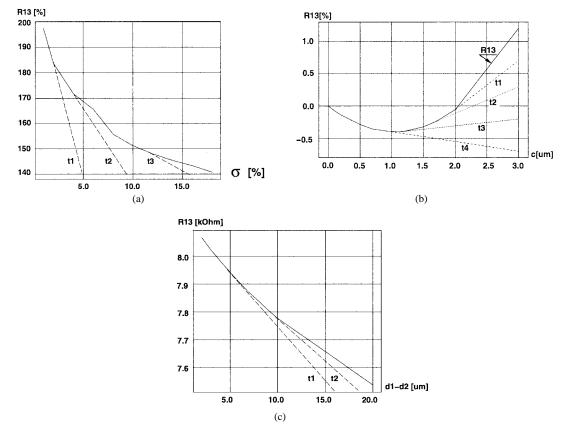

# A. Scaling and Technology Migration

Let us consider the scaling or technology migration for a given design (see Fig. 16). Redesign generally involves scaling in x- and y-directions, while technology migration involves a three-dimensional (3-D) scaling. Hereafter, we propose a generalized technique that can be used for both 2-D and 3-D scaling.

Consider first scaling in z-coordinate. Using (22)–(25),and the expressions in the Appendix, one can efficiently compute matrix  $\partial \mathbf{Y}/\partial T_\ell$ . Let us define a number of technology parameters for some design  $\mathcal{D},\,T_\ell^{(\mathcal{D})},\,\ell=1,\cdots,N_T$ , which include layer thicknesses or profile discretizations  $d_k,\,k=1,\cdots,N_d$  in Fig. 3 and permittivity  $\epsilon_k,\,k=1,\cdots,N_\epsilon$ . Call  $\mathbf{T}^{(\mathcal{D})}$  the  $N_T\times 1$  vector whose elements are the  $T_\ell^{(\mathcal{D})}$  terms.

Fig. 16. (a) Two-dimensional scaling in redisign. (b) Three-dimensional scaling in technology migration.

Fig. 17. Scaling in x- and y-directions. Relocation of contacts and area scaling.

Suppose now that conductance matrix  $\mathbf{Y}^{(\mathcal{D})}$  has been calculated for a set of parameters  $\mathbf{T}^{(\mathcal{D})}$ . In addition, assume that an array of parameters  $\mathbf{T}^{(\mathcal{D}')}$ , associated with a new design  $\mathcal{D}'$ , is also available. Define the  $N_T \times 1$  vector  $\Delta \mathbf{T}^{(\mathcal{D}\mathcal{D}')} = \mathbf{T}^{(\mathcal{D}')} - \mathbf{T}^{(\mathcal{D})}$  as the variation of technology parameters across designs  $\mathcal{D}$  and  $\mathcal{D}'$ . Conductance matrix  $\mathbf{Y}^{(\mathcal{D}')}$ , associated with the new design, can be computed using a first-order Taylor expansion as

$$\mathbf{Y}^{(\mathcal{D}')} \approx \mathbf{Y}^{(\mathcal{D})} + \sum_{\ell=1}^{N_T} \left[ \frac{\partial \mathbf{Y}}{\partial \mathbf{T}_{\ell}} \right]_{\mathbf{T}_{\ell}^{(\mathcal{D})}} \Delta \mathbf{T}_{\ell}^{(\mathcal{D}\mathcal{D}')}$$

(43)

provided that designs  $\mathcal{D}$  and  $\mathcal{D}'$  are close enough, i.e.,  $\max_{\ell}\{|\Delta T_{\ell}^{(\mathcal{D}\mathcal{D}')}|/T_{\ell}^{(\mathcal{D})}\}$  is small. Consider next scaling in (x,y)-direction. Assume that a contact i in design  $\mathcal{D}$  is located at a point  $\mathbf{v_i}^{(\mathcal{D})} = [v_x,v_y]^T$ , while a contact's position in design  $\mathcal{D}'$  is  $\mathbf{v_i}^{(\mathcal{D}')}$ . Furthermore, assume the contact's area is not significantly changed across designs. Suppose that conductance matrix  $\mathbf{Y}^{(\mathcal{D})}$  has been calculated for design  $\mathcal{D}$  and that vectors  $\mathbf{v_i}^{(\mathcal{D})}$  and  $\mathbf{v_i}^{(\mathcal{D}')}$  are given  $\forall i=1,\cdots,N_c$ . Let  $\Delta\mathbf{v_i}^{(\mathcal{D}\mathcal{D}')}$  be the change in location for contact i as illustrated in Fig. 17. Using (32), one can approximate matrix  $\mathbf{Y}$  as follows:

$$\mathbf{Y}^{(\mathcal{D}')} \approx \mathbf{Y}^{(\mathcal{D})} + \sum_{i=1}^{N_{c}} [\nabla_{\mathbf{v}} \mathbf{Y}]^{\mathbf{T}} \Delta v_{i}^{(\mathcal{D}\mathcal{D}')}.$$

(44)

Equations (43) and (44) can be combined so as to account for 3-D scaling realistically.

## B. Technology Selection Based on Nondeterministic Data

In the above discussion, we have assumed that the values of technology variations  $\Delta T_{\ell}$  and geometric displacements  $\Delta v_i$

are of a deterministic nature. Suppose on the contrary that we are given the statistical behavior of all or some technology parameters  $\Delta T_\ell$ ,  $\forall \ell=1,\cdots,N_T$ . Assume that the terms  $\Delta T_\ell$  are random variables with mean  $\mu_\ell$  and variance  $\sigma_\ell^2$ , moreover suppose that all  $\Delta T_\ell$  are statistically independent.

Then, the mean  $E(Y_{ij})$  and variance  $\sigma^2(Y_{ij}) = E(Y_{ij}^2) - E^2(Y_{ij})$  of each entry of conductance matrix **Y** can be computed as

$$E(Y_{ij}) \approx Y_{ij}^{(\mathcal{D})} + \sum_{\ell=1}^{N_T} \left[ \frac{\partial Y_{ij}}{\partial T_{\ell}} \right]_{T_{\ell}^{(\mathcal{D})}} \mu_{\ell}$$

$$\sigma^2(Y_{ij}) \approx \sum_{\ell=1}^{N_T} \left| \left[ \frac{\partial Y_{ij}}{\partial T_{\ell}} \right]_{T_{\ell}^{(\mathcal{D})}} \right|^2 \sigma_{\ell}^2$$

(45)

where  $[\partial Y_{ij}/\partial T_{\ell}]_{T_{\ell}^{(\mathcal{D})}}$  is the sensitivity of entry  $Y_{ij}$  with respect to  $T_{\ell}$  related to the original design  $\mathcal{D}$ .

Our sensitivity-based method for the computation of mean and variance of  $\mathbf{Y}$  can also be used for the selection of a technology which is most suitable for a certain circuit and its associated performance specifications. Suppose, for instance, that  $N_p$  constraints on all critical substrate coupling  $R_{ij}^{(\mathrm{bound})}$  have been computed using the techniques presented in [18]. Furthermore, assume that a number of technologies  $\mathcal{T}$  is available and that all relevant parameters  $T_\ell^{(T)}$  are identified. Suppose, however, that for some or all technologies, a number of parameters are not known precisely and only rough estimates with uncertainty exist. Assume that estimate and uncertainty can be modeled into each parameter in terms of its mean and variance. Then, by computing the mean and the variance of  $\mathbf{R}$  for a set of parameters  $T_\ell^{(T)}$ , one can derive the probability with which constraints  $R_{ij}^{(\mathrm{bound})}$  will be met

$$P_{\mathcal{T}}\left[\mu(R_{ij}), \sigma^{2}(R_{ij}), R_{ij}^{(\text{bound})}\right] = \operatorname{erf}\left(\frac{R_{ij}^{(\text{bound})} - \mu(R_{ij})}{\sigma(R_{ij})}\right)$$

(46)

provided that  $T_\ell^{(T)}$  is Gaussian. Notice that  $\operatorname{erf}(x)$  is defined here as the integral of a normal distribution N(0,1) from minus infinity to x. The problem of selecting a technology most likely to satisfy all constraints is equivalent to maximizing  $P_T$  over all critical constraints. Due to the efficiency of our techniques for the calculation of means and variances, the problem can be solved by exhaustively computing  $P_T[\mu(R_{ij}), \sigma^2(R_{ij}), R_{ij}^{(\text{bound})}]$  for each technology T.

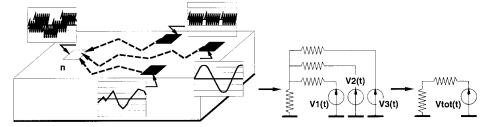

## C. Placement Problem

A substrate-aware placement methodology has been implemented in a simulated annealing (SA)-based framework with analog constraints, called PUPPY-A [20], [21]. The annealing, fully characterized by search space, cost function, move-set, and cooling schedule, is described in detail in [17, ch. 4]. Improvements on the performance degradation due to substrate-induced switching noise can be achieved by placing noise injecting and noise sensitive modules at a certain distance or by creating special structures, such as low-resistivity guard-rings, around noise injectors [15].

Fig. 18. Modeling noise injectors in the placer.

The first provision is implemented in the placer using the conventional SA move-set. The second issue is generally solved by extending the search space, allowing the annealing to choose from a number of alternative implementations for a module, including one with a guard-ring implemented around it. In this paper we restrict our attention to the first option, where our Green's Function-based substrate analysis method is used for the evaluation of the substrate at each annealing step.

In order for a placer to be effective in preventing violations to performance specifications, the following features must be implemented in the tool. First, a model for each noise injecting module must exist. The model should characterize the *waveform* and the *spatial location* where the noise is injected as precisely as possible (see Fig. 18). Second, a compact model of substrate transport should be available and efficient substrate current evaluation should be possible, independent of the circuit configuration. Third, a model for substrate noise absorption and its effect on performance should be defined.

For the purpose of physical assembly or schematic design, switching noise is often modeled as a simple signal, generally synchronized with the clock, if one is present. A number of examples of this modeling style can be found in the literature [6], [10], [22]. Alternatively, one can extract the actual noise waveform associated with a given logic circuit using event-driven simulation combined with a lookup table for the precise representation of every injection current. The method is explained in detail in [1]. In this paper we will use the results of this work applied to our examples.

For each noise injecting module j, a model is created which accurately reproduces substrate-injected noise, taking into account both impact ionization and capacitive coupling through devices and interconnect lines. The model  $V_S(\Pi_j)$  is based on a bank of independent current noise generators with a unified set of parameters, represented by vector  $\Pi_j$ . The problem of evaluating the effects of substrate on performance is approached in the following way.

- Compute constraints for node of noise-sensitive modules.

- 2) Generate resistive network associated with substrate.

- 3) Quantify violations to constraints.

The sensitivity of a given performance  $K_i$  is computed with respect to the parameters  $\Pi_j$  related to each noise source j acting on every node in the analog modules being placed. In step 1), a set of bounds  $\Pi_j^{\text{(bound)}}$  is generated for a subset of *critical nodes*  $n_c$  using constrained optimization techniques [23] and the specification on the maximum positive and negative performance degradation  $\overline{\Delta K_i}^{\pm}$ . Subset  $n_c$  is

Fig. 19. Mapping substrate onto fully connected graph  $G_S(V, E)$ .

Fig. 20. (a) Initial contact grid, (b) reshuffling of contacts at high temperatures, and (c) resulting grid at lower temperatures.

generated from the cumulative impact of all parasitic noise sources acting on each node as in [23].

In step 2) a given placement configuration is mapped onto a fully connected graph  $G_S(V,E)$ , whose vertices V are the substrate contacts and edges E are weighted by the conductance  $Y_{ij}$  or resistance  $R_{ij}$  between the corresponding vertices i and j. Fig. 19 shows the mapping procedure. The techniques for the evaluation of the edges have been described in detail in Section II. The calculation of all violations in step 3) to the given constraints is carried out by solving the circuit underlying  $G_S(V,E)$  and evaluating the appropriate parameters at each critical node.

At each stage of the annealing, only steps 2) and 3) need be repeated, since step 1) is carried out only once for each chip. The efficiency of a Green's Function-based substrate simulator, though high, is still insufficient for such computationally intensive algorithms as SA, hence, appropriate heuristics must be developed. In SA, at high annealing temperatures, considerable reshuffling is allowed on the components of the layout. Hence, the locations of switching noise generators and receptors can be significantly modified. At lower temperatures, on the contrary, modules move by lesser amounts in average. Hence, the edges of  $G_S(V, E)$  change with lower frequency and by a lesser amounts.

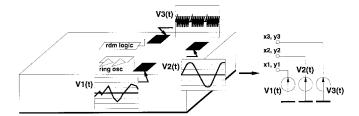

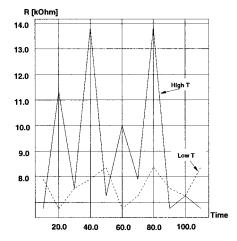

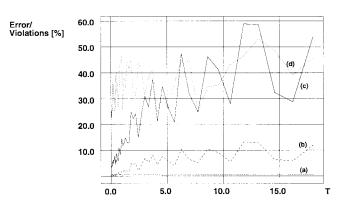

As an illustration, consider a regular 36-contact grid shown in Fig. 20(a). The plot of Fig. 21 shows the average variation of the resistive components of the substrate network

Fig. 21. Resistive network reacting to high-temperature and low-temperature contact reshuffling.

when high-temperature [Fig. 20(b)] and low-temperature [Fig. 20(c)] contact perturbations occur during the unfolding of SA. On the other hand, only when changes in the edges of  $G_S(V, E)$  reflect a significant change in any performance measure  $K_i$ , should the entire substrate network be evaluated along with the estimate of performance degradation  $\Delta K_i$ . When a new temperature  $T_k$  is reached, the full graph  $G_S(V,E)$  is solved, i.e., all the edges in V are evaluated exactly, using the Sherman-Morrison update to obtain the new matrix  $P^{-1}$ . After a new move  $m_k$  and the associated translation  $\Delta \mathbf{v} = [\Delta v_x \ \Delta v_y]^T$  is selected by the annealing algorithm, the sensitivity of the edges of  $G_S(V, E)$  can be efficiently computed using the techniques outlined in Section III-C. Suppose subset  $n_c$  of all critical receptors has been derived for the circuit; moreover, let  $n_s$  be the subset of all noise injecting nodes. Let  $[\mathbf{Y}_{\mathbf{c}}]_{m_k}$  be the conductance matrix of all the nodes in  $n_c$  and in  $n_s$  and let  $[{f \Delta Y_c}]_{m_k}$  be its update. By (32), term  $[\Delta \mathbf{Y_c}]_{m_b}$  is estimated as

$$[\mathbf{\Delta}\mathbf{Y}_{\mathbf{c}}]_{m_k} \approx [\nabla_{\mathbf{v}}\mathbf{Y}^{\mathbf{T}}]_0 \mathbf{\Delta}\mathbf{v}$$

(47)

where term  $[\nabla_{\mathbf{v}} \mathbf{Y}^{\mathbf{T}}]_0$  is defined as in (32) for matrix  $\mathbf{Y}_{\mathbf{c}}$ . After updating  $Y_c$ , the resistive network is solved and parameter  $\Pi_i$ can be evaluated for all critical nodes j. By comparing  $\Pi_i$ with the bound  $\Pi_i^{\text{(bound)}}$ , one can obtain the corresponding violation. If a violation to specifications has occurred, then a precise extraction step must be performed, and the precise value for the violation is used to drive the cost of the annealing in a manner similar to [20]. Otherwise, the contribution of substrate noise to node j in degrading performance  $K_i$  is considered negligible, and the cost function will not take it into account. The cost relative to the remaining analog-specific constraints, as well as area and wiring length, will, however, be computed. The placement algorithm is proved to converge to a global minimum under the same conditions of [24] and [25] when it is modified to account for noise substrate transport evaluation [17].

# V. CASE STUDY

The circuit used in our experiments is a 140-MHz monitor display controller (RAMDAC) including three D/A converters,

```

foreach temperature T<sub>k</sub>

evaluate_substrate_network_exactly; // use Sherman-Morrison to

undate

// configuration at equilibrium

repeat

m_k = \text{select\_move};

estimate_network_change(m_k);

// use gradient based method

foreach node i \in n_c

\Pi_i = \text{estimate\_cumulative\_noise}

if \Pi_j \geq \Pi_i^{(bound)}

evaluate_substrate_network_exactly;

go_to_next_node;

evaluate_cost_function;

accept_or_reject_move;

until equilibrium_reached

```

Fig. 22. Heuristic for the combined use of Sherman-Morrisonn and gradient-based methods.

Fig. 23. PLL schematic.

TABLE I PLL SPECIFICATIONS

|                        | Conditions      |     |           |               |

|------------------------|-----------------|-----|-----------|---------------|

| Measure                | PLL input freq. | n   | VCO freq. | Specs         |

| Stability              | 0.56 MHz        | 100 | 56 MHz    | Yes           |

|                        |                 | 250 | 140 MHz   | Yes           |

| Jitter $\triangle T/T$ | 0.56 MHz        | 250 | 140 MHz   | ≤ 0.007       |

| Ph. Margin             | =               | -   | -         | $\geq 45^{o}$ |

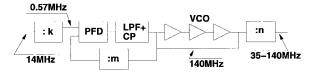

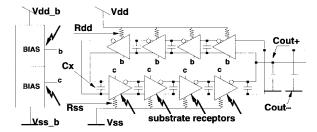

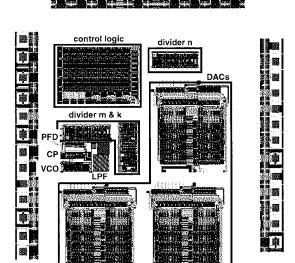

a phase lock loop (PLL) frequency synthesizer, and digital control logic. The circuit was integrated in a Mosis HP 1- $\mu$ m CMOS technology. The substrate parameters used by SUBRES are similar to Fig. 6(b) with a discretization matching the exponential doping curve. The converters were generated using dedicated silicon compilers [26]. The PLL needed particular care due to its extremely high sensitivity to thermal noise and spurious signals originated within the chip.

The PLL architecture, shown in Fig. 23, was derived from [27]. Device sizing was performed using a modified version of the supporting hyperplane algorithm and SPICE for circuit evaluation [28]. The circuit consists of a digital section, i.e., three divide-by-n modules and a phase-frequency detector (PFD), and a number of analog components, i.e., an analog low-pass filter (LPF) and a charge pump (CP). The interface between analog and digital sections is represented by the voltage-controlled oscillator (VCO), which generates a digital output at a frequency proportional to the input voltage. Typical frequencies of operation are shown in the various branches of the circuit in Fig. 23.

The specifications for the PLL are summarized in Table I. The jitter  $\frac{\Delta T}{T}$  is defined as the ratio between the variation from nominal of oscillation period  $\Delta T$  and period T. Due to the time-variance of  $\frac{\Delta T}{T}$ , it is generally measured in terms of its peak-to-peak or RMS value.

## A. Physical Design

The jitter performance of the PLL is entirely dependent on the jitter produced by the VCO. Using this fact, a sensitivity-

Fig. 24. Interconnect parasitics and substrate noise receptors

TABLE II

CONSTRAINTS OBTAINED FROM PARCAR

| Critical Parasitic | Constraint | Extracted value |

|--------------------|------------|-----------------|

| C <sub>out+</sub>  | 12.34fF    | 11.60 fF        |

| C <sub>out</sub> _ | 12.34 fF   | 11.60 fF        |

| $C_x$              | 15.84 fF   | 1.12fF          |

| $V_0 _{VCO}$       | 110mV      | 109mV           |

| $V_0 _{LPF}$       | -          | -               |

Note: only about 10% of all the parasitics need be constrained. The remaining 90% cannot be higher than the upper-bound ensured by the technology.

based model of the PLL could be constructed relating the PLL jitter performance to the level of the noise voltage peak-topeak present at some 85 critical locations in the VCO. All critical substrate noise receptors were identified in the delay elements and in the two bias circuits using SPICE simulations accounting for both impact ionization and capacitive coupling. Interconnect parasitics and IR drops were also identified (see Fig. 24). Sensitivities with respect to all parasitics (RC for interconnect and  $V_0$  for substrate receptors) were computed. Then, constraint generator PARCAR [23], [19] was used to derive a minimal set of constraints on the maximum admissible noise voltage in each one of the receptors and on the maximum R/C values for the interconnect parasitics in the VCO. The CPU time needed for the sensitivity analysis and constraint calculation was in total 2545 s, the results are shown in Table II. Interconnect parasitic constraints were exploited by a constraint-based module generator VCOGEN to synthesize the VCO. TIMBERWOLFSC-4.1 was used for the internal divider. The module generation step required a total of 163 s on a DEC AlphaServer 2100 5/250.

The next step was the placement of the component blocks of the PLL and of the other circuits in the RAMDAC. The placement was carried out using PUPPY-A. In the circuit there exist three major switching noise injectors, corresponding to the dividers. In order to accurately verify if the constraints on the maximum admissible noise voltage were violated, an accurate model was constructed of the injectors using the tool SUBWAVE [1]. SUBWAVE generates simplified substrate noise models, accounting for currents injected via capacitive coupling and impact ionization from active device areas and supply lines. For the capacitive coupling models used in SUBWAVE, we refer to [15] and [1].