# Thorough Testing of Any Multiport Memory With Linear Tests

Said Hamdioui, Member, IEEE, and Ad J. van de Goor, Fellow, IEEE

Abstract—The quality of tests, in terms of fault coverage and test length, is strongly dependent on the used fault models. This paper presents realistic fault models for multiport memories with p ports, based on defect injection and SPICE simulation. The results show that the fault models for p-port memories consist of p classes: single-port faults, two-port faults,..., p-port faults. In addition, the paper discusses the test procedure for such memories; it shows that the time complexity of the required tests is not exponential proportionally with p, as published by different authors, but it is linear, irrespective of the number of ports of which the multiport memory consists.

*Index Terms*—Fault coverage, fault models, multiport/singleport memories, spot defects, weak faults.

#### I. INTRODUCTION

**F** AST and efficient testing is an important step in any manufacturing process. The cost of testing such memories increases rapidly with every generation [1]. Precise and realistic fault modeling in order to design efficient tests, while keeping test cost and time within economically acceptable limits, are therefore essential.

A novel characteristic of today's memories is the presence of multiple ports to allow the two common operations (read and/or write) to be performed simultaneously. Testing of such *multiport* (MP) memories requires special tests since the multiple and simultaneous access can sensitize faults that are different from the conventional *single-port* (SP) memory faults.

In spite of the growing use of MP memories, little *experimental* work has been published. In [2], an *ad hoc* test with no specific fault model was described. In [3], a built-in-self-test (BIST) circuit, based on a serial interfacing technique for embedded *two-port (2P)* memories, was reported. However, the used fault models were very *simplistic*, and the proposed BIST requires a modification of the design. For the same fault models, modified march tests and BIST circuits were reported in [4]–[6]. In [7]–[10] it has been shown *theoretically* that the conventional tests for SP memories are *insufficient* for MP memories. Moreover, *theoretical* fault models, together with their tests, were developed. However, the introduced fault models are *not* based on any experimental/industrial analysis. In addition, the proposed tests have a time complexity which is exponentially proportional with the number of ports of the MP memory; that makes them

The authors are with the Laboratory of Computer Engineering, Delft University of Technology, 2628 CD Delft, The Netherlands (e-mail: said@ce.et. tudelft.nl; vdGoor@carit.et.tudelft.nl).

Publisher Item Identifier S 0278-0070(02)01047-3.

not practical. In [11], port interferences in 2P memories were *experimentally* analyzed, based on an industrial design and SPICE simulation; however, the analysis was restricted to only the interference between the bit lines and the word lines of the two ports. A similar, but theoretical work, has been reported in [12].

It can be seen from the above that little *experimental* research has been done on testing MP memories. Experimental research is required in order to develop *realistic* fault models and, thereafter, *optimal* tests. In this paper, a complete analysis of spot defects in MP memories will be presented, resulting in realistic fault models. The paper is organized as follows. Section II establishes an inventory of all possible spot defects in the memory cell array. Section III gives a description of the simulation model and methodology. Section IV derives the functional fault models based on the simulation results, which will be presented in Section V. Section VI analyzes the probabilities of occurrence of these faults. Section VII discusses the test procedure, while Section VIII ends with conclusions.

# II. CLASSIFICATION OF SPOT DEFECTS

Many faults in the memory circuit are caused by undesired particles called *spot defects (SDs)*. Depending on their conductivity, they can cause undesired connections or disconnections in the memory. They can be divided into three groups:

- Open: an extra resistance within a connection. The resistor value called R<sub>op</sub> is given by 0 < R<sub>op</sub> ≤ ∞.

- Short: an undesired resistive path between a node and V<sub>cc</sub> or V<sub>ss</sub>. The resistor value called R<sub>sh</sub> is given by 0 ≤ R<sub>sh</sub> < ∞.</li>

- Bridge: an undesired resistive path between two connections, which are not V<sub>cc</sub> or V<sub>ss</sub>. The resistor value called R<sub>br</sub> is given by 0 ≤ R<sub>br</sub> < ∞.</li>

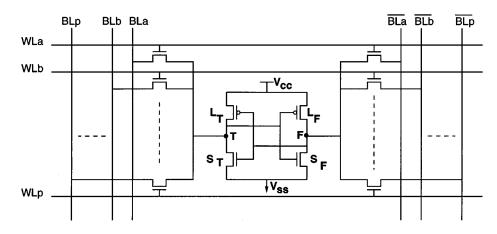

In this paper, a complete analysis of the above SDs will be done for a differential access p-port (pP) memory cell shown in Fig. 1. In order to do that, all possible SDs in the pP memory cell have to be defined and located.

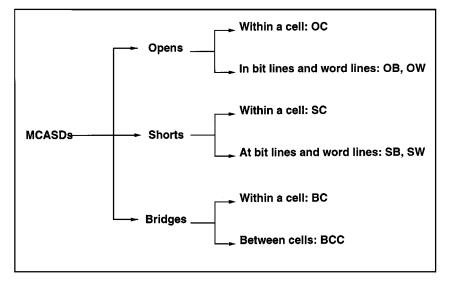

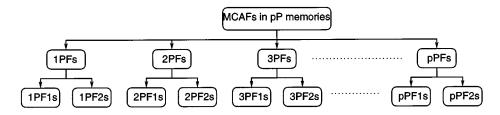

SDs can occur in any subcircuit of the memory circuit. In this paper, we will restrict ourselves to SDs in the memory cell array. Fig. 2 gives an overview of *memory cell array spot defects* (*MCASDs*). It should be noted that the discussion of SDs in this section will be done for a memory cell with any number of ports *p*.

Many SDs can be identified in a pP memory. However, due to the symmetric structure of the cell, only a subset needs to be simulated. For identifying the not-to-be simulated SDs, the following terminology will be introduced:

Manuscript received March 19, 2001. This work was supported by Intel Corporation, USA, via grants and internships. This paper was recommended by Associate Editor R. Aitken.

Fig. 1. A differential p-port memory cell.

Fig. 2. Classification of MCASDs.

- Similar behavior: A spot defect SD1 (i.e., open, short, or bridge) shows a similar behavior to SD2 if SD1 and SD2 present the same defect, but belong to different ports; e.g., a bridge between bit line  $BL_a$  and word line  $WL_b$  has a similar behavior to a bridge between bit line  $BL_b$  and word line  $WL_a$ .

- Complementary behavior: SD1 shows a complementary behavior to SD2 if SD1 and SD2 present defects in which locations in the memory cell are symmetrical to each other; e.g., a bridge between the bit lines  $BL_a$  and  $BL_b$  at the true side has a complementary behavior to a bridge between  $\overline{BL}_a$  and  $\overline{BL}_b$  at the false side. In this case, the functional fault behavior of SD1 is similar to that of SD2, with the only difference being that all 1s are replaced with 0s and vice versa. E.g., if due to the presence of SD1 the operation read 0 (r0) causes an up transition in the cell, then in the presence of SD2 the r1 operation causes a down transition in the cell.

- An SD1 (involving two cells) shows an interchanged behavior to an SD2 (involving the same two cells) if the fault behavior of SD1 is similar to that that of SD2, with the only difference being that the *aggressor cell* and the *victim cell* are interchanged; whereby, the victim cell is

the cell where the fault appears, while the aggressor cell is the cell to which the sensitizing operation (state) should be applied.

• *Interchanged complementary behavior:* SD1 shows an interchanged complementary behavior to SD2 if SD1 shows a complementary and interchanged behavior to SD2.

# A. Definition and Location of Opens

Opens in the memory cell can be classified as *opens within a cell* (denoted as *OC*) and opens at bit lines (*OB*) and at word lines (*OW*).

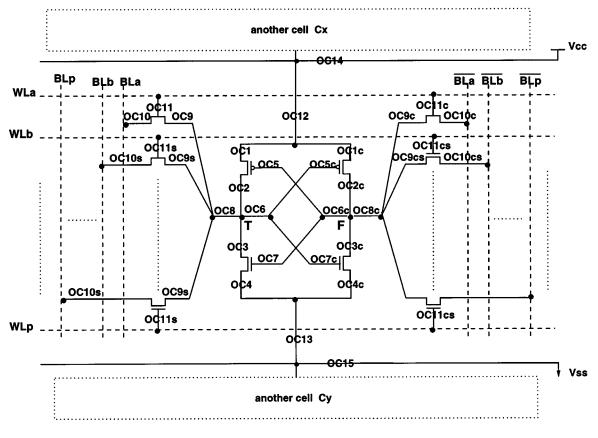

1) Opens Within a Cell: In this case, the *p*-port memory cell will be considered without bit lines and word lines to which it is connected. In order to define all possible opens, the cell will be considered as a graph in which all branches can show such a defect. Fig. 3 shows all possible locations of opens within a memory cell. Note that cells that belong to adjacent rows share the same  $V_{cc}$  or  $V_{ss}$  line and that the opens at such lines are considered as opens within a cell. Opens at locations OCx and OCxc will show complementary fault behaviors due to the symmetric structure of the memory cell, while opens at locations OCx and OCx and OCxs will show similar fault behaviors due to the fact

Fig. 3. Opens within a cell.

that the cell has p similar ports. For that reason, one can be limited to simulate opens OCx only. From these, the behavior of the opens OCxc and OCxs can be derived. The first block of Table I shows the OCs. The first column lists the OCx opens, which are the minimal set that needs to be simulated, the third column gives the number of opens within one group. A group is a set of defects having a similar and/or a complementary fault behavior (e.g., opens at the source of the pull-up transistor at the true side consist of two opens, OC1 and OC1c). Note that the total number of opens within a cell (including opens at  $V_{cc}$ and opens at  $V_{ss}$ ) is 20 + 6p, whereby p is the number of ports; note also that each port will add six possible opens to the list of opens (e.g., OC9, OC10, OC11, OC9c, OC10c, and OC11c).

The fourth column in Table I classifies the opens into single-port fault defects (SFDs) and multiport fault defects (MFDs). The SFDs are spot defects that only can cause single-port (SP) faults; they cannot cause special faults for MP memories. The SP faults are faults that can be sensitized using a single port. The MFDs are defects that can cause SP faults as well as MP faults; such faults require the use of multiple ports simultaneously in order to be sensitized. This classification is based on the simulation results done for a differential two-port (2P) memory [13], [16]; the SDs causing only SP faults in 2P memories are considered SFDs, while SDs causing SP faults as well as two-port faults (i.e., faults requiring the use of two ports simultaneously in order to be sensitized) are considered MFDs. Note that only OC3 and OC4 from Table I are MFDs. The fact that these two opens are MPDs can be explained as follows: when a single read operation is performed to the

TABLE I LIST OF OPENS

| Open              | Description                            | #        | Class |

|-------------------|----------------------------------------|----------|-------|

| OC1               | Source of pull-up at true side         | 2        | SFD   |

| OC2               | Drain of pull-up at true side          | 2        | SFD   |

| OC3               | Drain of pull-down at true side        | 2        | MFD   |

| OC4               | Source of pull-down at true side       | 2        | MFD   |

| OC5               | Gate of pull-up at true side           | 2        | SFD   |

| OC6               | Cross coupling at true side            | 2        | SFD   |

| OC7               | Gate of pull-down at true side         | 2        | SFD   |

| OC8               | Connection of the pass transistors     | 2        | SFD   |

| OC9               | Pass transistor connection to T        | 2p       | SFD   |

| OC10              | Pass transistor connection to bit line | 2p       | SFD   |

| OC11              | Gate of pass transistor at true side   | 2p       | SFD   |

| OC12              | $V_{cc}$ path of the cell broken       | 1        | SFD   |

| OC13              | $V_{ss}$ path of the cell broken       | 1        | SFD   |

| OC14              | $V_{cc}$ path shared by adjacent cells | 1        | SFD   |

| OC15              | $V_{ss}$ path shared by adjacent cells | 1        | SFD   |

| $\overline{OB}_w$ | the bit line $BL_i$ at the write side  | 2p       | SFD   |

| $OB_r$            | the bit line $BL_i$ at the read side   | 2p       | SFD   |

| OW                | the word line $WL_i$                   | <b>p</b> | SFD   |

cell, in the presence of OC3 (or OC4), a resistor divider will be formed by the pass transistor and the pull-down transistor together with OC3. If the resistance value of the defect is high enough, the voltage of the cell's node (during a read operation) will increase above the threshold voltage, and consequently the cell will flip. If two (or more) simultaneous read operations are performed, then two voltage dividers will be formed which have an additive effect on the cell's node. That means that the voltage on the node, in the presence of OC3, depends on the number of simultaneous read operations. Therefore OC3 is an MFD. Note that given the results for a 2P memory, then in order to examine a p-port memory, only the two MFDs (OC3 and OC4) need to be resimulated. This eliminates a lot of simulation work.

2) Opens at Bit Lines and Word Lines: Bit lines and word lines are connected to many cells. Therefore, an open at a bit line or a word line can influence the behavior of the operations applied to all these cells. In the following, first opens at bit lines will be discussed and thereafter at word lines.

*Opens at Bit Lines:* If we consider that the memory cell array is located between the read and the write circuit, then the opens at bit lines can occur in the following locations:

- an open between the cell and the write circuits (denoted as  $OB_w$ );

- an open between the cell and the read circuits (denoted as  $OB_r$ ).

Since there are p pairs of bit lines connected to each cell, 4p opens at bit lines can exist; 2p opens at the side of the write circuits and 2p opens at the side of the read circuits. However, one only needs to simulate two opens (e.g.,  $OB_w$  and  $OB_r$  at  $BL_i$ ) because the behavior of the other opens (e.g., opens at  $\overline{BL}_i, BL_j, \overline{BL}_j$ , etc.) can be derived (*i* and *j* denote any two different ports). This is because opens at bit lines belonging to different ports, while opens at the false side (e.g.,  $\overline{BL}_i$  and  $\overline{BL}_j$ ) have similar behaviors, while opens at the false side (e.g.,  $\overline{BL}_i$  and  $\overline{BL}_j$ ) have complementary behaviors to opens at the true side.

Opens at Word Lines: The word lines are only driven by the row decoder. Since the opens at the pass transistor gates have already been defined as opens within a cell, the only remaining opens are those in the common word lines. The influence of such opens is the same for all cells along the word lines. We will define OW as an open at the word line  $WL_i$ ; note that the total number of opens at word lines is p and that they all have similar behaviors (e.g., an open at  $WL_j$  has a similar behavior to an open at  $WL_i$ ).

The second block in Table I lists the OBs and the OWs; the minimal set of opens at bit lines and at word lines that has to be simulated consists of three opens while there 5p possible opens at bit lines and word lines. Note that all these opens can cause only SP faults and no special faults for MP memories since the fault effects of such defects can only impact the operation applied via the port to which the SD belongs [13], [16]; e.g., an open at the word line of port  $i(P_i)$  can only impact the operations performed via  $P_i$ .

#### B. Definition and Location of Shorts

The shorts are classified as *shorts within a cell* (denoted as *SC*) and *shorts at bit lines* (*SB*) and at *word lines* (*SW*). Power shorts (i.e., shorts between  $V_{cc}$  and  $V_{ss}$ ) are excluded, since they do not belong to the class of memory cell array faults; they impact the behavior of the whole circuit.

1) Shorts Within a Cell: To define shorts within a cell (SCs), a cell has to be considered as a graph in which all nodes can show a short. The cell is considered without bit lines and word lines.

TABLE II LIST OF SHORTS

| S   | horts                            | Co. behavior                 | #  | Class |

|-----|----------------------------------|------------------------------|----|-------|

| SC1 | T-V <sub>cc</sub>                | F-V <sub>cc</sub>            | 2  | SFD   |

| SC2 | T-V <sub>ss</sub>                | F-Vss                        | 2  | MFD   |

| SB1 | $BL_i$ - $V_{cc}$                | $\overline{BL}_i$ - $V_{cc}$ | 2p | SFD   |

| SB2 | $BL_i$ - $V_{ss}$                | $\overline{BL}_i$ - $V_{ss}$ | 2p | SFD   |

| SW1 | WL <sub>i</sub> -V <sub>cc</sub> |                              | p  | SFD   |

| SW2 | $WL_i$ - $V_{ss}$                |                              | p  | SFD   |

Each short is defined as a pair of nodes in which one node is  $V_{cc}$  or  $V_{ss}$ . The first block of Table II lists the possible SCs; shorts at F show complementary behaviors to shorts at T; see Fig. 1. Note that the number of shorts within a cell is 4, irrespective of the number of ports *p*. In addition, and based on the simulation results of 2P memories [13], [16], SC1 can only cause SP faults, while SC2 can cause SP faults as well as special MP faults. Note that in the presence of SC2, a voltage divider will be formed during the read operations; the fault effect is then similar to that of OC3 and OC4.

2) Shorts at Bit Lines and at Word Lines: The cells belonging to the same column or the same row are connected to the same bit lines and word lines, respectively. Therefore, shorts at bit lines (SBs) and at word lines (SWs) can affect the behavior of all operations performed to these cells. Shorts at bit line  $BL_i$  and at word line  $WL_i$  have similar behaviors to shorts at  $BL_i$  and at  $WL_i$ , respectively; and shorts at  $\overline{BL_i}$ have complementary behaviors to short at  $BL_i$ , whereby i and j can be any two different ports. The second and the third block of Table II list the possible SBs and SWs; shorts with complementary behavior are grouped together in the same row. The number of shorts within each group is also given in the table. The total number of SBs and SWs for an MP cell with p ports is 6p; while one needs to simulate only four. Note that all SBs and SWs are SFDs, since the fault effects of such defects can only impact the operation applied via the port to which the SD belongs [13], [16].

### C. Definition and Location of Bridges

A bridge in a *p*-port memory cell array can connect any arbitrary pair of nodes. However, the following assumptions are made: 1) the nodes have to be located close to each other, such that the bridge can occur only within a singe cell or between physically adjacent cells, and 2) the defect can involve two nodes *at the most*. These two assumptions are verified, based on the real data found using *inductive fault analysis (IFA)*, which shows that the occurrence probability of defects involving more than two nodes is very small ( 3.4% on the average), since they require that a defect has to be very large [13], [16]. The bridges in the memory cell array can be divided into two groups:

- *Bridges within a cell (BCs)*: All bridges connecting two nodes of the same cell, including the *p* pairs of bit lines and the *p* word lines to which it is connected.

- *Bridges between cells (BCCs)*: All bridges connecting nodes of an adjacent cells, including the bit lines and the word lines to which the cells are connected.

221

TABLE III LIST OF BRIDGES WITHIN A CELL (BCS)

| I    | Bridge                     | Comp. behavior                        | #                  | Class |

|------|----------------------------|---------------------------------------|--------------------|-------|

| BC1  | T-F                        |                                       | 1                  | SFD   |

| BC2  | $T-BL_i$                   | $F-\overline{BL}_i$                   | 2p                 | SFD   |

| BC3  | $T-\overline{BL}_i$        | $F-BL_i$                              | 2p                 | SFD   |

| BC4  | $T-WL_i$                   | F-WL <sub>i</sub>                     | 2p                 | SFD   |

| BC5  | $BL_i$ - $\overline{BL}_i$ |                                       | p                  | SFD   |

| BC6  | $BL_i$ - $BL_j$            | $\overline{BL}_i$ - $\overline{BL}_j$ | p(p-1)             | MFD   |

| BC7  | $BL_i$ - $\overline{BL}_j$ |                                       | p(p-1)             | MFD   |

| BC8  | $BL_i$ - $WL_i$            | $\overline{BL}_i$ -WL <sub>i</sub>    | 2p                 | SFD   |

| BC9  | $BL_i$ - $WL_j$            | $\overline{BL}_i$ -WL <sub>j</sub>    | 2p(p-1)            | SFD   |

| BC10 | $WL_i$ - $WL_j$            |                                       | $\frac{p(p-1)}{2}$ | SFD   |

1) Bridges Within a Cell: To define all possible bridges within a cell (BCs), the cell has to be considered as a graph in which each node can be connected to another by a bridge. Each p-port cell consists of 3p + 2 nodes  $n_i(n_i \in \{T, F, BL_i, \overline{BL_i}, WL_i\})$ : a true and a false node (T, F), 2p bit lines  $(BL_i, \overline{BL}_i)$ , and p word lines  $(WL_i)$ ; whereby *i* is one of the *p* ports ( $i \in \{a, b, c, \dots, p\}$ ). Therefore, there are  $C_2^{3p+2} = (3p+2)!/(2!(3p)!) = (9p^2+9p+2)/2$ bridges. Table III shows all possible bridges within a cell. Note that bridges with similar or complementary behaviors are grouped together in the same row, such that one can restrict the simulation to only one bridge of each row; e.g., only the first column of the table. The total number of bridges within one group is given in the third column of the table; the class of BCs is also given based on the simulation results for 2P memories [13], [16]. Note that only BC6 and BC7 can cause special faults in MP memories since they involve bit lines belonging to different ports [13], [16].

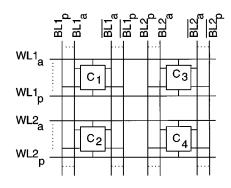

2) Bridges Between Cells: Bridges between cells (BCCs) consist of BCCs in the same row (rBCCs), BCCs in the same column (cBCCs), and BCCs on the same diagonal (dBCCs). To establish all possible BCCs, the configuration shown in Fig. 4 will be considered. It consists of four cells, namely  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ . Note that the adjacent cells can belong to the same column, the same row, or to the same diagonal. The cells  $C_1$  and  $C_3$ , as well as the cells  $C_2$  and  $C_4$ , are adjacent in the same row and therefore have common word lines, while the cells  $C_1$  and  $C_2$  (as well as the cells  $C_3$  and  $C_4$ ) are adjacent in the same column and therefore have common bit lines.

a) Bridges Between Cells in Same Row: In order to find all possible bridges between adjacent cells in the same row (rBCCs), only  $C_1$  and  $C_3$  have to be considered; see Fig. 4. Both  $C_1$  and  $C_3$  consist of 2 + 3p nodes:  $C_1$  consists of T1, F1,  $BL1_i$ ,  $\overline{BL1}_i$ , and  $WL1_i$ , while  $C_3$  consists of T3, F3,  $BL2_i, \overline{BL2}_i, \text{ and } WL1_i; i \in \{a, b, \dots, p\}$ . Since both cells have a common word line, only the true or false node (T1, F1) of  $C_1$  and its p pairs of bit lines can form a bridge with the true/false node or with the p pairs of bit lines of  $C_3$ . Therefore, there are  $(2 + 2p) * (2 + 2p) = 4p^2 + 8p + 4$  possible bridges,  $n_1 - n_2$ , between the two cells; whereby,  $n_1$  is a node of  $C_1(n_1 \in \{T1, F1, BL1_i, \overline{BL1}_i, \})$  and  $n_2$  is a node of  $C_3(n_2 \in \{T3, F3, BL2_j, \overline{BL2}_j\})$ . The first block of Table IV shows all possible rBCCs; ports i and j indicate any two *different* ports. Bridges with a complementary, an interchanged, or an interchanged complementary (I.C.) behavior are grouped

Fig. 4. Four cell configuration.

together in the same row. The total number of bridges within one group is given in the fifth column of the table. Note that the  $4p^2 + 8p + 4$  possible bridges are grouped in only eight groups. The class of rBCCs is also given based on the simulation results found for 2P memories [13]. Note that all rBCCs can cause special faults in MP memories.

b) Bridges Between Cells in Same Column: In order to find all possible bridges between adjacent cells in the same column (cBCCs), only  $C_1$  and  $C_2$  have to be considered; see Fig. 4. Both  $C_1$  and  $C_2$  consist of 2 + 3p nodes:  $C_1$  consists of T1, F1, <u>BL1</u><sub>i</sub>, <u>BL1</u><sub>i</sub>, and <u>WL1</u><sub>i</sub>, while  $C_2$  consists of T2, F2, <u>BL1</u><sub>i</sub>, <u>BL1</u><sub>i</sub>, and <u>WL2</u><sub>i</sub>;  $i \in \{a, b, \ldots, p\}$ . Note that the two cells share the same bit lines. Therefore, there are  $(2+p)*(2+p) = p^2 + 4p + 4$  possible bridges,  $n_1 - n_2$ , between  $C_1$  and  $C_2$ ; whereby,  $n_1 \in \{T1, F1, WL_i\}$  and  $n_2 \in \{T2, F2, WL2_i\}$ . A bridge between the bit lines and the nodes T2 or F2 is excluded since it belongs to bridges within a cell, which are already considered in Section II-C1. The second block of Table IV lists the  $p^2 + 4p + 4$  possible cBCCs; they are grouped into five groups. Note that only three cBCC groups can cause special faults in MP memories.

c) Bridges Between Diagonal Cells: The possible bridges between cells belonging to the same diagonal, dBCCs (i.e.,  $C_1$  and  $C_4$  of Fig. 4), consist only of four bridges; see the third block of Table IV. All other bridges between the nodes of  $C_1$  and the nodes of  $C_4$  are already considered in rBCCs and cBCCs; this is because  $C_4$  has the same word lines as  $C_2$  and the same bit lines as  $C_3$ .

#### **III. SIMULATION MODEL/METHODOLOGY**

In this section, the simulation model as well as the simulation methodology will be discussed.

# A. Simulation Model

The SPICE-like *circuit simulation environment*<sup>1</sup> (*CSE*) has been used for the simulation. Since CSE requires too much simulation time for a complete memory, an appropriate simulation model has to be built, which will both accurately describe the behavior of the memory while requiring only a reasonable simulation time. The accuracy of the simulation model determines the accuracy of the results, which implies that the model has to approximate the actual memory structure as close as possible.

The simulation model consists of a  $2 \times 2$  memory cell array; each port can be accessed using the *p* ports of the memory. In

| Br    | idge BCC                   | Complementary behavior                | Interchanged beh.          | I.C. behavior          | # of bridges | Class |

|-------|----------------------------|---------------------------------------|----------------------------|------------------------|--------------|-------|

| rBCC1 | T1-T3                      | F1-F3                                 | 1                          |                        | 2            | MFD   |

| rBCC2 | T1-F3                      | F1-F3                                 |                            |                        | 2            | MFD   |

| rBCC3 | $T1-BL2_i$                 | $F1-\overline{BL2}_i$                 | BL1 <sub>i</sub> -T3       | $\overline{BL1}_i$ -F3 | 4 <i>p</i>   | MFD   |

| rBCC4 | $T1-\overline{BL2}_i$      | F1-BL2 <sub>i</sub>                   | BL1 <sub>i</sub> -T3       | BL1 <sub>i</sub> -F3   | 4 <i>p</i>   | MFD   |

| rBCC5 | $BL1_i - BL2_i$            | $\overline{BL1}_i - \overline{BL2}_i$ |                            |                        | 2p           | MFD   |

| rBCC6 | $BL1_i - BL2_j$            | $\overline{BL1}_i - \overline{BL2}_j$ |                            |                        | 2p(p-1)      | MFD   |

| rBCC7 | $BL1_i - \overline{BL2}_i$ | $\overline{BL1}_i - BL2_i$            |                            |                        | 2 <i>p</i>   | MFD   |

| rBCC8 | $BL1_i - \overline{BL2}_j$ |                                       | $\overline{BL1}_i - BL2_j$ |                        | 2p(p-1)      | MFD   |

| cBCC1 | T1-T2                      | F1-F2                                 |                            |                        | 2            | MFD   |

| cBCC2 | T1-F2                      | F1-T2                                 |                            |                        | 2            | MFD   |

| cBCC3 | $T1-WL2_i$                 | F1-WL2 <sub>i</sub>                   | T2-WL1 <sub>i</sub>        | F2-WL1 <sub>i</sub>    | 4 <i>p</i>   | MFD   |

| cBCC4 | $WL1_i$ - $WL2_i$          |                                       |                            |                        | p            | SFD   |

| cBCC5 | $WL1_i$ - $WL2_j$          |                                       |                            |                        | p(p-1)       | SFD   |

| dBCC1 | T1-T4                      |                                       | F1-F4                      |                        | 2            | MFD   |

| dBCC2 | T1-F4                      |                                       | F1-T4                      |                        | 2            | MFD   |

TABLE IV LIST OF BRIDGES BETWEEN ADJACENT CELLS (BCCS)

addition, all cells of the memory cell array sharing the same bit lines or the same word lines (with the  $2 \times 2 \mod 1$ ) are added to the simulation model such that their loading can be taken into account. The model also contains *p* duplicated read and write circuits (i.e., precharge circuits, write drivers, sense amplifiers, etc). Moreover, the model also includes the resistance of the interconnections as well as the coupling between the adjacent cells. The model has been built for a differential 2P memory as well as for differential three-port (3P) memory, using Intel real designs.

#### B. Simulation Methodology

The simulation methodology has to examine all allowed operations in the to be simulated *p*P memory, for all opens, shorts, and bridges, by examining the resistance range for each SD from 0  $\Omega$  to  $\infty \Omega$ .

For a 2P memory, the methodology has to verify in addition to SP operations (i.e., read and write), all allowed 2P operation in the considered 2P memory design; they consist of the following.

- Two simultaneous read operations to the same location, as well as to different locations.

- Two simultaneous write operations to different locations.

- Simultaneous read and write to different locations.

- Simultaneous read and write to the same location. However, in that case the read data will be discarded; i.e., the write operation has a high priority.

For the 3P memory, the methodology has to verify all SP operations, all allowed 2P operations (which are the same as above), as well as all allowed 3P operations. The latter consists of the following simultaneous operations.

- Three operations (read and/or write) to different locations.

- Three read operations to the same and/or different location(s).

- Three write operations to different locations.

- Two reads to the same location and a write to another location.

- Two reads and write to the same location. However, in that case the read data will be discarded; i.e., the write operation has a high priority.

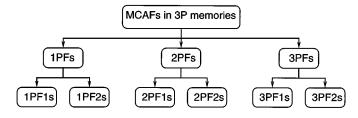

Fig. 5. Classification of MCAFs in 3P memories.

## **IV. FUNCTIONAL FAULT MODELS**

The simulation has been done for all opens, shorts, and bridges by examining the resistance range from  $0 \Omega$  to  $\infty \Omega$ , for a 2P SRAM design as well as for a 3P SRAM design [13], [16]. Each faulty behavior is reported in terms of a *fault primitive (FP)*; i.e., a compact notation describing the faulty behavior. It should be noted that after the simulation has been done for 2P SRAMs, the simulation has been redone only for MFDs (i.e., SD causing 1PFs as well as 2PFs) for the 3P SRAM design. Some simulation results will be given in Section V.

In order to design memory tests for detecting faults, the electrical faults caused by the SDs (expressed in terms of FPs) have to be translated into *functional fault models* (*FFMs*); whereby, an FFM is defined as a nonempty set of FPs. For example, a stuck-at fault (SAF) is an FFM, while the MATS+ [17] test has been designed to detect SAFs. The FFMs for 2P SRAMs, which can be considered as a subset of the FFMs for 3P SRAMs, are described in [13] and [14]. In this section, first the FFMs for a differential 3P SRAM will be presented, based on the simulation results; thereafter, the results will be extended for any MP memory with p ports.

# A. FFMs for 3P Memories

Based on the number of ports required in order to sensitize the faults, FFMs for memory cell array faults (MCAFs) in 3P memories can be classified into *single-port faults (1PFs), two-port faults (2PFs)*, and *three-port faults (3PFs)*; see Fig. 5. The 1PFs are faults that can be sensitized using SP operations. They are divided into 1PFs involving a single cell (1PF1s) and 1PFs involving two cells (1PF2s). The 2PFs are faults that cannot be

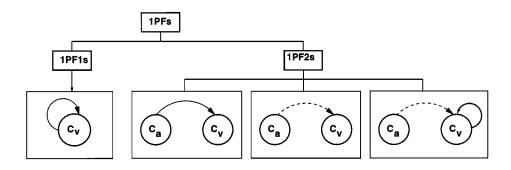

Fig. 6. Classification of 1PFs.

sensitized using SP operations; they require the use of the two ports of the memory simultaneously and are also divided into 2PFs involving a single cell (2PF1s) and 2PFs involving two cells (2PF2s). On the other hand, 3PFs are faults that cannot be sensitized using SP operations or 2P operations; they require the use of the three ports of the memory simultaneously. The 3PFs can be also divided into 3PFs involving a single cell (3PF1s) and 3PFs involving two cells (3PF2s). In the following the three classes will be discussed in detail.

1) Single-Port Faults : 1PFs are divided into faults involving a single-cell (1PF1s) and faults involving two-cells (1PF2s); see Fig. 6. The 1PF1s consist of single-cell FPs; they have the property that the cell used for sensitizing the fault is the same cell as where the fault appears. The 1PF2s have the property: (a) the application of a single-port operation (solid arrow in Fig. 6) to the aggressor cell ( $c_a$ ), (b) the state of the cell  $c_a$  (dashed arrow in the figure), or (c) the application of a single-port operation of a single-port operation to the victim cell ( $c_v$ ) with cell  $c_a$  in certain state, has as a consequence that a fault will be sensitized in the cell  $c_v$ .

To denote the 1PFs faults, the following precise compact notation referred as a *fault primitive (FP)*, which will prevent ambiguities and misunderstandings, will be used.

•  $\langle S/F/R \rangle$  (or  $\langle S/F/R \rangle_v$ ): denotes an FP involving a single-cell (a 1PF1); the cell  $c_v$  (victim cell) used to sensitize a fault is the same as where the fault appears. S describes the value/operation sensitizing the fault;  $S \in$  $\{0, 1, w0, w1, w \uparrow, w \downarrow, r0, r1, \forall\}$ , whereby 0 (1) denotes a zero (one) value, w0(w1) denotes a write 0(1) operation,  $w \uparrow (w \downarrow)$  denotes an up (down) transition write operation, r0(r1) denotes a read 0(1) operation, and  $\forall$  denotes any operation ( $\forall \in \{0, 1, w1, w0, w \uparrow, w \downarrow, r1, r0\}$ ). If the fault effect of S appears after a time T, then the sensitizing operation is given as  $S_T$ . F describes the value of the *faulty* cell (v-cell);  $F \in \{0, 1, \uparrow, \downarrow, ?\}$ , whereby  $\uparrow$  $(\downarrow)$  denotes an up (down) transition, and ? denotes an undefined state of the cell (e.g., the true and the false node of the cell have the same voltage). R describes the logical value which appears at the output of the SRAM if the sensitizing operation applied to the v-cell is a read operation:  $R \in \{0, 1, ?, -\}$ , whereby ? denotes an undefined or random logical value. An undefined logical value can occur if the voltage difference between the bit lines (used by the sense amplifier) is very small. A '-' in R means that the output data is not applicable; e.g., if S = w0,

TABLE V LIST OF 1PF1s;  $x \in \{0, 1\}$

| FFM  | Fault primitives                                            |

|------|-------------------------------------------------------------|

| SAF  | < ∀/0/->, < ∀/1/->                                          |

| TF   | $< w \uparrow /0/->, < w \downarrow /1/->$                  |

| RDF  | $ $ < $r0/\uparrow/1>$ , < $r1/\downarrow/0>$               |

| DRDF | $ $ < $r0/\uparrow/0>$ , < $r1/\downarrow/1>$               |

| IRF  | < r0/0/1 >, < r1/1/0 >                                      |

| RRF  | < r0/0/? >, < r1/1/? >                                      |

| DRF  | $< 1_T / \downarrow /->, < 0_T / \uparrow /->, < x_T /?/->$ |

| NAF  | $< w \uparrow /0/->, < w \downarrow /1/->, < rx/x/?>$       |

| USF  | < wx/?/->, < rx/?/?>                                        |

|      |                                                             |

then no data will appear at the memory output, and for that reason R is replaced by a '-'.

•  $\langle S_a; S_v/F/R \rangle$  (or  $\langle S_a; S_v/F/R \rangle_{a,v}$ ): denotes an FP involving two cells (a 1PF2);  $S_a$  describes the sensitizing operation or state of the *aggressor cell (a-cell)*; while  $S_v$  describes the sensitizing operation or state of the *victim cell (v-cell)*. The a-cell ( $c_a$ ) is the cell sensitizing a fault in an other cell called the v-cell ( $c_v$ ). The set  $S_i$  is defined as:  $S_i \in \{0, 1, w1, w0, w \uparrow, w \downarrow, r1, r0\}$  ( $i \in \{a, v\}$ ).

*The 1PF1 Fault Subclass:* The 1PF1 faults are FFMs consisting of single-port, single-cell FPs. They consist of nine FFMs [13], [15]; see Table V. The first column gives the abbreviation of the FFM, while the second column shows the FPs the FFM consists of (see also the sixth column of Table IX which shows the FFM to which each FP, sensitized in the presence of a certain defect, belongs):

- Stuck-at fault (SAF): the logic value of a cell is always '0' or '1'. The SAF consists of two FPs: < ∀/0/- >, and < ∀/1/- >; see Table V;

- 2) Transition fault (TF);

- 3) *Read destructive fault (RDF)* [20];

- 4) Deceptive read destructive fault (DRDF) [20];

- 5) Incorrect read fault (IRF);

- 6) Random read fault (RRF);

- 7) Data retention fault (DRF) [21];

- 8) No access fault (NAF);

- 9) Undefined state fault (USF).

*The 1PF2 Fault Fault Subclass:* The 1PF2 faults are FFMs consisting of single-port FPs, which involve two cells. They consist of seven FFMs [13], [15]; see Table VI.

TABLE VI LIST OF 1PF2S;  $x \in \{0, 1\}$

| $\mathbf{FFM}$ | Fault primitives                                          |

|----------------|-----------------------------------------------------------|

| $CF_{ds}$      | $\langle wx; 0/\uparrow/->, \langle wx; 1/\downarrow/->,$ |

|                | $< rx; 0/\uparrow/->, < rx; 1/\downarrow/->$              |

| CFst           | < 1; 1/0/->, < 1; 0/1/->,                                 |

|                | < 0; 1/0/->, < 0; 0/1/->                                  |

| $CF_{ir}$      | < 0; r0/0/1 >, < 0; r1/1/0 >,                             |

|                | < 1; r0/0/1 >, < 1; r1/1/0 >                              |

| $CF_{rr}$      | < 0; r0/0/? >, < 0; r1/1/? >,                             |

|                | < 1; r0/0/? >, < 1; r1/1/? >                              |

| $CF_{dr}$      | $  < 0; r0/\uparrow/0>, < 0; r1/\downarrow/1>,$           |

|                | $ <1; r0/\uparrow/0>, <1; r1/\downarrow/1>$               |

| $CF_{rd}$      | $<0; r0/\uparrow/1>, <0; r1/\downarrow/0>,$               |

|                | $< 1; r0/\uparrow/1>, < 1; r1/\downarrow/0>$              |

| $CF_{tr}$      | $<0; w \downarrow /1/->, <0; w \uparrow /0/->,$           |

|                | $ $ < 1; $w \downarrow /1/->$ , < 1; $w \uparrow /0/->$   |

- 1) Disturb Coupling Fault ( $CF_{ds}$ ) [19]: a disturb coupling fault is defined as a fault whereby the v-cell undergoes a transition due to a write or a read operation applied to the a-cell. It consists of eight FPs :  $\langle wx; 0/\uparrow /- \rangle$ ,  $\langle wx; 1/\downarrow /- \rangle$ ,  $\langle rx; 0/\uparrow /- \rangle$ , and  $\langle rx; 1/\downarrow /- \rangle$ , whereby  $x \in \{0, 1\}$ .

- 2) State coupling fault  $(CF_{st})$  [21].

- 3) Incorrect read coupling fault  $(CF_{ir})$ .

- 4) Random read coupling fault ( $CF_{rr}$ ).

- 5) Deceptive read destructive coupling fault  $(CF_{dr})$ .

- 6) Read destructive coupling fault ( $CF_{rd}$ ).

- 7) Transition coupling fault ( $CF_{tr}$ ).

2) *Two-Port Faults (2PFs):* In order to represent MP faults (e.g., two-port faults), the following terminology will be (re)introduced [7]–[10].

- *Strong fault:* This is a memory fault that can be **fully** *sensitized* by an operation; e.g., an SP write or read operation fails, two simultaneous read operations fail, etc. That means that the state of the v-cell is incorrectly changed, cannot be changed, or that the sense amplifier(s) return(s) an incorrect result(s).

- *Weak fault:* This is a fault which is **partially** sensitized by an operation; e.g., due to a defect that creates a small disturbance of the voltage of the true node of the cell. However, a fault can be *fully sensitized* (i.e., becomes strong) when two (or more) weak faults are sensitized simultaneously, since their fault effects can be additive. This may occur when a *p*P operation is applied. Note that in the presence of a weak fault, all SP (read and write) operations pass correctly, and that the *p*P operations may pass correctly. The latter will be the case if the fault effects of the weak faults are not sufficient to fully sensitize a fault.

The terminology of weak and strong faults is used in representing the MP faults as follows.

• *F* denotes a *strong fault F*, while *wF* denotes the *weak fault F*. For example, *RDF* denotes a strong read destructive fault, while *wRDF* denotes a weak read destructive fault.

•  $< fault_1 > \& < fault_2 > \cdots \& < fault_p >:$  denotes a *p*PF consisting of *p* weak faults; '&' denotes the fact that the *p* faults *in parallel* (i.e., simultaneously) form the *p* PF. E.g., the wRDF&wRDF denote a 2PFs based on two weak RDFs.

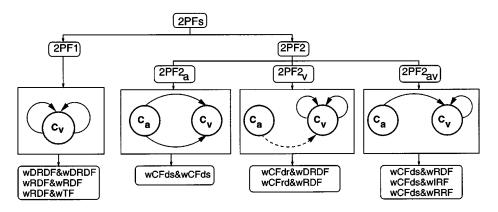

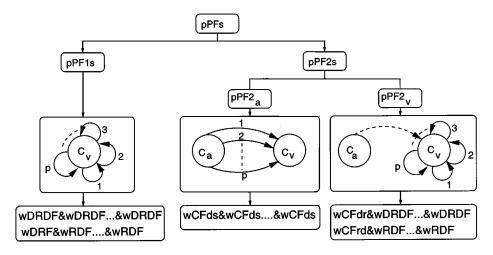

Two-port faults (2PFs) cannot be sensitized using SP operations; they require the use of the two ports simultaneously. The 2PFs can be considered as a combination of *two weak faults*. They can be divided into *faults involving a single cell* (2PF1s) and *faults involving two cells* (2PF2s) [13], [14]; see Fig. 7. A taxonomy of all realistic 2PFs is given also in the same figure.

Table VII shows the FPs of which each 2PF is composed. The FP notation used to describe the 2PF1s and 2PF2s is given as follows.

•  $\langle S_1 : S_2/F/R \rangle_v$ : denotes a two-port FP involving a single cell (v-cell); a 2PF1. This FP requires the use of the two ports *simultaneously*.  $S_1$  and  $S_2$  describe the sensitizing operations or states of the v-cell; ":" denotes the fact that  $S_1$  and  $S_2$  are applied *simultaneously* via the two ports. F describes the value of the v-cell. Note that the sensitizing operations are applied to the same cell as where the fault appears. R is the read result of  $S_1$  (and/of  $S_2$ ) if it is a read operation.

For 2PF2s, three notations can be identified, based on the cell(s) to which the two *simultaneous* sensitizing operations are applied, either to the aggressor cell and/or to the victim cell; see Fig. 7.

- $\langle S_a : S_a; S_v/F/R \rangle_{a,v}$  denotes a 2PF2<sub>a</sub>: an FP whereby both sensitizing operations,  $S_a$ , are applied to the a-cell.  $S_v$  denotes the state of the v-cell.

- $\langle S_a; S_v : S_v/F/R \rangle_{a,v}$  denotes a 2PF2<sub>v</sub>: an FP whereby both sensitizing operations,  $S_v$ , are applied to the v-cell.  $S_a$  describes the state of the a-cell.

- $< S_a : S_v/F/R >_{a,v}$  denotes a 2PF2<sub>av</sub>: an FP whereby one sensitizing operation,  $S_a$ , is applied to the a-cell, and the other sensitizing operation,  $S_v$ , is applied to the v-cell.

In the above notations, F denotes the value of the faulty cell  $c_v$ , and R denotes the value which appears at the memory output if  $S_v$  is a read operation. The above notation can be extended to describe any p-port fault (pPF); e.g.,  $< S_a : S_a : S_a$ ;  $S_v/F/R >_{a,v}$  denotes a FP whereby three simultaneous sensitizing operations,  $S_a$ , are applied to the a-cell; while  $S_v$  denotes the state of the v-cell; etc.

*The 2PF1 Fault Subclass:* The 2PF1s are based on a combination of *two single-cell weak faults.* In addition, the two a-cells are the same as the v-cell; see Fig. 7. In order to sensitize a 2PF1, the same cell has to be acted upon simultaneously via the two ports. The 2PF1 consists of three FFMs [13], [14], and are listed together with their FPs in Table VII (see also the sixth column of Table IX).

- *wDRDF&wDRDF:* Applying two simultaneous read operations to a single cell causes the cell to flip, while the sense amplifiers return the *correct values*.

- *wRDF&wRDF:* Applying two simultaneous read operations to a single cell causes the cell to flip and the sense amplifiers return *incorrect* values.

Fig. 7. Classification and taxonomy of 2PFs.

TABLE VII LIST OF 2PFS;  $x \in \{0, 1\}$  AND d = Don't Care

| FFM                                  | Fault primitives                                                             |

|--------------------------------------|------------------------------------------------------------------------------|

| wDRDF&wDRDF                          | $ $ < $r0: r0/\uparrow/0>, < r1: r1/\downarrow/1>$                           |

| wRDF&wRDF                            | $< r0: r0/\uparrow/1>, < r1: r1/\downarrow/0>$                               |

| wRDF&wTF                             | $  < r0: w \uparrow /0/->, < r1: w \downarrow /1/->$                         |

| wCF <sub>ds</sub> &wCF <sub>ds</sub> | $\langle w0: rd; 0/\uparrow/->, \langle w0: rd; 1/\downarrow/->,$            |

|                                      | $  \langle w1: rd; 0/\uparrow/->, \langle w1: rd; 1/\downarrow/->,$          |

|                                      | $ $ < $rx$ : $rx$ ; 0/ $\uparrow$ /- >, < $rx$ : $rx$ ; 1/ $\downarrow$ /- > |

| wCF <sub>dr</sub> &wDRDF             | $< 0; r0: r0/\uparrow/0>, < 0; r1: r1/\downarrow/1>,$                        |

|                                      | $<1; r0: r0/\uparrow /0>, <1; r1: r1/\downarrow /1>,$                        |

| $wCF_{rd}\&wRDF$                     | $<0; r0: r0/\uparrow/1>, <0; r1: r1/\downarrow/0>,$                          |

|                                      | $<1; r0:r0/\uparrow/1>, <1; r1:r1/\downarrow/0>$                             |

| wCF <sub>ds</sub> &wRDF              | $< w0: r0/\uparrow/1>, < w0: r1/\downarrow/0>,$                              |

|                                      | $< w1: r0/\uparrow/1>, < w1: r1/\downarrow/0>$                               |

| wCF <sub>ds</sub> &wIRF              | < w0: r0/0/1 >, < w0: r1/1/0 >,                                              |

|                                      | < w1: r0/0/1>, < w1: r1/1/0>                                                 |

| wCF <sub>ds</sub> &wRRF              | < w0: r0/0/?>, < w0: r1/1/?>,                                                |

|                                      | < w1: r0/0/? >, < w1: r1/1/? >                                               |

wRDF&wTF: A cell fails to undergo a write transition if a read operation is applied to the same cell simultaneously.

It should be noted that the wDRDF&wDRDF and wRDF&wRDF can be caused by the following defects, but with different resistance values of the defect [13], [16]: (a) drain/source of the pull-down transistor of the cell broken (OC3, OC4), (b) true or false node shorted to  $V_{ss}$  (SC2), and (c) short between a cell's node and a word line of an adjacent cell (cBCC3). The wRDF & wTF can be caused by bridges between bit lines belonging to the same column, to different ports and to different sides (i.e., true side and false side) of the cell.

The 2PF2 Fault Subclass: The 2PF2s are based on a combination of weak single-cell faults and weak faults involving two cells. Depending on to which cells the two simultaneous operations are applied (to the a-cell and/or to the v-cell), the 2PF2s are divided into three types (see Fig. 7): the  $2PF2_a$ , the  $2PF2_v$ , and the  $2PF2_{av}$ .

The 2PF2<sub>a</sub>: This fault is sensitized in cell  $c_v$  by applying two simultaneous operations to the same *a-cell*  $c_a$  (solid arrows in Fig. 7). Note that in this case, the 2PF is a combination of two weak faults involving two cells; both weak faults have the same a-cell as well as the same v-cell. The 2PF2<sub>a</sub> consists of one FFM:  $wCF_{ds}\&wCF_{ds}$ , with eight FPs; see Table VII. Note that the  $< w0 : rd; 1/ \downarrow /- >$  denotes only one FP since the read value is irrelevant (d = don't care); the read operation is used to sensitize the fault. Note also that  $\langle rx : rx; 0/\uparrow \rangle /- \rangle$ denotes two FPs since  $x \in \{0, 1\}$ . The 2PF2<sub>a</sub> can be caused by bridges between nodes of adjacent cells belonging to the same row (rBCC1, rBCC2), to the same column (cBCC1, cBCC2), or on same diagonal (dBCC1, dBCC2). They can also be caused by a bridge between a node of a cell and a bit line of an adjacent cell in the same row (rBCC3, rBCC4) [13], [16].

The  $2PF2_v$ : This fault is sensitized in cell  $c_v$  by applying two simultaneous operations to the same cell  $c_v$  (solid arrows in the figure), while the a-cell has to be in certain state (dashed arrow in Fig. 7). Note that this fault is a combination of two weak faults: a single-cell weak fault and a weak weak fault involving two cells, whereby the operation has to be performed to the v-cell while the a-cell has to be in a certain state. The  $2PF2_v$ consists of two FFMs; each with two FPs (see Table VII).

- $wCF_{dr}\&wRDF$ : Applying two simultaneous read operations to cell  $c_v$  will cause the cell to flip if cell  $c_a$  is in a certain state. The read operations return *correct* values.

- $wCF_{rd}\&wDRDF$ : Applying two simultaneous read operations to cell  $c_v$  will cause the cell to flip if cell  $c_a$  is in a certain state. The read operations than return *wrong* values.

Such faults can be caused by bridges between nodes of adjacent cells belonging to the same row, the same column, or on the same diagonal [13], [16].

The 2PF2<sub>av</sub>: This fault is sensitized by applying two simultaneous operations: one to cell  $c_a$  and one to cell  $c_v$ ; see Fig. 7. It is a combination of a single-cell weak fault and a weak fault involving two cells, and can be caused by bridges between bit lines of different ports belonging to the same or to adjacent columns (BC6, BC7, rBCC6, rBCC8). The 2PF2<sub>v</sub> consists of three FFMs, each with four FPs.

- $wCF_{ds}\&wRDF$ : A read operation applied to cell  $c_v$  flips the cell and the sense amplifier returns an incorrect value *if* a write operation is applied to cell  $c_a$  *simultaneously*.

- $wCF_{ds}\&wIRF$ : A read operation applied to cell  $c_v$  returns an incorrect value *if* a write operation is applied to cell  $c_a$  *simultaneously*. It should be noted that the state of cell  $c_v$  does not change.

- $wCF_{ds}\&wRRF$ : A read operation applied to cell  $c_v$  returns a random value *if* a write operation is applied to cell  $c_a$  simultaneously.

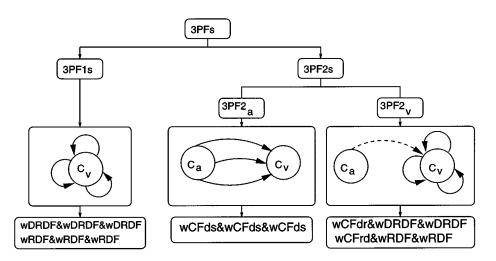

Fig. 8. Classification and taxonomy of 3PFs.

It should be noted that the above 2PFs are valid for memories which support simultaneous reading and writing of the same location, whereby the read data is discarded. If this is not supported, then the FFM wRDF&wTF will not be realistic. In addition, the FFM  $wCF_{ds}\&wCF_{ds}$  will consist only of the FPs sensitized by simultaneous read operations to the same location.

3) Three-Port Faults (3PFs): Three-port faults (3PFs) cannot be sensitized using SP operations or by using 2P operations; they require the use of the three ports simultaneously. The 3PFs can be considered as a combination of *three weak faults*. The 3PFs can be divided into faults involving a single cell (3PF1s) and faults involving two cells (3PF2s); see Fig. 8. A taxonomy of all realistic 3PFs is given in the same figure, while Table VIII shows the FPs of which each 3PF is composed. These 3PFs will be explained in detail in the following subsections.

*The 3PF1s:* The 3PF1s are based on a combination of *three single-cell weak faults*. In order to sensitize a 3PF1, the same cell has to be acted upon simultaneously via the three ports. It consists of two FFMs: wDRDF&wDRDF&wDRDF and wRDF&wRDF& each with two FPs (see Table VIII). They can be caused by the same defects as those causing the 2PF1s: wDRDF&wDRDF and wRDF&wRDF; but with a different resistance value of the defect.

*The 3PF2s:* The 3PF2s are based on a combination of single-cell weak faults and weak faults involving two cells. Depending on which cells the three simultaneous operations are applied to (to the a-cell or to the v-cell), the 3PF2s are divided into two types (see Fig. 8). Based on the FPs found by simulating MFDs, the following 3PF2s have been derived (see also the sixth column of Table IX).

The  $3PF2_{\mathbf{a}}$ : In this case, the 3PF is a combination of three weak faults involving two cells; they all have the same a-cell as well as the same v-cell (see Fig. 8). In order to sensitize the fault in cell  $c_v$ , three simultaneous operations have to be applied to the same cell  $c_a$  (solid arrows in the figure), while in order to detect the fault cell  $c_v$  has to be read. It consists of only one FFM:  $wCF_{ds}\&wCF_{ds}\&wCF_{ds}$ . Applying three simultaneous operations to cell  $c_v$  will sensitize a fault in cell  $c_v$ ;

TABLE VIII LIST OF 3PFS;  $x \in \{0, 1\}$  AND d = Don't Care

| FFM                                                     | Fault primitives                                |

|---------------------------------------------------------|-------------------------------------------------|

| wDRDF&wDRDF&wDRDF                                       | $< r0: r0: r0: r0/\uparrow/0>,$                 |

|                                                         | $< r1: r1: r1 / \downarrow /1 >$                |

| wRDF&wRDF&wRDF                                          | $  < r0: r0: r0 / \uparrow /1 >,$               |

|                                                         | $ $ < $r1:r1:r1/\downarrow/0>$                  |

| wCF <sub>ds</sub> &wCF <sub>ds</sub> &wCF <sub>ds</sub> | $\langle w0: rd: rd; 0/\uparrow/->,$            |

|                                                         | $  < w0: rd: rd; 1/\downarrow /->,$             |

|                                                         | $  < w1: rd: rd; 0/\uparrow/->,$                |

|                                                         | $  < w1: rd: rd; 1/\downarrow /->,$             |

|                                                         | $  < rx : rx : rx; 0/\uparrow/->,$              |

|                                                         | $ $ < $rx : rx : rx; 1/\downarrow/->$           |

| wCF <sub>dr</sub> &wDRDF&wDRDF                          | $< 0; r0: r0: r0 / \uparrow /0 >,$              |

|                                                         | $  < 0; r1: r1: r1 / \downarrow /1 >,$          |

|                                                         | $  < 1; r0: r0: r0 / \uparrow /0 >,$            |

|                                                         | $\langle 1; r1: r1: r1 / \downarrow /1 \rangle$ |

| wCF <sub>rd</sub> &wRDF&wRDF                            | $< 0; r0: r0: r0 / \uparrow /1 >,$              |

|                                                         | $  < 0; r1: r1: r1 / \downarrow /0 >,$          |

|                                                         | $  < 1; r0: r0: r0 / \uparrow /1 >,$            |

|                                                         | $ $ < 1; $r1$ : $r1$ : $r1/\downarrow/0$ >      |

i.e., cell  $c_v$  flips. Note that this FFM consists of eight FPs; see Table VIII. The 3PF2<sub>a</sub> can be caused by the same SDs as those causing the 2PF2<sub>a</sub>s, but having a different resistance value; see also Table IX.

The  $3PF2_v$ : In this case, the 3PF is a combination of three weak faults: a weak fault involving two cells and two single-cell weak faults. The weak fault involving two cells requires that the operation be performed to the v-cell while the a-cell has to be in certain state (dashed arrow in the Fig. 8). In order to sensitize the fault, three simultaneous operations have to be applied to cell  $c_v$ , and cell  $c_a$  has to be in certain state. Reading cell  $c_v$  will detect the fault. It consists of two FFMs:  $wCF_{dr}\&wDRDF\&wDRDF$ and  $wCF_{rd}\&wRDF\&wRDF$ , each with two FPs (see Table VIII). It can be caused by the same SDs as those causing the 2PF2<sub>v</sub>s but having a different resistance value; see also Table IX.

It should be noted that the 3PFs discussed above are valid for memories allowing for two simultaneous reads and a write of the

| Label  | $R_{df}$ region           | Fault primitive                                                                                 | Compl. fault primitive                                                              | Class          | Fault model                                                                                                   |

|--------|---------------------------|-------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------|---------------------------------------------------------------------------------------------------------------|

| OC3    | Region I                  | wF                                                                                              | wF                                                                                  |                |                                                                                                               |

| 003    | Region II                 | $< r0: r0: r0/ \uparrow /0 >_v$                                                                 | $\frac{w_1}{\langle r1:r1:r1/\downarrow/1\rangle_v}$                                | 3PF1           | wDRDF&wDRDF&wDRDF                                                                                             |

|        | Region III                | $< r0: r0: r0/\uparrow/1>_v$                                                                    | $< r1: r1: r1/\downarrow /0 >_v$                                                    | 3PF1           | wRDF&wRDF                                                                                                     |

|        | Region IV                 | $< r0: r0/ \uparrow /0 >_v$                                                                     | $\langle r1:r1/\downarrow/1>_v$                                                     | 2PF1           | wDRDF&wDRDF                                                                                                   |

|        | Region V                  | < r0: r0/ + /0 > v<br>< r0: r0/ + /1 > v                                                        | $< r1: r1/\downarrow /1 > v$<br>$< r1: r1/\downarrow /0 > v$                        | 2PF1           | wRDF&wRDF                                                                                                     |

|        | Region VI                 | $\langle r0/\uparrow/0>_v$                                                                      | $\langle r1/\downarrow/1 \rangle_v$                                                 | 1PF1           | DRDF                                                                                                          |

|        | Region VI                 |                                                                                                 | $\frac{\langle r1/\downarrow /1 \rangle_{v}}{\langle r1/\downarrow /0 \rangle_{v}}$ | 11 F 1<br>1PF1 | RDF                                                                                                           |

|        | Region VIII               | $\langle r0/\uparrow/1\rangle_v$                                                                |                                                                                     | 1111<br>1PF1   | RDF                                                                                                           |

|        | Region VIII               | $\frac{\langle r0/\uparrow/1\rangle_v}{\langle 0_T/\uparrow/-\rangle_v}$                        | $\frac{\langle r1/\downarrow/0\rangle_v}{\langle 1_T/\downarrow/-\rangle_v}$        | 1PF1           | DRF                                                                                                           |

| SC2    | Region I                  | $\langle \forall /1/- \rangle_v$                                                                | $\langle \forall / 0 / - \rangle_v$                                                 | 1PF1           | SAF                                                                                                           |

| 302    | Region II                 | $\langle r_1/\downarrow/0 \rangle_v$                                                            | $< r0/\uparrow/1>_v$                                                                | 1PF1           | RDF                                                                                                           |

|        | Region III                | $ \langle r1/\downarrow /0 \rangle_v$<br>$ \langle r1/\downarrow /1 \rangle_v$                  | $\langle r0/\uparrow/1 \rangle_v$                                                   | 1111<br>1PF1   | DRDF                                                                                                          |

|        | Region IV                 | $\langle r1 \rangle \langle r1 \rangle v$<br>$\langle r1 : r1/\downarrow /0 \rangle v$          | $< r0 : r0/\uparrow/1>_v$                                                           | 2PF1           | wRDF&wRDF                                                                                                     |

|        | Region V                  | $\frac{\langle r1:r1/\downarrow /0 \rangle_{v}}{\langle r1:r1/\downarrow /1 \rangle_{v}}$       | $< r0: r0/\uparrow/1>_v$                                                            | 21111<br>2PF1  | wDRDF&wDRDF                                                                                                   |

|        | Region VI                 | $\frac{\langle r1:r1/\psi/1 \rangle_v}{\langle r1:r1:r1/\psi/0 \rangle_v}$                      | $< r0: r0: r0/ + /0 >_v$<br>$< r0: r0: r0/ + /1 >_v$                                | 3PF1           | wRDF&wRDF                                                                                                     |

|        | Region VI                 | $\frac{\langle r1:r1,r1/\downarrow /0 \rangle_{v}}{\langle r1:r1:r1/\downarrow /1 \rangle_{v}}$ | < r0: r0: r0 : r0/ 1/2v                                                             | 3PF1           | wDRDF&wDRDF&wDRDF                                                                                             |

|        | Region VIII               | $\sqrt{1.11/1/1/2}$                                                                             | wF                                                                                  | -              | -                                                                                                             |

| BC6    | Region I                  | $< w0: r1/\downarrow/0>_{a,v}$                                                                  | $< w1: r0/\uparrow/1>_{a,v}$                                                        | 2PF2           | wCF <sub>ds</sub> &wRDF                                                                                       |

| BC0    | Region II                 | $< w0: r1/1/0 >_{a,v}$                                                                          | $< w1: r0/0/1 >_{a,v}$                                                              | 2PF2           | wCF <sub>ds</sub> &wIRF                                                                                       |

|        | Region III                | $< w0: r1/1/0 >_{a,v}$<br>$< w0: r1/1/? >_{a,v}$                                                | $< w1: r0/0/1 >_{a,v}$<br>$< w1: r0/0/? >_{a,v}$                                    | 21 F 2<br>2PF2 | wCF <sub>ds</sub> &wRRF                                                                                       |

|        | Region IV                 | $\langle w0:r1/1/: \rangle_{a,v}$<br>wF                                                         | $\sqrt{w1:r0/0/! >_{a,v}}$                                                          | -              | words & with                                                                                                  |

|        | and the                   |                                                                                                 | wF                                                                                  |                |                                                                                                               |

| BC7    | Region I                  | $< r0: w \uparrow /0 / >_v$                                                                     |                                                                                     | 2PF1           | wRDF&wTF                                                                                                      |

|        |                           | $< r1: w \downarrow /1 / >_v$                                                                   |                                                                                     | 2PF1           | wRDF&wTF                                                                                                      |

|        |                           | $< w1: r1/\downarrow/0>_{a,v}$                                                                  |                                                                                     | 2PF2           | wCF <sub>ds</sub> &wRDF                                                                                       |

|        |                           | $< w0: r0/\uparrow/1>_{a,v}$                                                                    |                                                                                     | 2PF2           | wCF <sub>ds</sub> &wRDF                                                                                       |

|        | Region II                 | $< w1: r1/\downarrow/0>_{a,v}$                                                                  |                                                                                     | 2PF2           | wCF <sub>ds</sub> &wRDF                                                                                       |

|        |                           | $< w0: r0/\uparrow/1>_{a,v}$                                                                    |                                                                                     | 2PF2           | wCF <sub>ds</sub> &wRDF                                                                                       |

|        | Region III                | $< w1: r1/1/0 >_{a,v}$                                                                          |                                                                                     | 2PF2           | wCF <sub>ds</sub> &wIRF                                                                                       |

|        |                           | $< w0: r0/0/1 >_{a,v}$                                                                          |                                                                                     | 2PF2           | wCF <sub>ds</sub> &wIRF                                                                                       |

|        | Region IV                 | $< w1: r1/1/? >_{a,v}$                                                                          |                                                                                     | 2PF2           | wCF <sub>ds</sub> &wRRF                                                                                       |

|        | Deries V                  | $< w0: r0/0/? >_{a,v}$ wF                                                                       |                                                                                     | 2PF2           | wCF <sub>ds</sub> &wRRF                                                                                       |

| - DOOL | Region V                  |                                                                                                 |                                                                                     | Ii             | -<br>CF <sub>st</sub>                                                                                         |

| rBCC1  | Region I                  | $<0;1/0/->_{a,v}$                                                                               | $< 1; 0/1/->_{a,v}$                                                                 | 1PF2           | CF <sub>st</sub>                                                                                              |

|        | Region II                 | $<0;r1/\downarrow/0>_{a,v}$                                                                     | $<1;r0/\uparrow/1>_{a,v}$                                                           | 1PF2           | CF <sub>rd</sub>                                                                                              |

|        | - D 1 111                 | $< r0; 1/\downarrow /->_{a,v}$                                                                  | $\langle r1; 0/\uparrow /- \rangle_{a,v}$                                           | 1PF2           | CF <sub>ds</sub>                                                                                              |

|        | Region III                | $<0;r1:r1/\downarrow/0>_{a,v}$                                                                  | $<1; r0: r0/\uparrow/1>_{a,v}$                                                      | 2PF2           | wCF <sub>rd</sub> &wDRDF                                                                                      |

|        |                           | $< r0: r0; 1/\downarrow/->_{a,v}$                                                               | $< r1: r1; 0/\uparrow/->_{a,v}$                                                     | 2PF2           | CF <sub>ds</sub> &wCF <sub>ds</sub>                                                                           |

|        |                           | $< w0: r1; 1/\downarrow/->_{a,v}$                                                               | $< w1: r0; 0/\uparrow/->_{a,v}$                                                     | 2PF2           | wCF <sub>ds</sub> &wCF <sub>ds</sub>                                                                          |

|        |                           | $< w0: r0; 1/\downarrow/->_{a,v}$                                                               | $ $ $< w1:r1;0/\uparrow/->_{a,v}$                                                   | 2PF2           | wCF <sub>ds</sub> &wCF <sub>ds</sub>                                                                          |

|        | Region IV                 | $<0; r1: r1/\downarrow/1>_{a,v}$                                                                | $<1; r0: r0/\uparrow/0>_{a,v}$                                                      | 2PF2           | wCF <sub>dr</sub> &wDRDF                                                                                      |

|        |                           | $< r0: r0; 1/\downarrow /->_{a,v}$                                                              | $< r1: r1; 0/\uparrow /->_{a,v}$                                                    | 2PF2           | wCF <sub>ds</sub> &wCF <sub>ds</sub>                                                                          |

|        |                           | $< w0: r1; 1/\downarrow /->_{a,v}$                                                              | $< w1: r0; 0/\uparrow/->_{a,v}$                                                     | 2PF2           | wCF <sub>ds</sub> &wCF <sub>ds</sub>                                                                          |

|        |                           | $< w0: r0; 1/\downarrow /->_{a,v}$                                                              | $\langle w1:r1;0/\uparrow/->_{a,v}$                                                 | 2PF2           | wCF <sub>ds</sub> &wCF <sub>ds</sub>                                                                          |

|        | Region V                  | $<0;r1:r1:r1/\downarrow/0>_{a,v}$                                                               | $< 1; r0: r0: r0/\uparrow /1 >_{a,v}$                                               | 3PF2           | wCF <sub>rd</sub> &wRDF&wRDF                                                                                  |

|        |                           | $< r0: r0: r0; 1/\downarrow /->_{a,v}$                                                          | $< r1: r1: r1; 0/\uparrow/->_{a,v}$                                                 | 3PF2           | wCF <sub>ds</sub> &wCF <sub>ds</sub> &wCF <sub>ds</sub>                                                       |

|        |                           | $< w0: rd: rd; 1/\downarrow/->_{a,v}$                                                           | $< w1: rd: rd; 0/\uparrow/->_{a,v}$                                                 | 3PF2           | wCF <sub>ds</sub> &wCF <sub>ds</sub> &wCF <sub>ds</sub>                                                       |

|        | Region VI                 | $< 0; r1: r1: r1/ \downarrow /1 >_{a,v}$                                                        | $< 1; r0: r0: r0/\uparrow /0 >_{a,v}$                                               | 3PF2           | wCF <sub>dr</sub> &wDRDF&wDRDF                                                                                |

|        |                           | $< r0: r0: r0; 1/\downarrow /->_{a,v}$                                                          | $\langle r1:r1:r1;0/\uparrow/->_{a,v}$                                              | 2PF2<br>3PF2   | $\frac{\text{wCF}_{ds}\&\text{wCF}_{ds}\&\text{wCF}_{ds}}{\text{wCF}_{ds}\&\text{wCF}_{ds}\&\text{wCF}_{ds}}$ |

|        | Region VII                | $< w0: rd: rd; 1/\downarrow/->_{a,v}$<br>wF                                                     | $  < w1: rd: rd; 0/\uparrow/->_{a,v} wF$                                            | - JEF 2        | words & words & words                                                                                         |

| -PCC1  |                           |                                                                                                 |                                                                                     | II             |                                                                                                               |

| cBCC1  | Region I                  | $<0;1/0/->_{a,v}$                                                                               | $< 1; 0/1/->_{a,v}$                                                                 | 1PF2           | CF <sub>st</sub>                                                                                              |

|        | Region II                 | $<0; r1/\downarrow/0>_{a,v}$                                                                    | $\langle 1; r0/\uparrow/1 \rangle_{a,v}$                                            | 1PF2           | CF <sub>rd</sub>                                                                                              |

|        | Region III                | $<0; r1/\downarrow/1>_{a,v}$                                                                    | $< 1; r0/ \uparrow /0 >_{a,v}$                                                      | 1PF2           | CF <sub>dr</sub>                                                                                              |

|        | Region IV                 | $<0; r1: r1/\downarrow/0>_{a,v}$                                                                | $< 1; r0: r0/\uparrow/1>_{a,v}$                                                     | 2PF2           | wCF <sub>rd</sub> &wRDF                                                                                       |

|        | Region V                  | $\langle 0; r1: r1/\downarrow/1 \rangle_{a,v}$                                                  | $< 1; r0: r0/\uparrow/0>_{a,v}$                                                     | 2PF2           | wCF <sub>dr</sub> &wDRDF                                                                                      |

|        | Region VI                 | $< 0; r1: r1: r1/ \downarrow /0 >_{a,v}$                                                        | $< 1; r0: r0: r0 / 1 >_{a,v}$                                                       | 3PF2           | wCF <sub>rd</sub> &wRDF&wRDF                                                                                  |

|        | Region VII<br>Region VIII | $<0; r1: r1: r1/\downarrow/1>_{a,v}$                                                            | $<1; r0: r0: r0/\uparrow/0>_{a,v}$                                                  | 3PF2           | wCF <sub>dr</sub> &wDRDF&wDRDF                                                                                |

|        | rtegion VIII              | wF                                                                                              | wF                                                                                  | - 1            | -                                                                                                             |