# **Net Clustering Based Macrocell Placement**

Stelian Alupoaei\* and Srinivas Katkoori University of South Florida Department of Computer Science and Engineering 4202 East Fowler Avenue, ENB 118, Tampa, FL, 33620 {alupoaei, katkoori}@csee.usf.edu

#### Abstract

Given an RTL (Register-Transfer-Level) netlist, a net dependency graph with weighted edges is built. Each node in the graph represents a net and an edge exists between two nodes if the two nets represented by the nodes share one or more macrocells. Clusters of nets are then formed by clique partitioning. A net cluster level floorplan is derived by simulated annealing to define the regions where the nets in each cluster must be routed. The macrocell placement is formulated as a force-directed problem where the terminals of a net are free to move under the influence of forces in the quest for optimal length of the net. A new type of rejection force is introduced in order to obtain a feasible placement. In comparison with the placements generated by CADENCE Silicon Ensemble, we obtained an average total wire length reduction of 22.8% and an average longest wire length reduction of 33% with an average area penalty of only 1.1%.

## 1. Introduction

In many existing placement approaches [12, 13], the "net placement" is dictated by the cell placement. As the interconnect dominates in Deep Sub-Micron (DSM) regime, CAD tools need to focus more on interconnect optimization [7, 1]. One of the early techniques that focuses on nets was proposed by Pillage and Rohrer [11] who have modeled nets as *points* and used a quadratic cost metric that is minimized by quadratic programming. Although the results were encouraging, this technique is not completely suitable for DSM regime as the delay is a function of the net topology. Mo, Tabbara, and Brayton [8] have proposed an RTL macrocell placer that models a net by a star model. The authors use force-directed method in which they account for macrocell shape and size.

We propose a Register Transfer Level (RTL) macrocell placement approach that optimizes the net lengths by using net clustering and force-directed method. Terminals of a net can move freely in the quest for an optimal wire length solution for the net. After all the terminals have stabilized, the placement position of a cell is determined by a common region defined by all the pins of the cell. Net-level forces on the net terminals drive the net length optimization. On the other hand, cell-level forces between pins of each macrocell ensure a feasible macrocell position.

The main contributions of our work are: (1) net-clustering is used to derive a floorplan; (2) difference between source and sink of a net when defining forces; such a distinction enables delay optimization; (3) the pins of a net are allowed to freely move under the influence of forces, and the cell placement is an implication of the net placement; and (4) a new *electrostatic repulsive* force is introduced. The force is inversely proportional to the square of the distance between the points. This force is strong at near distances and weak at farther distances.

The rest of the paper is organized as follows: Section 2 describes the models used. Section 3 describes the types of forces and the methods used to find the equilibrium positions. Section 4 describes the proposed approach in detail. Section 5 presents experimental results on a set of five RTL designs. Finally, Section 6 draws conclusions.

# 2. Models

#### 2.1. Net Dependency Graph

Given an RTL netlist, a weighted undirected graph,  $\mathcal{G} = (V, E)$ , is formed. Each vertex  $v \in V$  denotes a net and an edge  $(v_i, v_j) \in E$  exists if and only if the nets represented by vertices  $v_i$  and  $v_j$  share one or more macrocells. The weight of a vertex (net) is given by the number of net terminals. The weight of an edge  $(v_i, v_j)$  is given by the number of cells that the nets represented by  $v_i$  and  $v_j$  have in common.  $\mathcal{G}$  captures the dependencies between the nets and it is named the Net Dependency Graph.  $\mathcal{G}$  is the dual of the netlist hypergraph in which a vertex represents a module and a hyperedge represents a net connecting the corresponding modules. The same type of graph, called netlist intersection graph, was used in partitioning by Kahng [10] and Cong [4].

<sup>\*</sup>This work was supported by the 1999 Design Automation Conference (DAC) Scholarship.

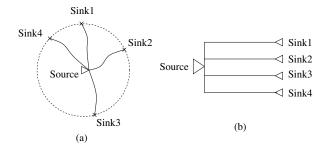

Figure 1. (a) Star model for nets. (b) The star topology.

#### 2.2. Interconnect Model

The interconnect model used is the star model<sup>1</sup> (Figure 1(a)) that conforms to a star net topology (Figure 1(b)). The source is at the center and the sinks are on the periphery. This model is suitable for the force-directed approach as the source and sink can attract each other in an attempt to minimize the wire length. The types of forces applied on a source are different from those applied on the sinks (discussed in detail later in Section 4.2). Ideally, the source is at the center of mass of the sinks as shown in Figure 1. Only single-source nets are considered in this paper. The model can be easily extended to multi-source nets. The motivation for a distinction between source and sink in the model is the fact that for delay optimization (work in progress), the delay estimate between the source and any sink can be used to derive appropriate forces on each other. A bus is treated as a single net with higher priority in order to reduce the problem size in terms of number of nets.

As a consequence of the interconnect model, in our approach the macrocells pins are not fixed on the cell boundary. At the beginning of the algorithm they are placed randomly and, during the iteration process, they try to find a position close to the cell boundary. The cells are modeled as circles with the radius given by the size of the cell R = (dx + dy)/4, where dx and dy are the macrocell dimensions.

## 3. Forces

The following notation is used to denote a force

$$\vec{F}_{n/c}^{a/r}(u,v) \tag{1}$$

where subscripts n and c (if present) classify  $\vec{F}$  into a netlevel force and cell-level force respectively. Superscripts aand r (if present) classify  $\vec{F}$  into an attractive and repulsive force respectively. The force is applied on the entity u (which can be a net terminal or a cell center) due to the entity v. For example,  $\vec{F}_c^a(p, Center(C_k))$ , represents an attractive force between the pin, p, and the center of cell,  $C_k$ . Further, it is a cell-level force, acting on p due to the cell  $C_k$ .

#### **3.1.** Attractive Forces

In general, an *attractive* force is computed as follows:

$$\vec{F}^a = K_1(\vec{r}_i - \vec{r}_j) \tag{2}$$

where  $K_1$  is an analogous spring constant and  $(\vec{r}_i - \vec{r}_j)$  is the displacement.

The value of  $K_1$ , the attraction coefficient, may be increased during the iterative process in order to reduce the distance between the objects that are attracting each other when this distance is bigger than the optimal value. Initially, this coefficient has the value of unity. Its value is updated each iteration using the following expression:

$$K_1' = \alpha \cdot K_1 + (1 - \alpha)(|\vec{r_i} - \vec{r_j}|/R)$$

(3)

where  $\alpha$  is a user chosen constant between 0 and 1,  $K'_1$  is the updated value of  $K_1$ , and R is the optimal distance.

#### **3.2. Repulsive Forces**

In order to obtain a feasible placement, when two objects are closer than the optimal distance, a repulsive force must be introduced. A new repulsive force (*electrostatic* type) is introduced. This force is felt strongly at near distances and weakly at long distances and is given by the equation:

$$\vec{F}^{r} = K_{2}(q_{i}/d)^{2} \frac{\vec{r_{i}} - \vec{r_{j}}}{|\vec{r_{i}} - \vec{r_{j}}|}$$

(4)

where  $K_2$  is a constant,  $q_i$  is a constant that depends on the size or the optimal distance between the objects that repel one another and d is the distance between the two objects in question. For example, in the case of a pin being rejected by the center of the cell,  $q_i = R$ , where R is the average distance between the cell center and the cell boundary.

### **3.3. Filling Forces**

When just the attractive and the repulsive forces are used, the placement obtained has cell overlaps. In order to obtain a feasible placement, a "filling" force is used. This force was proposed by Eisenmann and Johannes [9] and later enhanced by Mo *et al* in [8]. The placing area is covered by a grid with the bin size given by the minimum cell size. In order to reduce the execution time, the force is calculated just for the center bin of a cell without losing the accuracy. In [8] the force on a cell is the sum of the forces calculated for all the bins covered by the cell. The force is proportional to the number of cells that occupy a specific grid bin.

<sup>&</sup>lt;sup>1</sup>Note that our star model is different from the star model used in [8]. In [8], for each net, an additional point is inserted to which the source and sinks are connected. Our model has one-to-one correspondence with the star interconnect topology.

#### 3.4. Finding the Equilibrium Positions

Generally, the forces are used to determine new positions of the objects by using the following formula:

$$\vec{r}_{i\ new} = \vec{r}_i - k_r \frac{\partial \sum \vec{F}_i}{\partial \vec{r}}$$

(5)

where  $k_r \in [0.1, 0.5]$  is a constant which changes randomly in each iteration in order to avoid oscillations and  $\sum \vec{F_i}$  is the sum of forces applied on object *i*.

When the derivative of forces is not easy to compute (when filling forces are used), the new cell position is found using the same method as in [8]. The center of the cell will move in the direction of the force:

$$\vec{r}_{center} = \begin{cases} \vec{r}_{center} + k_c \vec{F}_c & |\vec{F}_c| < f_{lim} \\ \vec{r}_{center} + k_c f_{lim} \frac{\vec{F}_c}{|\vec{F}_c|} & |\vec{F}_c| \ge f_{lim} \end{cases}$$

(6)

where  $f_{lim}$  is a constant that has a bigger value at the beginning of the algorithm (the cells can find a good position) and a smaller value at the end (the position found is not disturbed too much),  $\vec{F}_c = \sum \vec{F}_i$  the sum of all forces applied on the center of cell C, and  $k_c$  is a unit conversion constant.

## 4. Proposed Approach

The input is an RT-level netlist that connects a set of module instances of varying sizes. Hard macrocells are used, i.e., cells have fixed aspect ratio and fixed pin positions. Nets are clustered using clique partitioning followed by a net-cluster based floorplanning by simulated annealing. Detailed macrocell placement is then achieved using force-directed method. The key idea is that the forces on the terminals of nets will determine the final macrocell placement. The optimal I/O pin placement is carried out by bipartite minimum-weight matching. The bipartite graph BG = (V, E) is built such that  $V = P \cup S$  where a vertex  $p \in P$  represents a cell pin that needs to be connected by an I/O net, and a vertex  $s \in S$ , represents a valid I/O slot. The weight of an edge  $(p_i, s_k)S$  (representing the possibility of mapping I/O net corresponding to the pin  $p_i$  to slot  $s_k$ ) is determined by the quadratic distance between  $p_i$  and  $s_k$ . The I/O pin placement is not performed in every iteration. It is performed more often in the beginning and less often as the design converges. The final placement is then fed into CADENCE Silicon Ensemble to perform global and detailed routing.

### 4.1. Net Clustering

In order to group nets that have to be routed in the same region, clique partitioning is carried out on the Net Dependency Graph  $\mathcal{G}$ . We employed a variation of the clique partitioning heuristic proposed by Tseng and Sieworick [3]. The modification enables the heuristic to form maximum weighted cliques.

Due to the method used to build  $\mathcal{G}$ , a net belongs just to one cluster, but the cells can be divided into two categories:

### Figure 2. Detailed view of the iterative improvement placement

cells that belong to a cluster (all the nets that connect it are in the same cluster) and common cells.

After the net clusters are generated, they have to be placed such that the area of the chip is minimum. Also, because there are cells connected by nets which belong to different clusters, the distance between these clusters must be minimized. These two objectives are realized by performing a cluster level floorplanning. Given a net cluster (say  $N_i$ ), its area is a sum of (1)  $A_{no-share}$ , the area of the macrocells that belong only to  $N_i$ ; and (2)  $A_{share}$ , the area of the common macrocells that is shared with other clusters. The area of the shared cells is distributed equally amongst the clusters. The derivation of the floorplan is based on the algorithm proposed by Wong and Liu [5]. The valid moves are: operand exchange, operator exchange, complementation of an operator chain, and aspect ratio variation.

## 4.2. Net & Cell Placement: An Iterative Improvement Approach

A detailed view of the approach is shown in Figure 2. Initially, the terminals of the nets are randomly placed in the cluster where the net is included. The average net size D (av-

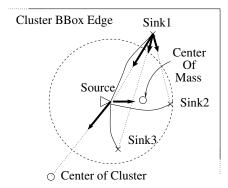

Figure 3. Net-level forces on the terminals of a net

erage estimated distance from source to any sink) is defined as a fraction of the cluster bounding box dimension. A cell center position is determined as the average position of all the net terminals that belong to the cell. The center of a common cell is placed on a position equally distant from the corresponding cluster centers. Then, the following tasks are performed:

(a) Net Terminal Placement: Forces on net terminals are computed and used to find the equilibrium positions of the terminals. These forces will be presented in Section 4.3.

(b) Cell Placement: Our method has two phases given by the type of forces exerted on cell centers.

**Phase 1.** During phase 1, each cell is attracted towards its net terminals. Also, rejection forces are considered between cells that belong to the same cluster in order to reduce the overlaps. On the common cells there are additional attraction forces between the cell center and the center of the clusters, trying to keep them in an optimal position.

**Phase 2.** During phase 2, the overlaps that may be existent after phase 1 are minimized in order to obtain a feasible placement. Besides the attractive forces towards the terminals, filling forces are used (Section 3.3). The rejection forces from phase 1 are not used anymore.

After the phase 1, in order to obtain the optimal cell orientation, all eight cell orientations (arising due to cell rotation and cell flip) are exhaustively considered. The optimal cell orientation is found by minimizing the sum of the distances between each net terminal and its corresponding fixed position on the cell boundary.

The user may select and prioritize one or more nets for wire length optimization. The nets, particularly on the critical path of the design, can be given to the placement tool for higher optimization. For each prioritized net, the coefficients of the forces between the source and the sinks of the net are scaled up to reflect the net priority.

#### 4.3. Net Terminal Placement

**Net Length Optimization Forces on a Net Terminal.** The forces defined on net terminals try to optimize the length of the nets. They depend on the type of terminal (source or sink)

on which they are applied. Consider a net  $(n_s)$  in a cluster as shown in Figure 3 with its source terminal at the center of the net. The center of the cluster and the center of mass of the terminals are also shown. The force on the source terminal *s* is given by:

$$\vec{F}_{n}(s) = \vec{F}_{n}^{a}(s, Ctr(\mathcal{N}_{s})) + \vec{F}_{n}^{a}(s, CM(Sinks(n_{s}))) + \sum_{\substack{n \in \mathcal{N}_{s} \\ n \neq n_{s}}} \vec{F}^{r}(s, Source(n))$$

(7)

The first term is an attractive force that pulls the source pin towards the center of the cluster. This force is responsible for keeping  $n_s$  within the area allocated to the cluster. The second term is an attractive force that pulls the source pin towards the center of mass of the sinks of the net. The third term is a small repulsive force between s and the sources of other nets in the cluster that is needed in order to avoid the overlap of the net sources of the cluster.

Consider the sink terminal  $t \in Sinks(n_t)$  of the net  $n_t$  in Figure 3. The force on a sink terminal t is given by:

$$\vec{F}_n(t) = \vec{F}_n^a(t, Source(n_t)) + \sum_{\substack{j \in Sinks(n_t) \\ t \neq j}} \vec{F}_n^a(t, j)$$

(8)

The first term an attractive force between the sink and the source of the net  $n_t$ . The second term is a small cumulative attractive force between t and the rest of the sinks in the net which tries to reduce the sink dispersion.

**Cell Feasibility Forces on a Pin.** Because the net terminals can move freely and are not locked on a macrocell boundary, the pins of a cell may not lie on the periphery of the cell. In order to find a feasible placement, the cell feasibility forces are introduced.

Consider the pins of a cell, C. The force acting on a pin p of a cell is given by:

$$\vec{F}_{c}(p) = \vec{F}_{c}^{r}(p, Center(c)) + \vec{F}_{c}^{a}(p, Center(c)) + \sum_{\substack{j \in Pins(c) \\ i \neq n}} \vec{F}_{c}^{r}(p, j)$$

(9)

The first term is a force that causes the center of the cell to repel the pin. This kind of force is dominant for the pins which fall inside the cell boundary. The second term is a force that causes the cell center to attract the pin. This component is dominant if the pin position falls outside the cell boundary. The third term is a cumulative repulsive force exerted by the rest of the pins of the cell C on pin p. This force avoids the collapse of multiple pins to the same position.

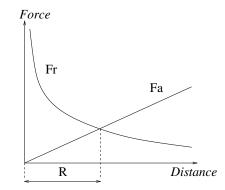

Figure 4 depicts the first and second type of forces. At closer distances from the cell center, the repulsive force  $\vec{F}^r$  dominates and at farther distances,  $\vec{F}^a$ . A judicious mixture of attractive and repulsive forces can be used to achieve good positions of pins on the cell boundary.

| Total wire length |           |           | Longest wire length |           |           | Bounding box area |                     |                     |         |

|-------------------|-----------|-----------|---------------------|-----------|-----------|-------------------|---------------------|---------------------|---------|

| Design            | SE        | Ours      | % Re-               | SE        | Ours      | % Re-             | SE                  | Ours                | % Re-   |

|                   | $(\mu m)$ | $(\mu m)$ | duction             | $(\mu m)$ | $(\mu m)$ | duction           | $(\mu m \ge \mu m)$ | $(\mu m \ge \mu m)$ | duction |

| Compress          | 47,617    | 28,770    | 39.5%               | 810       | 551       | 31.9%             | 550 x 550           | 480 x 580           | 7.9%    |

| Find              | 111,281   | 99,581    | 10.5%               | 1759      | 1186      | 32.6%             | 800 x 800           | 1000 x 730          | -14.0%  |

| Fifo              | 149,313   | 101,242   | 32.2%               | 1723      | 1285      | 25.4%             | 900 x 900           | 780 x 1060          | -2.0%   |

| Elliptic          | 357,787   | 317,867   | 11.1%               | 3951      | 2936      | 25.7%             | 1250 x 1250         | 1490 x 1100         | -4.9%   |

| Shuffle           | 143,378   | 113,735   | 20.7%               | 2499      | 1258      | 49.6%             | 1200 x 1200         | 1020 x 1150         | 18.5%   |

| Average %         | Reduction |           | 33.0%               |           |           | 22.8%             |                     |                     | -1.1%   |

Table 2. Experimental results.

Table 1. Design characteristics, netclustering data ( $|\mathcal{N}|$ =Number of net clusters,  $\mathcal{M}$ =Maximum number of nets in a cluster), and execution time.

| Design   | Cells | Nets | $ \mathcal{N} $ | $\mathcal{M}$ | ΙΟ   | Exec. |

|----------|-------|------|-----------------|---------------|------|-------|

|          |       |      |                 |               | pins | Time  |

| Compress | 35    | 174  | 6               | 9             | 51   | 85s   |

| Find     | 58    | 268  | 20              | 41            | 90   | 225s  |

| Fifo     | 63    | 296  | 14              | 9             | 112  | 249s  |

| Elliptic | 94    | 531  | 14              | 33            | 212  | 515s  |

| Shuffle  | 104   | 488  | 10              | 10            | 314  | 474s  |

#### 4.4. Forces on Cell Centers

The terminals, which can move freely, determine the cell positions, but can lead to a placement with cell overlaps. The overlaps must be eliminated while keeping the cells in position so that the wire lengths do not increase significantly. This is done using forces on cell centers and finding the equilibrium positions.

The overall force on the center of a cell  $C_i$  is:

$$\vec{F}_{C}^{i} = \sum_{j=0}^{N_{p}} \vec{F}_{C_{i}}^{a} + \vec{F}_{C_{i}}^{r}$$

(10)

where  $N_p$  is the number of pins of cell  $C_i$ . The first term is the attraction force between the center of the cell and the net terminals  $p_j$  that should be placed on the boundary of the cell using Equation 2. The attraction coefficient  $K_1$  is updated using Equation 3.

The second term is one of the following two types of forces that will help remove the cell overlaps: (1) Repulsive forces between cells in the same cluster that are proportional to the amount of the overlap as described by Equation 4 - used during phase 1. In this case, the coefficient  $q_i$  is  $q_i = R_i + R_j$ .  $R_i$ and  $R_j$  are the radii of the cells  $C_i$  and  $C_j$ ; (2) Filling forces as described in Section 3.3 - used during phase 2.

A halo is added around each macrocell that not only helps in reducing the overlaps, but also helps in efficient routing as well as the overall chip area minimization. On each side, the width of the halo is proportional to the cell connectivity, i.e., the number of pins on that side.

Figure 4. Illustration of attractive and repulsive forces on pins of a cell. R is the equilibrium distance.

### **5. Experimental Results**

We report results for five RTL designs [14] (See Table 1): (1) *Compress* - a look-up table based compression algorithm; (2) *Find* - a sort-and-search chip; (3) *FIFO* - a First In First Out Queue; (4) *Elliptic Wave Filter* - a fifth-order filter; (5) *Shuffle Exchange Network* - implementation of "forward pass" functionality of a high speed reconfigurable shuffle-exchange network [6].

The results are compared with those produced by the CA-DENCE Silicon Ensemble (SE version 5.3). In both cases, the global and detailed routing is performed by Silicon Ensemble. The designs were implemented in  $0.35\mu m$  technology with three wiring layers and over-the-cell routing. The results were obtained on a SUN ULTRASPARC 30 Workstation with 200MHz processor and 128MB RAM. The placement program is written in C++.

Table 2 compares the total wire length, the longest wire length, and the bounding box area of the designs. The longest wire length percentage reduction range of 25.4%–49.6%, and the average percentage reduction of 33.0% highlight the effectiveness of the proposed approach. The range of total wire length percentage savings is 10.5%–39.5%. The average percentage reduction is 22.8%. Clock, reset, power, and ground nets are excluded as they need to be handled separately due to their connectivity to every cell in the design.

For two benchmarks (Compress and Shuffle) the area is significantly reduced, while for three benchmarks (Find, Fifo,

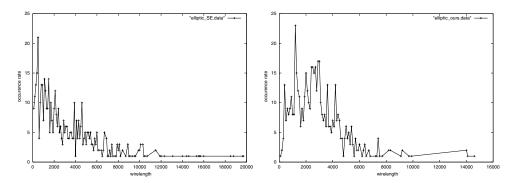

Figure 5. Wire length distribution in Elliptic design produced by SE (left plot) and by the proposed approach (right plot).

and Elliptic), it has increased. The maximum area increase is 14% in case of Find design. This is a reasonable penalty paid for a reduction of 32.6% in the longest wire length and reduction of 10.5% in the total wire length.

Global net length optimization is at the cost of an *increase* in the average wire length of the local nets. Figure 5 shows the wire length distributions for the Elliptic design. We observe that: (1) both distributions agree with the bi-modal wire distribution model suggested by Bakoglu [2]; (2) there is a significant decrease in the number of global nets; and (3) the number of local nets has increased. The increase in wire length of local nets implies an increase in their delay which does not affect the overall chip delay.

The net prioritization is demonstrated by considering four nets (n1-n4) whose lengths are above the average length for Compress design. Table 3 shows the wire lengths without any prioritization (column two), when n1 and n2 are prioritized (column three), and when n3 and n4 are prioritized. The reduction range is between 32.3% and 69.1%.

#### 6. Conclusions

In this work, a net-clustering based macrocell placement has been proposed. The novelty of the approach lies in using the new net model and cluster information to derive a rough floorplan. The significant wire length reductions across the benchmark set (with reasonable area penalty) may be attributed to the following factors: (1) Clustering of interdependent nets and floorplanning gives a very good starting point for the force-directed net terminal placement and subsequent macrocell placement; (2) Pin-level force formulation is very

| Table 3. Demonstration of n | net prioritization. |

|-----------------------------|---------------------|

|-----------------------------|---------------------|

|                  | Wire length ( $\mu m$ ) |                              |                              |  |  |

|------------------|-------------------------|------------------------------|------------------------------|--|--|

| Net Id<br>Net Id | Without<br>Priority     | n1, n2<br>Higher<br>Priority | n3, n4<br>Higher<br>Priority |  |  |

| nl               | 459                     | 250                          | 68                           |  |  |

| n2               | 337                     | 104                          | 111                          |  |  |

| n3               | 328                     | 316                          | 222                          |  |  |

| n4               | 48                      | 199                          | 20                           |  |  |

effective in optimizing the net lengths; (3) The bipartite minimum weight matching is effective in reducing the nets involving I/O pins; (4) User prioritization of nets can help optimize the nets on the critical path of the design and hence the overall chip delay characteristics.

#### References

- -. "The National Technology Roadmap for Semiconductors". SIA (Semiconductor Industry Association), 1997.

- [2] H. B. Bakoglu. Circuits, Interconnections, and Packaging for VLSI. Addison Wesley Publishing Company, 1990.

- [3] C. Tseng and D. P. Siewiorek. "Facet: A Procedure for the Automated Synthesis of Digital Systems". In 20th ACM/IEEE DAC, pages 490–496, 1983.

- [4] J. Cong and A. Kahng. "Net Partitions Yield Better Module Partitions". In 29th DAC, pages 47–52, June 1992.

- [5] D. F. Wong and C. L. Liu. "A New Algorithm for Floorplan Design". In *Proceedings of the DAC*, pages 101–107, 1986.

- [6] Electronic Products. "Novel IC Shuffles Parallel Processing Data". pages 42–50, August 1986.

- [7] J. C. et. al. Performance optimization of vlsi interconnect layout. In *Integration, the VLSI Journal*, pages 1–94. 1996.

- [8] F. Mo, A. Tabbara, and R. K. Brayton. "A Force-Directed Macro-Cell Placer". In *Proceedings of ICCAD*, pages 177– 180, 2000.

- [9] H. Eisenmann, F.M. Johannes. "Generic Global Placement and Floorplanning". In 35th DAC, pages 269–274, 1998.

- [10] A. Kahng. "Fast Hypergraph Partition". In 26th DAC, pages 762–766, June 1989.

- [11] L. T. Pillage and R. A. Rohrer. "A Quadratic Metric with a Simple Solution Scheme for Initial Placement". In *Proceedings of DAC*, pages 324–329, 1988.

- [12] J. M.Kleinhans, G. Sigl, F. M.Johannes, and K. J.Antreich. GORDIAN: VLSI Placement by Quadratic Programming and Slicing Optimization. *IEEE Trans. on CAD*, 10(3):356–365, March 1991.

- [13] A. Srinivasan, K. Chaudhary, and E. S.Kuh. RITUAL: A Performance-Driven Placement Algorithm. *IEEE Transactions on Circuits and Systems -II: Analog and Digital Signal Processing*, 39(11):825–839, November 1992.

- [14] J. Roy, N. Kumar, R. Dutta, and R. Vemuri. DSS : A Distributed High-Level Synthesis System. *DNT*, pages 18–32, June 1992.