# Model Based Layout Pattern Dependent Metal Filling Algorithm for Improved Chip Surface Uniformity in the Copper Process

Subarna Sinha, Jianfeng Luo and Charles Chiang Synopsys Inc., Mountain View, CA, USA Email: { subarna, jianfeng, clc}@synopsys.com

## Abstract

Thickness range, i.e. the difference between the highest point and the lowest point of the chip surface, is a key indicator of chip yield. This paper presents a novel metal filling algorithm that seeks to minimize the thickness range of the chip surface during the copper damascene process. The proposed solution considers the physical mechanisms in the damascene process, namely ECP (which is the process used to deposit Cu in the trenches) and CMP (which is the process used to polish Cu after ECP), that affect thickness range. Key predictors for the final thickness range, which is the thickness range after ECP & CMP, that can be computed efficiently are identified and used to drive the metal filling process.

To the best of our knowledge, this is the first metal filling algorithm that uses an ECP model among other things to guide metal filling. Experimental results are very promising and indicate that the proposed method can significantly reduce the thickness range after metal filling. This is in sharp contrast with the density-driven approaches which often increase the thickness range after metal filling, thereby potentially adversely impacting yield. In addition, the proposed method inserts significantly smaller amount of fill when compared to the densitydriven approaches. This is desirable as it limits the impact of metal filling on timing.

## 1 Introduction

Continued aggressive scaling down of VLSI feature size has necessitated better planarization of chip surface topography to improve both functional and parametric yield. Planar chip surface topography is necessary to satisfy the stringent depth of focus (DOF) requirements of the lithography process as nonplanarity can eat into the DOF budget. In addition, large metal and dielectric thickness variations can produce resistance and capacitance variations which can adversely impact chip timing. The depth of focus (DOF) budget and interconnect thickness values are continually shrinking with each technology node, making the variations induced by surface non-planarity increasingly significant. Hence, it is extremely important to reduce the systematic topography variations during the fabrication process. Thickness range, which is the difference between the highest point and the lowest point of the chip surface, is a measure of the planarization of chip surface topography and is a key indicator of chip yield. In this paper, we propose a novel algorithm to reduce the thickness range of the chip and thereby increase yield.

To better understand the proposed algorithm, we begin with a brief description of the key processes in dual-damascene that affect the thickness range of the chip surface. Electroplating (ECP) and Chemical Mechanical Polishing (CMP) are two enabling processes that are widely used in sub-130 nm ICs for the fabrication of copper (Cu) interconnects. During the Cu metalization process, trenches for wires or holes for vias are first etched in the dielectric materials. ECP and CMP are then applied in a sequential fashion to fill up the trenches and holes with Cu and remove the overburden Cu from the dielectric surface, leaving Cu in the trenches as interconnect wires or vias. In general, the Cu and dielectric thickness values after the Cu metalization process are not uniform across the chip. Instead, systematic variations in the final chip surface topography are observed. One of the major contributors to these topography

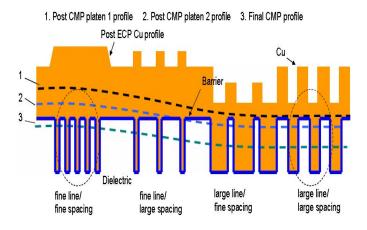

Figure 1. Profile after ECP and CMP.

variations is from the ECP process. Figure 1 shows an example of a typical topography after ECP. The figure also shows that the variations in the ECP topography are propagated through the CMP steps, thereby affecting the final surface topography, as shown by the dashed curve labeled '3' in Figure 1.

The thickness variations of the chip surface are usually dependent on variations of key layout characteristics. The commonly used approach to reduce thickness variations is to insert electrically inactive features (also known as metal fills or dummies) in the empty spaces in the layout to reduce the variations in key layout characteristics. This process is typically called metal filling or dummy filling. In the past, the primary objective of metal filling was to reduce the density difference between different regions in the layout. This can be attributed to the fact that most metal filling solutions were originally developed to obtain better planarization after inter-layer dielectric (ILD) CMP, a process which was used when Al was the interconnect material of choice. Previous work by Ouma [8] shows that the ILD thickness is primarily a function of the underlying density. Hence, it sufficed to have a metal filling algorithm that sought to uniformize the density differences between the different regions of the layout to attain smaller final thickness range. This is no longer true for the Cu metalization process. A variety of layout parameters (besides density) can affect the final surface topography after CMP. Figure 1 shows an example where two regions with the same density (highlighted by the two circled regions) could end up with very different topographies. Hence, it is no longer sufficient to reduce only the density differences between the different regions in the layout during metal filling. In fact, pure density-driven metal filling can often increase the final thickness range, a claim that will be supported by experimental results in a later section.

The primary contributions of this paper are as follows:

1. Key reliable predictors of the final thickness range based on the physical mechanisms of Cu ECP and CMP are identified and used to guide the metal filling process. These predictors can also be efficiently computed. This makes it possible to have a high quality and yet practically feasible metal filling solution.

- 2. Use of smooth ECP topography as an objective enables parameters besides density to be considered during metal filling. In particular, it enables accounting for perimeter effects during metal filling, thereby making the proposed solution strongly layout pattern dependent. To the best of our knowledge, the proposed solution is the first solution that consider ECP effects during metal filling.

- 3. Experimental results indicate that the thickness range reduction obtained using the proposed scheme (as measured by a CMP simulator) is significantly better than that obtained using the commercially available density-driven solutions. In addition, the density-driven solutions can often increase the thickness range after metal filling, a scenario that never happens with the proposed solution.

The paper is organized as follows. Section 2 provides an overview of the Cu ECP and CMP processes and key details of our in-house CMP simulator. A brief summary of the density-based metal filling solutions is provided in Section 3. It also presents data to illustrate that density is not the only layout parameter that affects planarization after Cu CMP. Section 4 discusses a few key reliable predictors of final thickness range that can be efficiently computed and hence can be used to guide metal filling. The details of the proposed metal filling algorithm is provided in Section 5. Section 6 provides experimental validation of the proposed algorithm. We end with conclusions and directions for future work in Section 7.

#### 2 Overview of Cu ECP and CMP

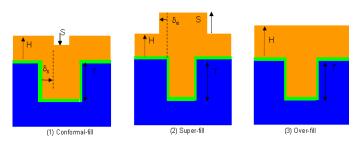

Electroplating or ECP is the process by which Cu is deposited in the trenches in the damascene process. Figures 2(1)-(3) show the three types of topography for a single wire [1] at the end of the ECP process. The two output variables that represent the final topography are the array thickness H, and the step height  $S^1$ . In case (1), the Cu above the dielectric is higher than that above the trench, resulting in a positive step height S. In addition, the Cu trench width is smaller than the feature trench width in the dielectric by amount  $\delta_s$ , as shown in Figure 2 (1). This case is called conformal-fill. In case (2), the width of the Cu above the feature trench is larger than the feature trench width by amount  $\delta_e$ . This is the differentiating property for case (2). This case is called super-fill. In case (3), the Cu surface is flat after deposition (S=0 in this case). This case is called over-fill. The above discussion can be generalized to multi-wires as well.

To determine the ECP profile of a layout, the layout is first meshed into non-overlapping tiles. The tile size is typically

10 microns by 10 microns to obtain a good compromise between accuracy and computational efficiency. The dependence of thickness on the the layout parameters varies with the case of the tile. Two key parameters affecting the case of a tile, its array thickness and its step height are the density and perimeter of the layout features in the tile and its neighboring tiles. The radius of the region surrounding a tile that can affect its ECP topography ranges between 20-30 microns and is henceforth referred to as its *ECP radius of influence*. An ECP model, like the one proposed by Luo et. al [1], can be used to determine ECP thickness values for the tiles in the layout. The ECP model in [1] uses analytical equations to determine the ECP thickness of a tile. For a detailed exposition on ECP modeling, the reader is referred to [1]. In this paper, the ECP model is used as a black box, i.e. layout parameters are input to the model and the case and thickness values of the tiles are determined.

After ECP, CMP is used to remove Cu from the surface above the dielectric, leaving Cu in the dielectric trenches as interconnects. Cu CMP is usually processed sequentially by three steps (polishing platens), each with its own consumable mixture. Typically, bulk copper is removed in the first step, barrier layer is removed during the second step and a dielectricbuffing<sup>2</sup> step is carried out in the third step. In Cu CMP, insitu endpoint-detection of the desired remaining thickness is applied in polishing steps 1 and 2 to control the completion of the polishing. Polishing time is often used to control the completion of step 3.

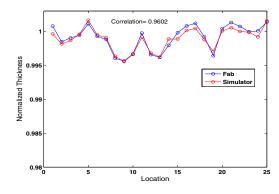

To simulate the layout dependency of Cu thickness variation after CMP, an in-house CMP simulator was developed. The simulator includes four components: an ECP topography model, platen 1 polishing model, platen 2 polishing model and platen 3 polishing model. Typical process parameters from a fab were input to the simulator. The simulator is quite comprehensive in its modeling and can capture both typical CMP non-uniformities such as dishing, erosion and multi-layer accumulative effects and atypical CMP non-uniformities such as edge erosion and isolated line dishing. Calibration results show that the simulator has a high level of accuracy in predicting final thickness values. Figure 3 provides an illustration of the excellent correlation between the thickness values predicted by our simulator when compared to the thickness values for the same locations obtained from a fab (only the normalized thickness values are shown for privacy reasons).

Figure 3. Correlation between our simulator and fab data.

## **3** Current Metal Filling Solutions

In this section, we provide a brief overview on previous work in metal filling. As stated before, the objective of prior

<sup>&</sup>lt;sup>1</sup>The array thickness H is defined as the thickness of Cu above the dielectric after deposition; the step height S is defined as the difference between the Cu thickness above the dielectric and the Cu thickness above the trench in the dielectric. When the thickness of Cu above the dielectric is larger than the thickness of Cu above the trench, the step height S is a positive value. Otherwise, it is a negative value.

<sup>&</sup>lt;sup>2</sup>Dielectric buffing is a step used to ensure all barrier materials are cleared from the dielectric surface.

work in metal filling was to achieve better density uniformity. Previous work can be grouped into two major categories: rule-based and model-based. Rule-based solutions, which are widely used in current EDA commercial tools, use guidelines from the fabs to insert metal fills such that the minimum and maximum density of the layout are within certain bounds and the density of a set of windows, the union of which can cover the entire layout, is within certain bounds. The layout is typically divided into windows and two adjacent windows overlap with each other by a pre-determined amount (usually equal to half the window size) to have a greater control on the density. Most model-based solutions, on the other hand, use an ILD thickness model to guide the metal filling process. The ILD thickness model states the dielectric thickness at a location is proportional to the convolution of the metal density and a suitable weighting function which considers the deformation of the polishing pad during polish [8]. There is a wealth of literature on model-based metal filling solutions for ILD CMP. All of them seek to minimize the difference between the largest and smallest values of the convolved metal density across all locations of the layout. Some of them formulate the above problem as an LP solution [2,3], whereas others use heuristic based solutions [4-6]. In [7], Tian et. al. proposed a filling solution tuned to the Cu CMP process. The solution, however, focuses primarily on metal density and does not consider the impact of ECP. If the primary goal is to reduce the density difference between the different regions in the layout, rule-based solutions are known to suffice and are the most commonly used solutions.

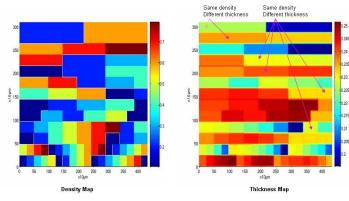

The inadequacy of density in faithfully predicting Cu CMP topography can be illustrated with a simple experiment. The CMP simulator was run on a test-chip which had patterns with different density and perimeter combinations. The test-chip included patterns with the same density and different perimeters as well as patterns with different densities and perimeters. Figure 4 shows the density map and the thickness map

Figure 4. Topography Results using CMP Simulator.

for the test-chip. It can be seen that different regions with the same density have different final thickness values after Cu ECP&CMP. In addition, there is prior experimental data [9] that demonstrates that regions with the same density could have varying metal thickness values after Cu CMP. Based on the above results, it can be concluded that it is not sufficient to consider only density during metal filling for copper processes. In the sequel, Cu ECP and CMP are simply referred to as ECP and CMP, respectively.

## 4 Predictors of Final (Post-CMP) Thickness Range

To develop a metal filling solution that can consistently reduce the thickness range, one option would be to tightly integrate the simulator with the filling algorithm. In this scenario, the filling algorithm would invoke the simulator as it explored the solution space and evaluated various filling options. However, the run-time for such an algorithm would be prohibitive due to multiple calls to the simulator, making it computationally infeasible. Hence, reliable predictors of the final thickness range that can be efficiently calculated while being fairly representative are required. In this section, these predictors are identified.

### 4.1 ECP Thickness versus Final Thickness

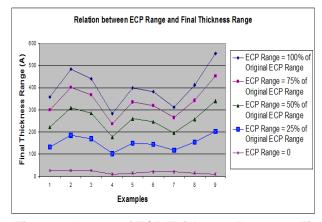

It was noted in a previous section that surface nonuniformities after ECP can propagate through the CMP platens and result in a non-uniform final topography. This suggests that a smaller ECP thickness range (i.e. a more flat ECP topography) for a given design would result in a smaller final thickness range.

Figure 5. Impact of ECP Thickness Range on Final Thickness Range.

To experimentally test this thesis<sup>3</sup>, we modified the ECP topography model in our in-house simulator to produce progressively smoother ECP topography without changing the subsequent CMP platens. The ECP model was run with five different settings to produce ECP profiles with the following ranges for a given design: original range (which is the ECP thickness range with no change to the ECP model), range = 75% of original ECP range, range = 50% of original ECP range, range = 25%of original ECP range and range = 0% of original ECP range (i.e. flat profile after ECP). For each setting, the ECP thickness value of each tile was scaled equally by the same ratio. The result of running the CMP simulator with five different settings for the ECP model on a set of 65nm and 90nm designs is presented in Figure 5. It can be seen that for the same layout as the ECP thickness range is reduced, the final thickness range monotonically reduces by a substantial amount. The above results clearly indicate that the range of the incoming ECP profile does have a strong impact on the final thickness range and a smaller ECP thickness range results in a smaller final thickness range.

Thus, using ECP thickness range minimization as an objective during metal filling has a very high likelihood of resulting in a smaller final thickness range for the metal filled design than the original. To the best of our knowledge, no metal filling solutions available today consider the dependency between ECP thickness and final thickness during metal filling.

<sup>&</sup>lt;sup>3</sup>The absence of a closed-form analytical equation for final thickness makes it very hard to mathematically derive the relationship between ECP thickness range and final thickness range.

## 4.2 Effective Density versus Final Thickness

For more uniform ECP profiles, there is a dependence between the final thickness and the density [10]. The thickness in such cases is inversely proportional to the *effective density*, which is a function of the density. The effective density denoted as  $\rho$  is equal to the convolution of the density and a weighting function and is computed as follows:  $\rho = d \otimes w$  where d is the metal density and w is the weighting function that accounts for the deformation of the polishing pad [8]. Typical values of the weighting function for (Cu) CMP range between 40-120 microns [11] and is henceforth referred to as the *CMP radius of influence*.

A smaller effective density range, i.e. the difference between the largest effective density and the smallest effective density across all tiles of a layout, translates to a smaller thickness range if the incoming ECP profile is quite uniform. *Thus a smaller effective density range for the same ECP thickness range after metal filling will result in a smaller final thickness range*.

It should be noted that both the ECP thickness values and the effective density values can be calculated very efficiently as they are single step analytical computations. Thus, it is computationally feasible to develop a high quality metal filling solution that is guided by these predictors.

#### 5 Proposed Metal Filling Algorithm

The details of the proposed metal filling algorithm based on the predictors outlined in the previous section is discussed here. The key objective of the algorithm is to minimize the final thickness range of the chip surface. The algorithm uses an ECP model, among other things, to guide the filling process. The ECP thickness at a location depends on both the density and perimeter of the layout features in the areas surrounding it [1] and hence is pattern dependent (for instance, it is necessary to distinguish between fine line/fine spacing and wide line/wide spacing even if they have the same density). Hence, we will refer to the proposed algorithm as the *model-based layout pattern dependent (MBLPD)* algorithm. The *MBLPD* algorithm has to manipulate both the density and the perimeter of the layout to achieve the best possible final thickness range reduction.

The *MBLPD* algorithm is divided into two main steps: *parameter assignment* and *fill placement*. The key objective of the *parameter assignment* step is to determine the best density and perimeter targets for all the tiles of the layout such that the final thickness range is minimized. This step takes both the ECP profile and the effective density into account to determine the targets. The size of the tile is set to be the same as the tile size for the ECP model being used. During *fill placement*, the fills are inserted in the layout. The fills are selected to best match the density and perimeter targets computed in the assignment step for each tile.

In the MBLPD algorithm, parameter assignment and fill placement are de-coupled for runtime efficiency. However, to increase the likelihood that fill placement can find the fills necessary to satisfy the targets assigned by parameter assignment, both steps use the same input information about the different types and configurations of fills that can be inserted. This ensures that the parameter assignment step only determines density and perimeter targets that are realistic and based on actual fill patterns that can be inserted during the fill placement step. Information related to the types and configurations of the fills is stored in a library of fill patterns. Each element of the library represents a particular pattern of fills and is denoted as  $(l, w, x_s, y_s)$ . Here *l* denotes the length of the fill element, w denotes the width of the fill element,  $x_s$  and  $y_s$  denote the the spacing between fill elements in the horizontal and vertical direction, respectively. The library used in our experiments has  $\sim 2000$  unique fill elements. Note that the fill pattern can contain multiple instances of a fill element. The values of l, w,

$x_s$  and  $y_s$  are chosen such that the DRC rules and manufacturing and/or routing grid restrictions are satisfied. This ensures that the fill placement step only has to focus on achieving DRC correctness between signal wires and fills.

#### 5.1 Parameter Assignment

The key layout parameters that are considered in this step are density and perimeter since ECP thickness profile primarily depends on both these parameters and the effective density depends only on density. The parameter assignment step has two main steps.

In the first step, the objective is to minimize the thickness difference between the highest tile and lowest tile at the end of the ECP process. Throughout this step, the maximum ECP thickness of the layout is kept the same as the maximum ECP thickness of the original layout to avoid unnecessary filling. As described earlier, the relationship between the layout parameters and the ECP thickness of a tile depends on the particular case (conformal/super/over-fill) it falls under. This makes it hard to perform ECP thickness minimization as the tile thickness values may oscillate depending on their respective cases. In our solution, we tackle this issue by pushing all the tiles into the over-fill case before starting the minimization problem. A few key observations can justify this simplification. First, the ECP thickness within a tile is smooth in the over-fill case. Second, most of the tiles in typical industrial layouts fall into the (super/over)-fill cases and the super-fill tiles can be very easily converted to the over-fill case by inserting a small number of fills. Thus, the original design is perturbed very slightly during this conversion. Finally, an over-fill tile has a very high likelihood of remaining an over-fill tile if the only allowable layout modification is the insertion of fill patterns. Simple checks can be performed during the insertion process to ensure that an over-fill tile never moves to any other case. In fact, in all our examples, a tile never moved from the over-fill case to any other case. Thus, the likelihood of oscillation of cases is significantly reduced once the tiles are all over-fill tiles. At this point, there is a unique dependence of the ECP thickness on density and perimeter and the thickness difference between the different tiles can be more easily minimized.

The second step of the assignment algorithm seeks to reduce the effective density range between the tiles without increasing the ECP thickness range between the tiles. This step is necessary since the dependence of the final thickness on effective density increases as the ECP topography gets more uniform after the first step of parameter assignment. Further details of the parameter assignment step are provided below.

1. Layout Preparation:

- (a) Mesh the layout into non-overlapping tiles. Denote the *i*th tile as  $T_i$ .

- (b) Determine amount of available space, henceforth referred to as the fill-able area, in each tile for inserting fills based on DRC/routing rules. The ratio of fill-able area and total tile area multiplied with a weighting factor<sup>4</sup> gives the fillable density. The fill-able density of the tile  $T_i$  is denoted as  $d_i^F$ .

- (c) Based on the input fill pattern library, enumerate valid (density, perimeter) combinations that can be assigned to the tiles. The set of combinations is denoted as CS.

- 2. Reduce ECP Thickness Range:

- (a) Let the maximum ECP thickness of the design be  $H_{max}$ .

- (b) Determine case of each tile using an ECP model, for instance [1].

- (c) For each tile  $T_i$  in the layout:

- *i.* If  $T_i$  is in over-fill case, continue.

<sup>&</sup>lt;sup>4</sup>The weighting factor is less than 1 to account for the fact that the sum of areas of the inserted metal fills is usually less than the fill-able area due to spacing rules between fills.

- ii. Pick  $c = (d_k^c, p_k^c) \in CS$  such that  $d_k < d_i^F$  and the density and perimeter of  $T_i$  incremented by  $d_k^c$ and  $p_{k}^c$ , respectively, satisfies the conditions for the over-fill case. Typically, the element c with the smallest value of  $d_k^c$  that satisfies the above condition is picked. If no such c exists, then go to Step 3<sup>5</sup>.

- *iii.* Update  $d_i^F = d_i^F d_k^c$ .

- (d) For each tile  $T_i$ , unlock it and compute its priority as a function of the difference of its ECP thickness and  $H_{max}$ .

- i. Tiles with ECP thickness smaller than  $H_{max}$  or tiles surrounded by neighboring tiles with ECP thickness values smaller than  $H_{max}$  have higher priority.

- (e) Until (some tiles remain unlocked)

- *i.* Initialize  $TS \leftarrow \phi$ ;  $DT \leftarrow \phi$ .

- *ii.* Sort the tiles according to the priority function.

- *iii.* Until (all unlocked tiles are processed)

- A. Pick next tile in priority order. If the tile belongs to DT, continue. Else insert it in TS and add all the tiles within its ECP radius of influence into DT.

- iv. For each tile  $T_i \in TS$ , do

- A. Pick  $c = (d_k^c, p_k^c) \in CS$  such that  $d_k < d_i^F$  and (1) Difference between  $H_{max}$  and  $T_i$ 's ECP thickness after incrementing its density and perimeter by  $d_k^c$  and  $p_k^c$ , respectively, is minimized. (2) New ECP thickness values of  $T_i$  and the tiles in its ECP radius of influence are  $\geq$  their original thickness values<sup>6</sup> and  $\leq H_{max}$ .

- B. Update  $d_i^F = d_i^F d_k^c$  and lock  $T_i$ .

- v. Re-compute priorities of remaining unlocked tiles and go to Step 2(e).

- 3. Minimize Effective Density Range:

- (a) For each tile  $T_i$ , unlock it and compute its priority as a function of the difference of its effective density and the maximum effective density of the layout.

- i. Tiles with low effective density or tiles surrounded by neighboring tiles with low effective density have higher priority.

- (b) Until (some tiles remain unlocked)

- *i.* Initialize  $TS \leftarrow \phi$ ;  $DT \leftarrow \phi$ .

- *ii.* Sort the tiles according to the priority function.

- *iii.* Until (all unlocked tiles are processed)

- A. Pick next tile in priority order. If the tile belongs to DT, continue. Else insert it in TS and add all the tiles within its CMP radius of influence into DT.

- iv. For each tile  $T_i$  in TS, do

- A. Pick  $c = (d_k^c, p_k^c) \in CS$  such that  $d_k < d_i^F$  and (1) Difference between  $T_i$ 's effective density after incrementing its density by  $d_k^c$  and the maximum effective density of the layout is minimized. (2) New ECP thickness values of  $T_i$  and all tiles in its ECP radius of influence  $\geq$  their original thickness values and  $\leq H_{max}$ .

- B. Update  $d_i^F = d_i^F d_k^c$  and lock  $T_i$ .

- (c) Re-compute priorities of remaining unlocked tiles and go to Step 3(b).

The *fill-able* area computation in Step 1 can incorporate additional rules like fill to metal spacing, etc. In our algorithm, we require that all fills should be separated from the signal lines by at least  $2 \times$  minimum spacing to reduce the impact of RC coupling. In Step 2, tiles whose ECP thickness values are less than

$H_{max}$  are aggressively filled to bring their ECP thickness values as close to  $H_{max}$  as possible. In Step 3(b)(iv), after each set of tiles is assigned new density and perimeter values, it is possible that the effective density range might increase. Thus, an additional check is done after each such step and the density and perimeter values of all the tiles in the layout are temporarily saved only if the effective density range reduces after assignment to this set of tiles. The final solution returned by the algorithm is the best solution saved in the temporary storage at the end of Step 3.

#### 5.2 Fill Placement

The main objective in this step is to select and insert one or more fill patterns in each tile to ensure that the density and perimeter targets for each tile are satisfied as closely as possible. The fill placement step is very flexible and can insert fills either on the manufacturing grid or routing grid. Thus, the proposed algorithm can be used either in traditional place&route tools or in subsequent verification tools.

In order to match each tile's density and perimeter target with as much accuracy as possible, each tile  $T_i$ 's *fill-able* area  $F_i$  is decomposed into non-overlapping rectangles  $R_{ij}$ , where  $\sum_j R_{ij} = F_i$ . For each rectangle  $R_{ij}$ , a density and perimeter budget is computed: the density budget is simply equal to the {(target density-original density)×(area( $T_i$ )/area( $F_i$ )}; the perimeter budget is equal to the {(target perimeter - original perimeter)×area( $R_{ij}$ )/area( $F_i$ )}. Then, for each  $R_{ij}$ , the library element that matches its density and perimeter budget with the smallest possible error is determined and placed in the appropriate grids (for instance, the routing grid). The number of instances of the library element that produces the best match for the density and perimeter budgets is inserted.

The budgets are computed such that if the density and perimeter budgets of each  $R_{ij}$  is satisfied, the density and perimeter of the tile is equal to the target density and target perimeter, respectively. It can be shown that the density budget of each  $R_{ij}$  is always less than 1. This is because the difference between target density and original density is always less than area $(F_i)$ /area $(T_i)$ , since the additional assigned density of each tile is never greater than the tile's *fill-able density*.

#### 6 Experimental Results

Here, we present experimental results to validate the proposed *MBLPD* algorithm. It is compared with a commercially available metal filling solution from a major EDA vendor, which is density-driven. The metrics used to compare the two metal filling solutions are the final thickness range (i.e. the difference between the highest point and the lowest point on the chip surface after CMP) and the percentage of fill inserted. Our in-house CMP simulator is used to simulate the topography of each layer of the chip and the thickness range is computed. The percentage of metal fill is equal to the inserted fill area divided by the total area of the chip. We present data for seven layers for two industrial chips. The first one (henceforth referred to as D1) is  $0.7 \times 0.7 \ mm^2$  and the second one (henceforth referred to as D2) is  $1.78 \times 1.78 \ mm^2$ .

Table 1 provides a comparison between the different metal filling schemes. Columns *Design* and *Layer Num* specify the design and the layer number of the design, respectively. Column *Original* gives the final thickness range of the layer for the original design. The final thickness range for that layer after density-driven metal filling and the proposed model-based layout parameter-driven metal filling are given in Columns *Post\_DD\_MF* and *Post\_MBLPD\_MF*, respectively. All thickness ranges are reported in angstroms. Columns *FillArea\_DD* and *FillArea\_MBLPD* present the percentage of total area that is occupied by metal fills for the density-driven and the proposed algorithm, respectively. Columns *ED\_Org, ED\_MBLPD* and *ED\_DD* report the effective density range for the original

<sup>&</sup>lt;sup>5</sup>It should be noted that in all the examples we tried we were always able to convert all conformal/super-fill tiles to over-fill tiles.

<sup>&</sup>lt;sup>6</sup>This check is typically redundant since the ECP thickness value of an overfill tile rarely decreases after filling, another benefit of converting all tiles to over-fill.

| Design | Layer Num | Original $(A^o)$ | Post_DD_MF $(A^o)$ | Post_MBLPD_MF $(A^o)$ | FillArea_DD | FillArea_MBLPD | ED_Org | ED_MBLPD | ED_DD |

|--------|-----------|------------------|--------------------|-----------------------|-------------|----------------|--------|----------|-------|

| D1     | L1        | 232.21           | 125.39             | 107.17                | 2.58        | 1.44           | 0.25   | 0.17     | 0.05  |

| D1     | L2        | 281.11           | 316.12             | 177.87                | 13.52       | 4.52           | 0.10   | 0.08     | 0.08  |

| D1     | L3        | 399.31           | 302.02             | 313.78                | 15.38       | 5.51           | 0.17   | 0.10     | 0.07  |

| D1     | L4        | 382.17           | 324.17             | 309.01                | 15.62       | 5.86           | 0.21   | 0.16     | 0.06  |

| D1     | L5        | 313.95           | 262.38             | 251.33                | 13.49       | 5.24           | 0.22   | 0.12     | 0.06  |

| D1     | L6        | 413.86           | 285.04             | 293.6                 | 8.80        | 4.48           | 0.26   | 0.18     | 0.08  |

| D1     | L7        | 554.1            | 389.96             | 350.48                | 12.57       | 7.16           | 0.26   | 0.12     | 0.06  |

| D2     | L1        | 681.08           | 272.29             | 396.91                | 17.07       | 5.57           | 0.10   | 0.06     | 0.08  |

| D2     | L2        | 290.18           | 293.33             | 172.28                | 11.59       | 5.80           | 0.22   | 0.11     | 0.06  |

| D2     | L3        | 259.49           | 272.98             | 154.41                | 11.19       | 4.75           | 0.24   | 0.09     | 0.06  |

| D2     | L4        | 273.18           | 201.61             | 189.69                | 3.60        | 1.84           | 0.28   | 0.17     | 0.09  |

| D2     | L5        | 731.59           | 604.83             | 628.17                | 5.58        | 2.37           | 0.25   | 0.11     | 0.10  |

| D2     | L6        | 523.26           | 1208.99            | 307.85                | 13.94       | 6.79           | 0.21   | 0.20     | 0.11  |

| D2     | L7        | 1209.84          | 1503.60            | 1084.75               | 7.75        | 3.60           | 0.24   | 0.11     | 0.11  |

| Avg    | -         | -                | 6.6%               | 31.1%                 | 10.9%       | 4.7%           | -      | 39.5%    | 60.5% |

Table 1. Comparison of Different Metal Filling Results

layer, the layer after the *MBLPD* algorithm and the layer after the density-driven algorithm, respectively. A runtime comparison of the two algorithms is not provided as the code is still being optimized for runtime. However, the typical run-times for the *MBLPD* algorithm range between 100 seconds per layer for the smaller design and 600 seconds per layer for the larger design. These numbers are a very small fraction of the typical routing times. Hence, we believe that runtime should not be a factor limiting its application.

#### 6.1 Discussion

The results show that the proposed algorithm consistently reduces the final thickness range after metal filling whereas the density-driven approach can increase the final thickness range after metal filling. On average, the range reduction using the density-driven algorithm is 6.6%, where as the range reduction with our approach is 31.1%. In four cases, the density-driven approach significantly increases the final thickness range after metal filling. It should be noted, however, that the densitydriven algorithm is quite proficient in reducing the effective density range as per its original intention. It achieves an average effective density range reduction of 60.5%. Inspite of this, the poor thickness range reduction by the density-driven algorithm for these cases can be attributed to a significant increase in ECP thickness range<sup>7</sup> after filling. For the few cases in which the density-driven algorithm does better than the MBLPD algorithm, the density-driven approach obtains a better ECP thickness range reduction than the *MBLPD* algorithm<sup>8</sup>. It has also been observed that the maximum thickness after metal filling using the MBLPD algorithm does not exceed the maximum thickness of the original design. This is noteworthy since some manufacturers prefer the minimum and maximum thickness values to be within pre-specified bounds. Hence, for the proposed scheme, the metal filled design is never worse (usually it is much better) than the original design in this regard. This is not true for the designs after density-driven approaches.

In addition, the proposed algorithm always introduces a smaller amount of fill when compared with the density-driven approach. The proposed algorithm only introduces 4.7% fill, whereas the density-driven algorithm introduces 10.9% fill. Since metal fills can introduce undesirable coupling effects, it is likely that the proposed metal filling will have significantly less timing impact when compared to the density-driven approach. However, a more thorough investigation is necessary and will be done as a part of future work.

#### 7 Conclusions and Future Work

A novel metal filling algorithm that is based on the physics of the copper damascene process was presented. Key predictors of final thickness range that can be efficiently computed were identified and used to drive metal filling. In particular, the impact of the ECP profile on final surface topography was thoroughly investigated. To the best of our knowledge, this is the first metal filling algorithm that uses an ECP model among other things to guide the metal filling. Experimental results indicate that the proposed method can significantly reduce the final thickness range after metal filling. This is in sharp contrast to the density-driven approaches which can actually increase the final thickness range after metal filling, thereby potentially adversely impacting yield.

The proposed method also introduced significantly smaller amount of fill when compared to the density-driven approach. This leads us to believe that the *MBLPD* algorithm will have less timing impact after metal filling. However, this needs to investigated more thoroughly. Future work will include a timing aware *MBLPD* algorithm to minimize timing impact. Extensions of the *MBLPD* algorithm to consider accumulative multilayer effects are also being investigated.

# References

- [1] J. Luo, Q. Su, C. Chiang and J. Kawa, *A Layout Dependent Full-Chip Copper Electroplating Topography Model*, ICCAD 2005.

- [2] R. Tian, D. Wong and R. Boone, Model-based Dummy Feature Placement for Oxide Chemical-Mechanical Polishing Manufacturability, IEEE Trans CAD, 2001.

- [3] A. B. Kahng, G. Robins, A. Singh and A. Zelikovsky, New and Exact Filling Algorithms for Layout Density Control, Intl. Conf. on VLSI Design, 1999.

- [4] Y. Chen, A. B. Kahng, G. Robins and A. Zelikovsky, Monte-Carlo Algorithms for Layout Density Control, ASP-DAC 2000.

- [5] Y. Chen, A. B. Kahng, G. Robins and A. Zelikovsky, Practical Iterated Fill Synthesis for CMP Uniformity, DAC, 2000.

- [6] X. Wang, C. Chiang, J. Kawa and Q. Su, *Min-Variance Iterative Method for Fast Smart Dummy Features Density Assignment in Chemical-Mechanical Polishing*, ISQED 2005.

- [7] R. Tian, X. Tang, and D. F. Wong. Filling and Slotting for Process Uniformity Control in Copper Chemical-Mechanical Polishing, CMP-MIC 2001.

- [8] D. O. Ouma, Modeling of Chemical Mechanical Polishing for Dielectric Planarization, Ph. D. Dissertation, Dept. of EECS, MIT, Cambridge, MA, USA, 1998.

- [9] T. E. Gbondo-Tugbawa, Chip-scale Modeling of Pattern Dependencies in Copper Chemical Mechanical Polishing Processes, Ph.D. Dissertation, Dept. of EECS, Cambridge, MIT, MA, USA, 2002.

- [10] J. Luo and D. A. Dornfeld, Integrated Modeling of Chemical Mechanical Planarization for Sub-Micron IC Fabrication: from Particle Scale to Feature, Die and Wafer Scales, Springer-Verlag, Berlin, Germany, 2004.

- [11] S. Lakshminarayanan, P.J. Wright and J. Pallinti, *Electrical Characterization of the Copper CMP Process and Derivation of Metal Layout Rules*, IEEE Trans. Semiconductor Manufacturing, 2003.

<sup>&</sup>lt;sup>7</sup>There was an average ECP thickness range increase of 22% for these examples. Due to lack of space, the detailed ECP data could not be presented.

<sup>&</sup>lt;sup>8</sup>It should be noted that since *MBLPD* algorithm is heuristic in nature, it is not guaranteed to always obtain the optimum ECP thickness range reductions.