## A 31-µ W, 148-fs Step, 9-bit Capacitor-DAC-Based Constant-Slope Digital-to-Time Converter in 28-nm CMOS

Chen, Peng; Zhang, Feifei; Zong, Zhirui; Hu, Suoping; Siriburanon, Teerachot; Staszewski, Robert Bogdan

DOI

10.1109/JSSC.2019.2939663

Publication date

**Document Version** Final published version

Published in

IEEE Journal of Solid-State Circuits

Citation (APA)

Chen, P., Zhang, F., Zong, Z., Hu, S., Siriburanon, T., & Staszewski, R. B. (2019). A 31-µ W, 148-fs Step, 9-bit Capacitor-DAC-Based Constant-Slope Digital-to-Time Converter in 28-nm CMOS. *IEEE Journal of Solid-*State Circuits, 54(11), 3075-3085. Article 8850049. https://doi.org/10.1109/JSSC.2019.2939663

Important note

To cite this publication, please use the final published version (if applicable). Please check the document version above.

Copyright

Other than for strictly personal use, it is not permitted to download, forward or distribute the text or part of it, without the consent of the author(s) and/or copyright holder(s), unless the work is under an open content license such as Creative Commons.

Please contact us and provide details if you believe this document breaches copyrights. We will remove access to the work immediately and investigate your claim.

# A 31-μW, 148-fs Step, 9-bit Capacitor-DAC-Based Constant-Slope Digital-to-Time Converter in 28-nm CMOS

Peng Chen<sup>®</sup>, Student Member, IEEE, Feifei Zhang, Student Member, IEEE, Zhirui Zong<sup>®</sup>, Student Member, IEEE, Suoping Hu, Student Member, IEEE, Teerachot Siriburanon<sup>®</sup>, Member, IEEE, and Robert Bogdan Staszewski<sup>®</sup>, Fellow, IEEE

Abstract—This article proposes a power-efficient highly linear capacitor-array-based digital-to-time converter (DTC) using a charge redistribution constant-slope approach. A fringe-capacitor-based digital-to-analog converter (C-DAC) array is used to regulate the starting supply voltage of the constant discharging slope fed to a fixed-threshold comparator. The DTC operation mechanism is analyzed and design tradeoffs are investigated. The proposed DTC consumes merely 31  $\mu\rm W$  from a 1-V supply when clocked at 40 MHz, while achieving a fine resolution of 148 fs over a 9-bit range. The measured differential nonlinearity (DNL) and integral nonlinearity (INL) are 0.96/1.07 LSB.

Index Terms—Capacitor-based digital-to-analog converter (C-DAC), constant slope, digital-to-time converter (DTC), femtosecond resolution, integral nonlinearity (INL), phase-locked loop (PLL), power-efficient, ultra-low power (ULP).

## I. INTRODUCTION

AN important building block in time-domain signal processing [1], a digital-to-time converter (DTC) delays the transition edges of its input signal (e.g., clock) by an amount dynamically controlled by a digital code. It is increasingly utilized in various applications that exploit fast and precise edge manipulations in scaled low-voltage CMOS technology, e.g., polar transmitters [2], phase-locked loops (PLLs) [3]–[5], [7], [8], [10], [12], [13], direct-digital frequency synthesis (DDFS) [14], sampling oscilloscopes [15], and successive approximation time-to-digital converters (SAR-TDCs) [16].

Traditionally, to achieve low in-band phase noise in an all-digital PLL (ADPLL), a fine-resolution TDC with a dynamic range of at least one oscillator period is required [1].

Manuscript received April 2, 2019; revised June 30, 2019, and September 1, 2019; accepted September 2, 2019. Date of publication September 26, 2019; date of current version October 23, 2019. This article was approved by Associate Editor Pietro Andreani. This work was supported by the Science Foundation Ireland (SFI) under Grant 14/RP/I2921. (Corresponding author: Peng Chen.)

P. Chen, F. Zhang, S. Hu, T. Siriburanon, and R. B. Staszewski are with the School of Electrical and Electronic Engineering, University College Dublin, Dublin 4, Ireland (e-mail: peng.chen.1@ucdconnect.ie).

Z. Zong was with the Department of Microelectronics, Delft University of Technology, 2628 CD Delft, The Netherlands. He is now with NXP Semiconductors, 5656 AE Eindhoven, The Netherlands.

Color versions of one or more of the figures in this article are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/JSSC.2019.2939663

Such a wide range makes it one of the most power-hungry blocks in the ADPLL [after the digitally controlled oscillator (DCO)]. Moreover, high linearity is essential in avoiding significant in-band fractional spurious tones.

In recent years, the DTCs have aroused significant interest in the design of PLLs [4], [5], [11], [13], [27], [28]. A DTC can reduce the TDC detection range in a fractional-N ADPLL via a reference clock edge prediction and realignment. With the assistance of the DTC, one can greatly reduce power consumption of the phase detection circuitry, which can now employ a TDC with a much narrower range. This is instrumental in pushing the ADPLL's power consumption to below 1 mW for Bluetooth low-energy (BLE) applications [4], [5]. However, [4] suffers from large fractional spurs due to the DTC's nonlinearity. A phase-dithering technique was adopted in the later version [5]. The literature also reports a DTC used to dither the reference clock over an ADPLL to suppress its spurs at near integer-N channels [17], as well as ADPLLs achieving fractional-N operation based on a conventional integer-N PLL architecture [7], [10]. The dynamic range of the DTC can be relaxed by using multi-phase outputs from a DCO divider or a coarse-fine DTC architecture [6], [12]. It can further be reduced with an assistance of a phase interpolator (PI) in the feedback path [7]. A DTC with a fine resolution can reduce its quantization noise contribution in the PLL.

A generic DTC topology would consist of input and output buffers in addition to a variable delay-generation part. One popular DTC propagates the signal through a digitally controlled delay chain comprised of inverters/buffers [4]. This approach suffers from limited resolution and high power consumption due to a large number of delay cells. For highresolution DTCs, special attention is paid to the input-output buffers to isolate the delay-generation part from the outside interference. For example, in [10], the DTC delay unit is built as a cascade of two inverters, each loaded with tunable MOS capacitors, and extra buffers are added to isolate each delay unit. By controlling the MOS capacitance, the loading of each of the two inverters has two states, generating two different delays. That architecture suffers from a MOS capacitance mismatch among different units. Thus, the DTC resolution and nonlinearity are limited by the manufacturing variations.

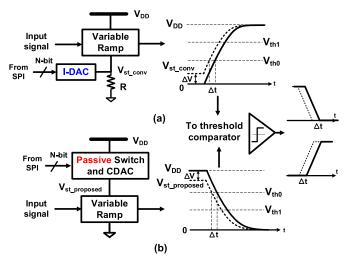

Fig. 1. Conceptual diagram of the delay-generation circuit in (a) conventional constant-slope DTC using I-DAC [19] and (b) proposed constant-slope DTC using passive C-DAC.

Another popular method in [18] regulates a variable voltage ramp driving a threshold comparator. The variable ramp generator can be simply modeled as a first-order RC circuit. The slope of the voltage ramp is controlled through tunable capacitances. Even though the DTC can achieve fine resolution <500 fs [12], [18], it suffers from poor linearity due to a nonlinear relationship between the propagation delay and the input ramp time. This problem can be alleviated by exploiting a constant-slope method [3], [19], which generates voltage ramps with different starting voltages. As shown in Fig. 1(a), the slope is maintained and it ideally produces a linear relationship if the following threshold comparator has a constant sampling aperture. Despite the significant improvements in resolution and linearity, the main power contributor in [19] is the current digital-to-analog converter (I-DAC), which consumes 1 mW. To reduce the power consumption of I-DAC, an isolation technique of ramp signal, and offset generations was proposed in [3] in which the DAC has to only charge a 10× smaller capacitor. However, since the architecture still needs an independent DAC and a cascoded current mirror, the power consumption is 98  $\mu$ W at 26 MHz.

In this article, we propose a new architecture of the constant-slope DTC that achieves much lower power consumption while maintaining high resolution and linearity. By exploiting a passive capacitor-based DAC (C-DAC) as part of the ramp generator, the power consumption is significantly reduced through charge redistribution. The capacitive DAC regulates the supply of the ramp generator, creating a linearly stepped starting voltage for the constant discharging slope. The high linearity of the DTC is ensured by the constant-slope method and excellent matching of C-DAC's metal-oxide-metal (MOM) capacitors as well as a builtin predistortion. The C-DAC design follows the principles and derives benefits from a successive approximation register analog-to-digital converter (SAR-ADC) architecture [21], [22]. The C-DAC output supplies the threshold comparator such that different supply voltages generate proportional delays with extremely fine resolution through the constant-slope discharging process, as shown in Fig. 1(b).

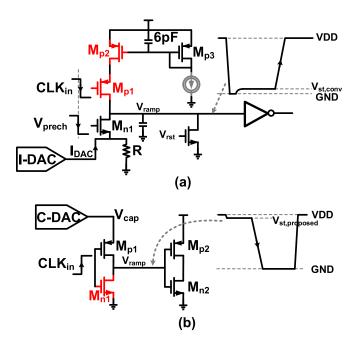

Fig. 2. Detailed comparison of (a) conventional constant-slope charging DTCs adopting I-DAC [19] and (b) proposed constant-slope-discharging DTC adopting C-DAC.

In the rest of this article, Section II explains the proposed concept of constant-slope discharging using the programmable passive C-DAC. Design details of the proposed DTC architecture are described in Section III. The experimental results are shown in Section IV. At last, the conclusions are given in Section V.

#### II. CHARGE-REDISTRIBUTION CONSTANT SLOPE

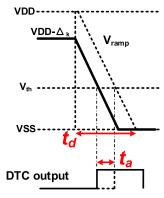

#### A. Constant-Slope Discharging

Comparison between the DTC variable-slope and constantslope methods can be found in [19]. Briefly, the delay is controlled in the former by varying the signal's voltage transition slope at its rising (i.e., significant) edges. However, this suffers from a systematic nonlinearity (see [19, Fig. 7]) due to the rise time versus delay dependence in practical comparators. In contrast, the constant-slope method maintains the same slope at every ramp. The conventional constant-slope DTCs employ an I-DAC, as shown in Fig. 1(a). A variable start voltage  $(V_{\text{st\_conv}})$  is used to linearly program the variable delay. All ramps above a certain  $V_{\text{st conv,max}}$  have the same shape, thus exerting the same influence on the following comparator. Considering a more practical model of the comparator, the output voltage transition mainly responds to a "soft" range of input voltages [ $V_{\text{th0}}$ ,  $V_{\text{th1}}$ ]. As long as  $V_{\text{st conv,max}} < V_{\text{th0}}$ , it is reasonable to assume the comparator does not add extra nonlinearity, irrespective of the comparator's bandwidth.

The proposed C-DAC-based constant-slope DTC shown in Fig. 1(b) inherits the benefits of the conventional I-DAC structure but with additional advantages derived from the constant-slope discharging, rather than the constant-slope charging as in [19]. As a result, the start voltage here ranges from  $V_{\rm st,min}$  to  $V_{\rm DD}$ , in contrast with the ground-to- $V_{\rm st,max}$  range in the I-DAC-based DTC. The differences are shown in Fig. 2. For both the DTCs, the difference in the voltage ramp

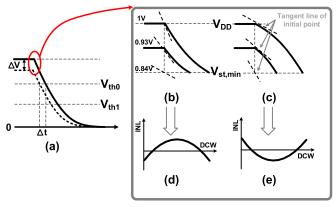

Fig. 3. Built-in predistortion decomposition. (a) Discharging slope influenced by (b) channel-length modulation and (c) variable loading capacitance. Induced INL from (d) channel-length modulation and (e) from variable loading capacitance.

is within the start voltage ranges. Note that the output delay can be expressed as  $\Delta t = \Delta V/(I/C)$ , where I/C is the ramp slope. We will discuss I and C in the following regarding their influences on  $\Delta t$ , which contains DTC nonlinearity effects.

Due to the channel-length modulation, the current is not constant, since the drain voltage changes in the saturation mode. The drain current is given by [20]

$$I = \frac{1}{2}\mu_n C_{\text{ox}} \frac{W}{L} (V_{\text{GS}} - V_{\text{th}})^2 (1 + \lambda_I V_{\text{DS}}). \tag{1}$$

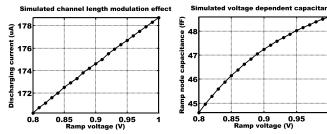

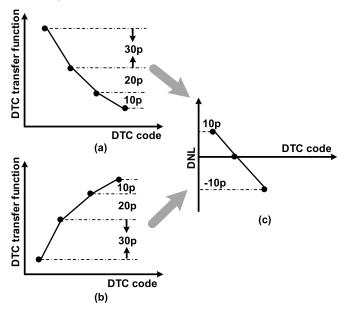

To partially alleviate this issue in the prior-art circuits, a 6-pF capacitor is connected to the gate of  $M_{P2}$  to stabilize its  $V_{GS}$  voltage, as shown in Fig. 2(a). The cascode transistor  $M_{P1}$  helps to stabilize the drain voltage of  $M_{P2}$ . The charging current is thus less sensitive to the variable starting voltage  $V_{\rm st}$ . At the same time, to achieve a *fixed* capacitance of the  $V_{\text{ramp}}$ node, a big capacitor is attached to that node. Its value should be large enough so that it suppresses the MOS parasitics, thus dominating the  $V_{\text{ramp}}$  node's capacitance. Similar issues could also affect the proposed DTC architecture. During the discharging process, various DTC control codes produce varying  $V_{\rm st}$ , which is the  $V_{\rm DS}$  of the discharging NMOS. Without the isolating cascode current mirror, the channellength modulation effect would be more severe. However, it is interesting to point out that  $V_{\text{ramp}}$  node's capacitance also increases with the voltage. In other words, the  $V_{\text{ramp}}$ node manifests a varactor property, which compensates the nonlinearity induced by the channel-length modulation when properly sized, as shown in Fig. 3.

With only the channel-length modulation effect, the discharging current would reduce as  $V_{\rm ramp}$  drops, making the discharging curve convex. On the other hand, when only the variable loading capacitance effect exists, the slope increases as  $V_{\rm ramp}$  drops, forcing the discharging curve to be concave. The dashed lines in Fig. 3(b) and (c) are slopes at the points of interest. Fig. 3(d) corresponds to the case when the channel length modulation effects dominate the nonlinearity contribution. The integral nonlinearity (INL) in Fig. 3(e) indicates that the variable loading capacitance exerts more influence than the channel length modulation. Those two opposing effects

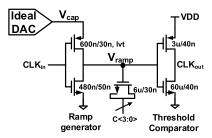

Fig. 4. Schematic of the DTC core with ideal DAC feeding  $V_{\text{cap}}$ .

can roughly compensate, with the latter acting as a built-in predistortion for the former across a certain voltage range.

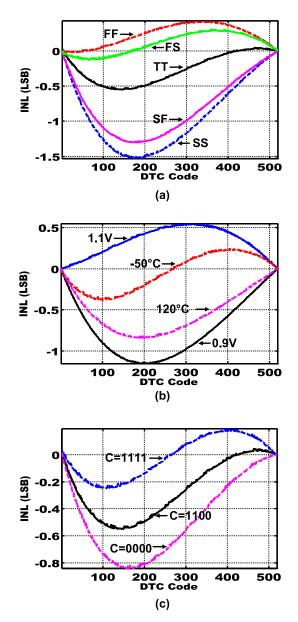

#### B. PVT Sensitivity

To verify the effectiveness of the proposed technique, Fig. 4 schematic is now simulated under different process, voltage, temperature (PVT) variations. The circuit comprises the DTC core  $M_{P1,N1,P2,N2}$  with an ideal DAC to generate  $V_{\text{cap}}$  ranging from 0.8 to 1 V while the incoming clock runs at 40 MHz. The control code C(3:0) is set to "1100" in the PVT sensitivity analysis. Post-layout simulations indicate the typical range of  $\sim 80$  ps. Fig. 5(a) shows the post-layout simulation results over five process corners. The worst case INL is maintained within 2 LSBs over the 9-bit range. To check for the temperature and voltage variations, the INL is simulated at 0.9- and 1.1-V supply voltages at room temperature, as well as at −50°C and 120°C at 1-V supply, respectively, as shown in Fig. 5(b). Its worst case INL is slightly larger than 1 LSB over the 9-bit design. Specifically, at the lower supply of 0.9 V, due to the slope of the ramp node capacitance against the ramp voltage being steeper, the varactor effect dominates. As a result, the INL curve tends to be convex, which is aligned with the analysis in Fig. 3(e). As compared with [19, Fig. 13], the proposed architecture features comparable linearity but at a much lower complexity and power consumption.

#### C. Trial Calibration

In order to allow for a possible calibration of the non-linearity, four identical MOS capacitors were added in this article (missing in our earlier version in [9]) between the ramp node and the ground, as shown in Fig. 4. When we enable (EN) all the MOS capacitors with the calibration control code "0000," the varactor effect dominates when compared with the light-loading case of "1111," which shows a desired S-shape. Code "0000" thus causes the INL curve to become convex. The conclusion is verified by the post-layout simulations in Fig. 5(c).

#### III. PROPOSED DIGITAL-TO-TIME CONVERTER

This design is based on our charge-sharing constant-slope DTC topology originally proposed in [9]. In this article, four identical MOS capacitors are added at the  $V_{\rm ramp}$  node for fine-tuning the INL. Furthermore, the original 5-bit topology was extended to 9 bits, while the layout and the MOS transistor sizes were additionally optimized.

Fig. 5. Simulated INL characteristics of the DTC core including parasitic capacitances with an ideal DAC at (a) different corners, (b) temperature and supply variations, and (c) different calibration codes.

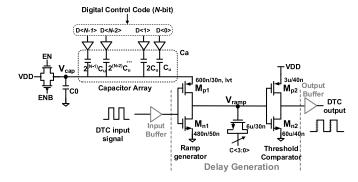

## A. Proposed DTC Architecture

The schematic of the proposed constant-slope discharging DTC is shown in Fig. 6. It consists of the input and output buffers, a ramp generator, and a threshold comparator. The transmission gate, fixed capacitor  $C_0$ , and controllable capacitor array  $C_a$  are used to regulate the supply voltage of the ramp generator. The output of the ramp generator drives the threshold comparator to generate the time delay  $\Delta t_d$  proportional to the initial voltage drop  $\Delta V_{\rm DD}$ . Four identical loading MOS capacitors are added at the ramp node controlled by  $C\langle 3:0 \rangle$  to explore the calibration possibility.

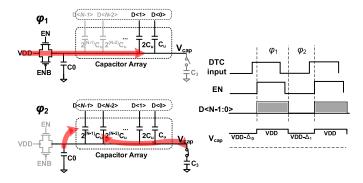

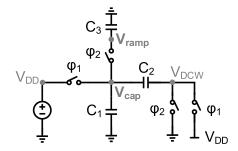

The supply regulation of the ramp generator is carried out in two phases: pre-charging  $\varphi_1$  and discharging  $\varphi_2$ , as shown in Fig. 7. During  $\varphi_1$ , the transmission gate is transparent and the shaded part of the  $C_a$  capacitor array (corresponding to  $C_2$  in Fig. 9) is disabled by keeping the zero voltage across

Fig. 6. Schematic of the proposed constant-slope discharging DTC.

Fig. 7. Illustration of charging and discharging processes of the programmable C-DAC.

the constituting capacitors, as shown in Fig. 9. The fixed capacitor  $C_0$  and the remaining (un-shaded) capacitor array (corresponding to  $C_1$  in Fig. 9) are precharged to  $V_{\rm DD}$ . During the  $\varphi_2$  discharge phase, the transmission gate is opaque and all the capacitor arrays gets engaged together with the  $V_{\rm ramp}$  node capacitance  $C_3$ . The charge is thus shared with the newly engaged capacitors. This produces a regulated voltage drop on  $V_{\rm cap}$ . Referring to Figs. 6 and 9,  $V_{\rm cap}$  is expressed as

$$V_{\rm cap} = \frac{C_1}{C_1 + C_2 + C_3} V_{\rm DD} \tag{2}$$

where  $C_1 = C_0 + \sum_{i=0}^{N-1} D\langle i \rangle 2^i C_u$  and  $C_2 = \sum_{i=0}^{N-1} (1 - D\langle i \rangle) 2^i C_u$ . The total capacitance  $C_1 + C_2 + C_3$  is kept constant. When  $C_1$  is linearly increased with the digital control code,  $C_2$  will be linearly decreased by the same amount. As an example, a 900-fF capacitance is first pre-charged to 1 V. Then, the charge is shared with the total 1000-fF capacitance, making  $V_{\text{cap}}$  settled at 0.9 V. The supply voltage for the ramp generator discharging becomes  $V_{\text{DD}} - \Delta_k$ , which is the start voltage  $(V_{\text{st proposed}})$  in Fig. 1(b).

## B. Timing Strategy

A detailed timing diagram is shown in Fig. 8. The DTC input rising (i.e., significant) edge is the critical edge to be precisely delayed. Compared with the conventional DTCs [4], [5], there is one extra control signal here whose timing should be taken care of, i.e., the control signal EN for the transmission gate. Since it affects the next cycle operation, together with the DTC delay control word,  $D\langle N-1:0\rangle$ , the rising edge of the EN should come safely *after* the rising edge

Fig. 8. Timing diagram of the proposed constant-slope DTC using charge redistribution.

of the DTC input.  $\Delta_{tr}$  is the time to allow the ramp inverter output  $(V_{\text{ramp}})$  to discharge to ground and well settle there. This way, EN and D(N-1:0) will not affect the previous DTC input rising edge propagation. After the transmission gate is enabled, DTC enters into  $\varphi_1$ .  $V_{\text{cap}}$  is preset to  $V_{\text{DD}}$  in preparation for  $\varphi_2$ .  $\Delta_{tf}$  represents the time difference between the nearby falling edge of EN and D(N-1:0). This ensures that the transmission gate will be turned off completely. The charge stored on the capacitor array is still  $(C_0 + kC_u)V_{DD}$ , where  $C_0$  is a fixed capacitance,  $C_u$  is the unit capacitance of C-DAC, and k represents the number of chosen charging units in the capacitor array. After D(N-1:0) is reset to zero, the stored charge is shared over  $C_1 + C_2 + C_3$ , resulting in  $V_{\rm cap}$  going to  $V_{\rm DD} - \Delta_K$ . When the next DTC input arrives,  $V_{\rm ramp}$  discharges from  $V_{\rm DD} - \Delta_K$  to ground. Thus, by different initial discharging ramp voltages, the DTC output rising edge is programmably delayed. More control bits selected result in less capacitors engaged in storing the charge. Consequently, a larger voltage drop  $V_{\text{ramp}}$  node will ensue, giving less discharging time. Finally, this causes the input signal to propagate faster to the output.

#### C. Power Advantages With Abstract Diagram

As shown in Fig. 2(a), I-DAC continues to charge the ramp node even after the voltage is settled, thus burning power on the resistor. In contrast, the proposed C-DAC stores the charge on the ramp node after the voltages settles to  $V_{\rm st}$ , with no more charge drawn from the supply. This is because  $M_{n1}$  is disabled before the arrival of the critical input rising edge, thus preventing the charge on  $V_{\rm cap}$  to go to ground. This helps to improve the energy efficiency.

The proposed C-DAC does not inherently dissipate any charge, since  $V_{\rm cap}$  achieves the desired voltage by charge sharing and there is no path to ground for the  $V_{\rm cap}$  node. By taking advantage of the charge redistribution, the variable start voltage generation can be realized with much less power than that in the conventional I-DAC. Fig. 9 shows a simplified abstract model of the charge redistribution used in the proposed DTC. During  $\varphi_1$ ,  $C_1$  is charged to  $V_{\rm DD}$ , accumulating an

Fig. 9. Abstract diagram of charge redistribution mechanism.

overall charge of  $C_1V_{\rm DD}$ , while the charge on  $C_2$  is zero due to its both nodes being at the same voltage potential. During  $\varphi_2$ , the right-hand side electrode of  $C_2$ , which is denoted as  $V_{DCW}$ , gets grounded. The  $V_{\text{ramp}}$  node capacitance gets also shorted to  $V_{\text{cap}}$ . The charge originally stored on  $C_1$  is hence redistributed over  $C_1 + C_2 + C_3$ , reducing  $C_1$ 's voltage from  $V_{DD}$  to  $C_1 V_{\rm DD}/(C_1+C_2+C_3)$ . Even though the charge is conserved, the energy loss due to the charge redistribution during the  $\varphi_1$  to  $\varphi_2$  transition is  $C_1(C_2+C_3)/(C_1+C_2+C_3)\cdot V_{DD}^2$ . Then, from  $\varphi_2$  to the next cycle of  $\varphi_1$ , the power supply needs to fuel up that energy loss. Thus, the energy loss of the entire operation period is obtained as  $C_1(C_2 + C_3)/(C_1 + C_2 + C_3) \cdot V_{DD}^2$ . The energy loss can be small when  $C_1$  is much larger than  $C_2$  and  $C_3$ . Even though the voltage variation on  $C_2$  and  $C_3$ can be as large as  $V_{\rm DD}$  or close to  $V_{\rm DD}$ , their capacitances are relatively small.  $C_1$  is large, while its voltage variation is small. Hence, the power consumption caused by this passive network of three capacitors could be very low.

Referring back to Fig. 4, the  $V_{\rm cap}$  node features a slow discharging slope, forcing the threshold comparator to stay in the feedthrough status for a long time. Thus, longer channel length can be selected for it to bring the power consumption down.

As a last remark, there is no need for extra-large buffers to drive the DTC input signal, as compared with the conventional ramp generator [19]. Consequently, the power consumption can be further reduced.

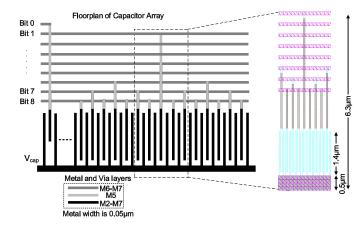

## D. C-DAC-Based Ramp Generator

The size of the transmission gate should be carefully chosen to minimize its on-resistance and to reduce the  $V_{\text{cap}}$  settling time so that it does not limit the operating speed of the DTC. The capacitor array implementation should take into account its power efficiency, matching accuracy, and noise suppression. The digital control word drivers should be strong enough to keep the settling time within half clock period, satisfying the timing conditions in Fig. 8. In this article, a customdesigned MOM capacitor [21] is used, as shown in Fig. 10. The unit capacitance is laid out using metal-2 (M2) to M7 with 0.05- $\mu$ m width and 1.4- $\mu$ m length. The layout extraction estimates a unit capacitance of 0.84 fF. It is chosen to guarantee that the quantization noise is buried under the thermal noise level. Only M5 is used to connect the capacitor and the control bits. The distance from the control bits to the custom-designed capacitor fingers is enlarged to reduce the unwanted parasitics.

Fig. 10. Layout fragment of the capacitor array.

The LSB is implemented with half of the length of one unit finger to reduce the area. The fixed capacitor ( $C_0$ ) is built as an MOM capacitor from the PDK and has a value of 2.26 pF. The capacitors occupy the majority of core area. The voltage variation range for  $V_{\rm cap}$  is from the minimum initial voltage ( $V_{\rm st,min}$ ) to  $V_{\rm DD}$ , where  $V_{\rm st,min}$  can be determined as

$$V_{\rm st,min} = \frac{C_0 V_{\rm DD}}{C_a + C_0 + C_3}.$$

(3)

With the implemented capacitor array,  $V_{\rm st,min}$  is 820 mV. In the layout, M1 and M2 are not used in  $C_0$  in order to reduce the substrate interference. The ramp inverter size should not be overly large in order to prevent its self-parasitic capacitance from being too large. The avoidance of the cascode structure in the ramp inverter, as previously done in Fig. 2, is instrumental in substantially lowering the supply voltage in the proposed DTC. In addition, a guard ring is used for noise isolation.

## E. Threshold Comparator

The threshold comparator serves two roles: providing the loading capacitance as well as the predistortion for the channel-length modulation. As mentioned in Section II-A, the discharging slope is I/C. After the node  $V_{\text{ramp}}$  discharges below  $V_{\rm st,min}$ , the discharging curves under different DTC control codes are the same, therefore experiencing the same effects. Thus, when deciding on I/C, only the part above  $V_{\rm st,min}$  needs to be considered. In order to ensure that the initial ramp voltage stays sufficiently away from the comparator's threshold voltage, its NMOS transistor is sized larger than the PMOS. This resulted in substantial lowering of the comparator's threshold. When the drain voltage of  $M_{n1}$  in the ramp generator drops from  $V_{\rm DD}$  to  $V_{\rm st,min}$ , it still operates in the saturation region. Then, the discharged current linearly increases with the drain voltage scaled by the factor of  $\lambda_I$ following the conventional I-V formula in (1). As a result, to keep the slope I/C constant, the loading capacitance must decrease as  $V_{\text{ramp}}$  decreases from  $V_{\text{DD}}$  to  $V_{\text{st,min}}$ .

The size of the comparator is large and is optimized to slow down the input ramp and to cover the desired dynamic range. Thus, the node capacitance of  $V_{\text{ramp}}$  is mainly determined by

Fig. 11. Schematic simulation results of channel-length modulation effect and voltage-dependent capacitance of  $V_{\text{ramp}}$  node.

the gate capacitance of the comparator rather than the drain capacitance of ramp generator, even though the latter can still contribute a small amount of nonlinearities. Considering that the gate voltage of the comparator (inverter) is still high even when it drops to  $V_{\text{st,min}}$ , then  $M_{p2}$  is OFF and  $M_{n2}$  is ON. Hence, the comparator output node voltage stays low. Under these conditions, sweeping the gate from  $V_{\rm st,min}$ to  $V_{\mathrm{DD}}$  causes the NMOS gate capacitance to increase much faster than that of the PMOS. By properly sizing the PMOS versus NMOS, the slope due to capacitance variation can approach the slope due to channel-length modulation. Fig. 11 shows the circuit simulation results of capacitance at the  $V_{\text{ramp}}$ node against its voltage. Even though this C-V curve is not very linear, this nonlinearity has a weak effect on the DTC delay nonlinearity, as explained in the following. After the  $V_{\text{ramp}}$ -node capacitance manages to track the channel-length modulation effect, the ramp capacitance can be written as

$$C = C_0(1 + \lambda_C V) + f_n(V) \tag{4}$$

where  $f_n(V)$  models the nonlinearity of the  $V_{\text{ramp}}$ -node C-V relationship

$$\Delta t = \Delta V / (I/C)$$

$$= \frac{\Delta V}{I_0(1 + \lambda_I V) / (C_0(1 + \lambda_C V) + f_n(V))}$$

$$= \frac{\Delta V}{I_0/C_0} \left( 1 + \frac{f_n(V)}{C_0(1 + \lambda_C V)} \right). \tag{5}$$

It can be observed that  $f_n(V)$  needs to be scaled by  $C_0$  before affecting the delay nonlinearity. The large size of the comparator not only makes the ratio more robust but also provides strong driving ability to the following output buffer. It can be roughly calculated that  $\lambda$  for the current and capacitance is  $\lambda_I = 0.25 \text{ V}^{-1}$  [see (1)] and  $\lambda_C = 0.45 \text{ V}^{-1}$  [see (4)], respectively. However, considering that fixed parasitics will be added to the capacitance at post-layout simulations, the latter  $\lambda$  approaches to the former until they are first-order-compensated properly.

#### IV. EXPERIMENTAL RESULTS

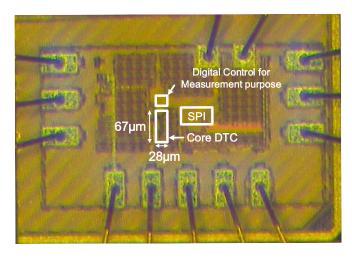

To demonstrate the effectiveness of the proposed techniques, a brand new constant-slope DTC is implemented in a 28-nm low power (LP) CMOS. Fig. 12 shows the chip micrograph. The effective DTC area is 0.0019 mm<sup>2</sup>. When operating at a 1-V supply, it consumes only 31  $\mu$ W while clocking at 40 MHz.

Fig. 12. Die photograph of the proposed DTC.

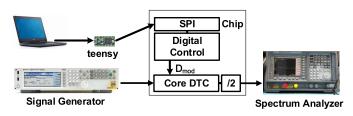

Fig. 13. Measurement setup.

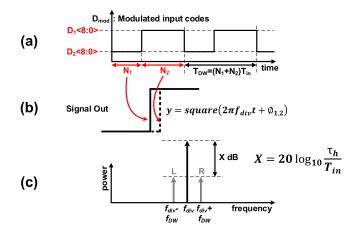

Fig. 14. DTC delay measurement via phase modulation method. (a) Input modulating codes, D1 and D2. (b) Corresponding modulated output delays in time domain. (c) Spectrum of modulated delays.

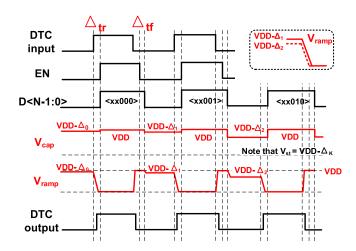

The measurement setup is shown in Fig. 13. To measure the DTC nonlinearity,  $^1$  a sensitive frequency-domain method is adopted from [25], as shown in Fig. 14(c). A digital control block is embedded to generate alternating codes D1 and D2 to periodically modulate the DTC delay.  $\Phi_1$  and  $\Phi_2$  are the corresponding DTC output phases. The spurious tone level then corresponds to the delay difference between the two corresponding control codes. Similar to the method in [25], the DTC output is divided by 2, yielding a 20-MHz square wave as the output. The spectrum is measured using Agilent E4405B ESA-E. The relation between the spur

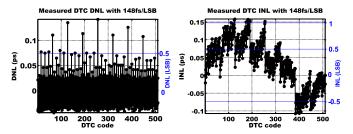

Fig. 15. Measurement results of DNL/INL.

Fig. 16. Nonlinearity under 0.75-V supply voltage.

level and the relative time step can be expressed as

$$\operatorname{spur}_{h}(f_{\operatorname{div}} \pm f_{\operatorname{DW}}) = 20 \log_{10} \left( \frac{|\tau_{h}|}{T_{in}} \right) [\operatorname{dBc}]$$

(6)

where  $\tau_h$  is the delay difference between the two corresponding control codes D1(8:0) and D2(8:0);  $T_{in}$  is the period of the DTC input clock;  $f_{div}$  is the fundamental frequency of the divided DTC output; and  $f_{DW}$  is the frequency of the code waveform. The code waveform is set as eight periods of the input clock. Referring to the fundamental frequency at 20 MHz, the relative spur level at 5-MHz offset is, for example, -105 dBc when the DTC control codes are modulated with a single-LSB step difference, which corresponds to a 141fs delay step. The measured differential nonlinearity (DNL) and INL are, respectively, 0.96 and 1.07 LSB of the 148-fs step size, as shown in Fig. 15. The DNL is mainly contributed by the MSB switching, originating from the systematic layout parasitics. Moreover, due to the LSB being implemented as half of the unit length as other bits, there is an odd-even pattern in the DNL originating from the process mismatch and parasitics. By avoiding the usage of the cascoding topology, the proposed DTC can operate at a low supply voltage. This was verified at as low as 0.75 V with 16-LSB steps per measurement. These results are shown in Fig. 16. The INL is 3.2 LSB with a full range of 187 ps. Its INL degrades due to voltagedependent ramp node capacitance dominating the nonlinearity. Since the sizes are optimized with 1-V supply, the degraded INL is within the expectations. Current consumption of the DTC core (all the blocks in Fig. 6) is measured under 1 and 0.75 V. The results are shown in Fig. 17, indicating that the consumed power increases with DCW. The average currents are 22.7 and 16.2  $\mu A$ , respectively. To help generating  $\Delta_{\rm ff}$ and  $\Delta_{tf}$  in Fig. 8, extra buffers are needed. These assistant 3-ns delay buffers for the timing control consume 8.5 and 6.1  $\mu A$  (post-layout simulations), respectively, running at 40 MHz, which can be further reduced, since their jitter has

<sup>&</sup>lt;sup>1</sup>In this context, DNL/INL are defined as DNL =  $|A_{i+1} - A_i|/A_{LSB} - 1$ , INL =  $(A_{i,real} - A_{i,ideal})/A_{LSB}$ , where  $A_{LSB}$  is a positive LSB.

|                       | ISSCC18<br>[3] Liu | ISSCC11<br>[12] Pavlovic | ESSCIRC14<br>[18] Markulic | JSSC15<br>[19] Ru            | JSSC16<br>[26] Sievert | VLSI06<br>[15] Inagaki | ISSCC14<br>[4] Chillara | This work           |                   |

|-----------------------|--------------------|--------------------------|----------------------------|------------------------------|------------------------|------------------------|-------------------------|---------------------|-------------------|

| Method                | Constant slope     | Variable<br>slope        | Variable<br>slope          | Constant<br>slope<br>(I-DAC) | Interpolation          | Variable<br>threshold  | Buffer-<br>based        | Cons<br>slo<br>(C-D | pe                |

| Technology (nm)       | 65                 | 65                       | 28                         | 65                           | 28                     | 90                     | 40                      | 28                  |                   |

| Supply (V)            | 1                  | 1.2                      | 0.9                        | 1.2                          | 1.1                    | 1.0                    | 1.0                     | 1.0                 | 0.75              |

| Resolution (fs)       | 580                | 241-330                  | 550                        | 189                          | 244                    | 1000                   | 21500                   | 148                 | 365               |

| Number of bits        | 10                 | 10                       | 10                         | 10                           | 11                     | 6                      | 6                       | 9                   |                   |

| INL <sup>1</sup> (fs) | 870*+              | 3000                     | 990+                       | 328+                         | 1200 <sup>+</sup>      | 3200                   | 67600*                  | 159 <sup>+</sup>    | 1170 <sup>+</sup> |

|                       | (0.15%)            | (1%)                     | (0.18%)                    | (0.17%)                      | (0.24%)                | (5%)                   | (4.9%)                  | (0.21%)             | (0.63%)           |

| Range (ps)            | 593                | 247-338                  | 563                        | 189                          | 500                    | 64                     | 1376                    | 76                  | 187               |

| Power (mW)            | 0.14@<br>52MHz     | 2.2@<br>40MHz            | 0.5@<br>40MHz              | 0.8+1.0@<br>55MHz            | 19.8@<br>2GHz          | N/A                    | 0.0137@<br>32MHz        | 0.031@<br>40MHz     | 0.017@<br>40MHz   |

10<sup>-10</sup>

10<sup>-1</sup>

10

Power/Freq (J)

TABLE I PERFORMANCE COMPARISON WITH THE STATE-OF-THE-ART DTCs

<sup>&</sup>lt;sup>1</sup> \*End-point, <sup>+</sup>Best fit straight line.

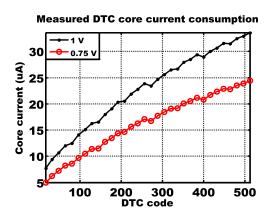

Fig. 17. Current consumption versus DTC control codes with two different voltages.

10 2

INL/Range

Tasca ISSCC'11 A

> Paylovio ISSCC'11

> > ISSCC'14

10

only a slight influence compared with the 3 ns delay. Thus, the total power consumption of the DTC is 31  $\mu W$  with the 1-V supply, and 17  $\mu W$  with 0.75 V.

The measured phase noise of the whole DTC, including the test circuitry, with a 100-MHz sinusoidal input and a 50-MHz square-wave output is -151 dBc/Hz at 100 kHz and -154 dBc/Hz at above 1-MHz offset frequencies. The integrated jitter from 10 kHz to 10 MHz is 267 fs. By incorporating this DTC into an ADPLL, the DTC might contribute some limited amount into the ADPLL's in-band phase noise. Doubling the dissipated power could roughly reduce the jitter power by half. The power consumption of the self-biased buffer is not included in the total power calculation, unlike in [19], which embeds the input driving buffer for testing purpose into the core DTC design. In addition, the input of the proposed compact DTC core is a square wave rather than a sine wave, which is favored by the digital design approach.

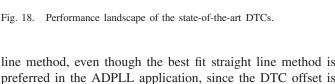

The key performance metrics of the proposed DTC are compared in Table I with the state-of-the-art DTCs. It is noted that the constant-slope DTCs can achieve fine resolution and excellent linearity. In this article, the proposed DTC maintains such performance, while consuming significantly less power. Moreover, we should acknowledge that different definitions of INL are chosen in various publications. The endpoint usually gives worse numbers than the best fit straight

line method, even though the best fit straight line method is preferred in the ADPLL application, since the DTC offset is normally compensated by the loop.

The DTC performance comparison landscape considering the four key parameters (consumed power, clock frequency, INL, and range) is shown in Fig. 18. The highly accurate matching property of the MOM capacitors in the C-DAC and the constant-slope operation result in a competitive INL/range performance along the horizontal axis. For the vertical axis, which shows the power consumption over clock frequency, this article achieves top performance thanks to the excellent power efficiency of the passive C-DAC, simple ramp generator, and threshold comparator. No additional biasing circuits and current mirror are needed.

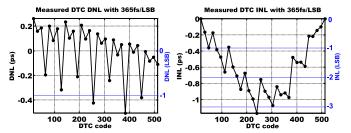

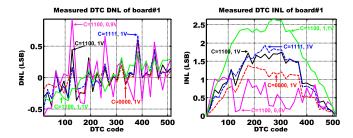

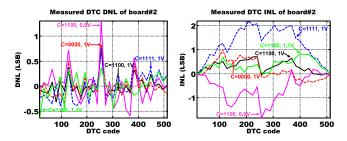

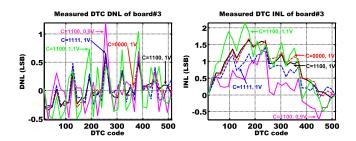

The above measurements were done with board #3 and control codes for the loading MOS capacitors C(3:0)=1100. To check the influence from process and supply variations, and how much influence the trial calibration (four identical MOS varactors controlled by C(3:0) can impose, three boards were measured under different control codes of C(3:0) and supply voltages. To simplify the DNL/INL measurements, readings were taken every 16 LSBs. The results can be slightly different from the ones taken by 1-LSB step due to the measurement error. The measured resolution and DNL/INL are shown in Figs. 19-21 and summarized in Table II. It can

Fig. 19. Measured DNL/INL of board #1.

Fig. 20. Measured DNL/INL of board #2.

Fig. 21. Measured DNL/INL board #3.

TABLE II

PERFORMANCE SUMMARY OF THREE BOARDS

|                 | '1100' | '0000' | '1111' | '1100' | '1100' |

|-----------------|--------|--------|--------|--------|--------|

|                 | @1 V   | @1 V   | @1 V   | @0.9 V | @1.1 V |

| Board#1         |        |        |        |        |        |

| Resolution (fs) | 163    | 170    | 156    | 204    | 140    |

| DNL (LSB)       | 0.60   | 0.59   | 0.67   | 0.93   | 0.39   |

| INL (LSB)       | 1.75   | 1.39   | 1.94   | 1.06   | 2.66   |

| Board#2         |        |        |        |        |        |

| Resolution (fs) | 167    | 159    | 177    | 209    | 138    |

| DNL (LSB)       | 0.76   | 0.73   | 0.83   | 1.31   | 0.54   |

| INL (LSB)       | 0.71   | 2.20   | 0.99   | 1.84   | 1.89   |

| Board#3         |        |        |        |        |        |

| Resolution (fs) | 153    | 160    | 145    | 189    | 127    |

| DNL (LSB)       | 0.66   | 0.59   | 0.65   | 1.20   | 1.04   |

| INL (LSB)       | 1.64   | 1.69   | 1.42   | 1.34   | 2.15   |

be observed that the voltage variation has a larger influence on INL than the control-code tuning of the MOS capacitors. Comparing between the control codes "1111" and "0000," the significant influence by the tunable MOS capacitance is verified in boards #1 and #2. The INL difference is relatively small in board #3. Comparing the supply voltages between 0.9 and 1.1 V, its influence is verified by all three boards. The INL is more convex at 0.9 V than at 1.1 V. As a conclusion, the calibration can be done either by tuning the

Fig. 22. Linear model of constant-slope discharging voltage ramp.

supply voltage or by tuning the loading MOS capacitances at the ramp node.

#### V. CONCLUSION

In this article, we have proposed a high-resolution, ultralow-power (ULP) DTC. When operating at 1 V, it achieves 9-bit range with 148-fs step size at 31- $\mu$ W drained power. Benefiting from the constant-slope operation, the proposed DTC achieves 159-fs INL. It makes use of a simple inverter structure with a built-in predistortion and a passive capacitor array as a DAC generating the initial ramp voltage. The DTC can offer high resolution with good linearity while consuming extremely LP, thus making it suitable for the Internet-of-Things (IoT) applications.

#### APPENDIX

## A. Nonlinearity Versus Range

A larger ratio of the tuning range over the total delay will worsen the nonlinearity, since  $V_{\text{ramp}}$  node experiences more non-linear distortions. As shown in Fig. 22, for a given slope and total delay  $t_d$ , the range  $t_a$  can only be increased with a larger voltage drop  $\Delta_k$ , which obviously worsens the linearity. Under the 1-V supply, a drop to 0.7 V brings much worse linearity than a drop to 0.8 V.

#### B. Phase-Modulation Measurement Method

As commented in [25], a subset of INL points could also describe the DTC linearity if the INL behavior is fairly smooth. It means that measuring the DNL with 1-LSB steps should result in the same INL as with 16-LSB steps, provided noise is disregarded. However, making the measurements with the finest 1-LSB steps over the 9-bit range will accumulate the measurement error 511 times, adding more uncertainty to the results than with the coarse steps. This is even despite the fact that the spur sensitivity is better with finer steps. The noise can make the spur vary more at larger amplitudes. This requires longer time for averaging, resulting in significant increases in the measurement times.

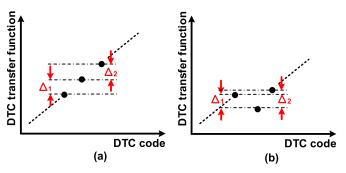

One scenario that has not been covered in [25] is the case when the DTC transfer function is not monotonic. The DNL/INL calculation cannot directly follow the procedures described in the above publication. As shown in Fig. 23,

Fig. 23. DTC transfer function (a) with monotonicity, and (b) without monotonicity.

Fig. 24. Different DTC transfer functions can yield the same measured DNL. (a) Descending transfer function. (b) Ascending transfer function. (c) Resulting DNL.

similar results can be derived for two different DTC transfer functions. The DNL calculation should involve with the polarity information. To eliminate such a potential issue, not only 1-LSB steps should be measured across the whole range but also 2 LSB or even more spacing should be confirmed.

Another scenario that should be seriously considered is the INL polarity when transferring DNL into INL. The method described in [25] assumes that the DTC delay increases with the control codes. Fig. 24 shows that two different DTC transfer functions can result in the same measured DNL. When the delay decreases with the control codes, the INL calculated through the conventional way needs to be inverted.

## ACKNOWLEDGMENT

The authors would like to thank H. Zheng, P. Vieira, and E. Staszewski for measurement help, Y. Zhu for the layout suggestion, J. Yin for valuable technical discussion, W. Zubrzycka for technical assistance, MCCI for their secondary support, and TSMC University Shuttle for chip fabrication.

#### REFERENCES

R. B. Staszewski et al., "All-digital TX frequency synthesizer and discrete-time receiver for Bluetooth radio in 130-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2278–2291, Dec. 2004.

- [2] I. Bashir, R. B. Staszewski, O. Eliezer, B. Banerjee, and P. T. Balsara, "A novel approach for mitigation of RF oscillator pulling in a polar transmitter," *IEEE J. Solid-State Circuits*, vol. 46, no. 2, pp. 403–415, Feb. 2011.

- [3] H. Liu et al., "A 0.98 mW fractional-N ADPLL using 10b isolated constant-slope DTC with FOM of -246 dB for IoT applications in 65 nm CMOS," in *IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech. Papers*, Feb. 2018, pp. 246–247.

- [4] V. K. Chillara *et al.*, "An 860  $\mu$ W 2.1-to-2.7 GHz all-digital PLL-based frequency modulator with a DTC-assisted snapshot TDC for WPAN (bluetooth smart and ZigBee) applications," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2014, pp. 172–173.

- [5] Y. He et al., "A 673 μW 1.8-to-2.5 GHz dividerless fractional-N digital PLL with an inherent frequency-capture capability and a phase-dithering spur mitigation for IoT applications," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2017, pp. 420–421.

- [6] A. Elmallah, M. G. Ahmed, A. Elkholy, W.-S. Choi, and P. K. Hanumolu, "A 1.6 ps peak-INL 5.3 ns range two-step digital-totime converter in 65 nm CMOS," in *Proc. IEEE Custom Integr. Circuits Conf. (CICC)*, Apr. 2018, pp. 1–4.

- [7] A. T. Narayanan et al., "A fractional-NSub-sampling PLL using a pipelined phase-interpolator with an FoM of -250 dB," *IEEE J. Solid-State Circuits*, vol. 51, no. 7, pp. 1630–1640, Jul. 2016.

- [8] E. Temporiti, C. Weltin-Wu, D. Baldi, M. Cusmai, and F. Svelto, "A 3.5 GHz wideband adpll with fractional spur suppression through TDC dithering and feedforward compensation," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2723–2736, Dec. 2010.

- [9] P. Chen, F. Zhang, Z. Zong, H. Zheng, T. Siriburanon, and R. B. Staszewski, "A 15-µW, 103-fs step, 5-bit capacitor-DAC-based constant-slope digital-to-time converter in 28 nm CMOS," in *Proc. IEEE Asian Solid-State Circuits Conf. (A-SSCC)*, Nov. 2017, pp. 93–96.

- [10] N. Pavlovic and J. Bergervoet, "A 5.3 GHz digital-to-time-converter-based fractional-N all-digital PLL," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2011, pp. 54–56.

- [11] Z. Zong, P. Chen, and R. B. Staszewski, "A low-noise fractional-N digital frequency synthesizer with implicit frequency tripling for mm-wave applications," *IEEE J. Solid-State Circuits*, vol. 54, no. 3, pp. 755–767, Mar. 2019

- [12] D. Tasca, M. Zanuso, G. Marzin, S. Levantino, C. Samori, and A. L. Lacaita, "A 2.9–4.0-GHz fractional-N digital PLL with bang-bang phase detector and 560-fs<sub>rms</sub> integrated jitter at 4.5-mW power," *IEEE J. Solid-State Circuits*, vol. 46, no. 12, pp. 2745–2758, Dec. 2011.

- [13] Y. Wu, M. Shahmohammadi, Y. Chen, P. Lu, and R. B. Staszewski, "A 3.5-6.8-GHz wide-bandwidth DTC-assisted fractional-N all-digital PLL with a MASH ΔΣ-TDC for low in-band phase noise," *IEEE J. Solid-State Circuits*, vol. 52, no. 7, pp. 1885–1903, Jul. 2017.

- [14] S. Talwalkar, T. Gradishar, B. Stengel, G. Cafaro, and G. Nagaraj, "Controlled dither in 90 nm digital to time conversion based direct digital synthesizer for spur mitigation," in *Proc. IEEE Radio Freq. Integr. Circuits Symp. (RFIC)*, May 2010, pp. 549–552.

- [15] K. Inagaki, D. Antono, M. Takamiya, S. Kumashiro, and T. Sakurai, "A 1-ps resolution on-chip sampling oscilloscope with, 64:1 tunable sampling range based on ramp waveform division scheme," in *Symp. VLSI Circuits*, *Dig. Tech. Papers*, Jun. 2006, pp. 61–62.

- [16] A. Mantyniemi, T. Rahkonen, and J. Kostamovaara, "A CMOS time-to-digital converter (TDC) based on a cyclic time domain successive approximation interpolation method," *IEEE J. Solid-State Circuits*, vol. 44, no. 11, pp. 3067–3078, Nov. 2009.

- [17] R. B. Staszewski et al., "Spur-free all-digital PLL in 65 nm for mobile phones," in *IEEE ISSCC Dig. Tech. Papers*, Feb. 2011, pp. 52–54.

- [18] N. Markulic, K. Raczkowski, P. Wambacq, and J. Craninckx, "A 10-bit, 550-fs step digital-to-time converter in 28 nm CMOS," in *Proc. 40th IEEE Eur. Solid State Circuits Conf. (ESSCIRC)*, Sep. 2014, pp. 79–82.

- [19] J. Z. Ru, C. Palattella, P. Geraedts, E. Klumperink, and B. Nauta, "A high-linearity digital-to-time converter technique: Constant-slope charging," *IEEE J. Solid-State Circuits*, vol. 50, no. 6, pp. 1412–1423, Jun. 2015.

- [20] B. Razavi, Design of Analog CMOS Integrated Circuits. Boston, MA, USA: McGraw-Hill, 2001.

- [21] P. J. A. Harpe et al., "A 26 μW 8 bit 10 MS/s asynchronous SAR ADC for low energy radios," *IEEE J. Solid-State Circuits*, vol. 46, no. 7, pp. 1585–1595, Jul. 2011.

- [22] M. Saberi, R. Lotfi, K. Mafinezhad, and W. A. Serdijn, "Analysis of power consumption and linearity in capacitive digital-to-analog converters used in successive approximation ADCs," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 8, pp. 1736–1748, Aug. 2011.

- [23] A. A. Abidi, "Phase noise and jitter in CMOS ring oscillators," *IEEE J. Solid-State Circuits*, vol. 41, no. 8, pp. 1803–1816, Aug. 2006.

- [24] S. Levantino, L. Romano, S. Pellerano, C. Samori, and A. L. Lacaita, "Phase noise in digital frequency dividers," *IEEE J. Solid-State Circuits*, vol. 39, no. 5, pp. 775–784, May 2004.

- [25] C. Palattella, E. A. M. Klumperink, J. Z. Ru, and B. Nauta, "A sensitive method to measure the integral nonlinearity of a digital-to-time converter based on phase modulation," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 62, no. 8, pp. 741–745, Aug. 2015.

- [26] S. Sievert et al., "A 2 GHz 244 fs-resolution 1.2 ps-Peak-INL edge interpolator-based digital-to-time converter in 28 nm CMOS," IEEE J. Solid-State Circuits, vol. 51, no. 12, pp. 2992–3004, Dec. 2016.

- [27] P. Chen et al., "Design and built-in characterization of digital-to-time converters for ultra-low power ADPLLs," in Proc. 41st IEEE Eur. Solid-State Circuits Conf. (ESSCIRC), Sep. 2015, pp. 283–286.

- [28] P. Chen, X. Huang, Y. Chen, L. Wu, and R. B. Staszewski, "An on-chip self-characterization of a digital-to-time converter by embedding it in a first-order ΔΣ loop," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 65, no. 11, pp. 3734–3744, Nov. 2018.

Peng Chen (S'15) received the B.Sc. degree in electronics from the Huazhong University of Science and Technology, Wuhan, China, in 2012, the M.Sc. degree in microelectronics from the Delft University of Technology (TU Delft), Delft, The Netherlands, in 2014, and the Ph.D. degree from University College Dublin, Dublin, Ireland, in 2019. His M.Sc. thesis was done at the IMEC Holst Center, Eindhoven, The Netherlands).

From 2014 to 2015, he was a Test Manager with Huawei Technologies, Amsterdam, The Netherlands.

From 2017 to 2018, he has been a Visiting Research Assistant with the University of Macau, Macau, China. His research interests include time-domain data converters, frequency synthesizers, and low-noise amplifier.

**Suoping Hu** (S'16) received the B.E. degree in integrated circuit design and system from Tianjin University, Tianjin, China, in 2013, and the M.Sc. degree (Hons.) in electronic science and technology from Shanghai Jiao Tong University, Shanghai, China, in 2016. He is currently pursuing the Ph.D. degree with University College Dublin, Dublin, Ireland.

In 2018, he was an Intern with Qualcomm, Cambridge, U.K., where he was part of the RFIC Design Group. His current research interests include analog

and radio-frequency circuits and low-power receiver.

**Teerachot Siriburanon** (S'10–M'16) received the B.E. degree in telecommunications engineering from the Sirindhorn International Institute of Technology (SIIT), Pathum Thani, Thailand, Thammasat University, Pathum Thani, in 2010, and the M.E. and Ph.D. degrees in physical electronics from the Tokyo Institute of Technology, Tokyo, Japan, in 2012 and 2016, respectively.

In 2016, he joined University College Dublin (UCD), Dublin, Ireland, as a Post-Doctoral Researcher under the Marie Skłodowska-Curie

Individual Fellowship Program. Since 2019, he has been an Assistant Professor with UCD. His research interests are CMOS wireless transceiver systems and clock/frequency generations for wireless and wireline communications.

Dr. Siriburanon was a recipient of the Japanese Government (MEXT) Scholarship, the Young Researcher Best Presentation Award at the Thailand–Japan Microwave in 2013, the ASP-DAC Best Design Award in 2014 and 2015, the IEEE SSCS Student Travel Grant Award in 2014, the IEEE SSCS Predoctoral Achievement Award in 2016, and the Tejima Research Award in 2016. He has been a Guest Editor of the IEEE TRANSACTIONS ON CIRCUIT AND SYSTEMS—I and serves as a Reviewer for the IEEE JOURNAL OF SOLID-STATE CIRCUITS.

Feifei Zhang (S'15) received the B.Sc. degree in navigation guidance and control from the Beijing University of Aeronautics and Astronautics, Beijing, China, and the M.Sc. degree in microelectronics from the Beijing Embedded System Key Laboratory, Beijing University of Technology, Beijing, in 2014. She is currently pursuing the Ph.D. degree with University College Dublin, Dublin, Ireland.

Her current research interest includes radiofrequency digital-to-analog converters.

**Robert Bogdan Staszewski** (M'97–SM'05–F'09) was born in Bialystok, Poland. He received the B.Sc. (*summa cum laude*), M.Sc., and Ph.D. degrees in electrical engineering from The University of Texas at Dallas, Richardson, TX, USA, in 1991, 1992, and 2002, respectively.

From 1991 to 1995, he was with Alcatel Network Systems, Richardson, where he was involved in synchronous optical network (SONET) cross-connect systems for fiber optics communications. In 1995, he joined Texas Instruments Inc., Dallas, TX, USA,

where he was elected as a Distinguished Member of Technical Staff (limited to 2% of technical staff). From 1995 to 1999, he was involved in advanced CMOS read channel development for hard disk drives. In 1999, he co-started the Digital RF Processor (DRP) Group, Texas Instruments Inc., with a mission to invent new digitally intensive approaches to traditional radio frequency (RF) functions for integrated radios in deeply scaled CMOS technology. From 2007 to 2009, he was the Chief Technology Officer of the DRP Group. In 2009, he joined the Delft University of Technology, Delft, The Netherlands, where he currently holds a guest appointment of Full Professor (Antoni van Leeuwenhoek Hoogleraar). Since 2014, he has been a Full Professor with University College Dublin (UCD), Dublin, Ireland. He has authored or coauthored five books, eight book chapters, and 100 journal and 180 conference publications. He holds 180 issued U.S. patents. His current research interests include nanoscale CMOS architectures and circuits for frequency synthesizers, transmitters and receivers, and quantum computers.

Dr. Staszewski was a recipient of the 2012 IEEE Circuits and Systems Industrial Pioneer Award. He is currently the TPC Chair of ESSCIRC 2019, Krakow, Poland.

Zhirui Zong (S'12) received the B.Eng. degree (Hons.) in electronic information engineering from the University of Electronic Science and Technology of China (UESTC), Chengdu, China, in 2012, and the Ph.D. degree in microelectronics from the Delft University of Technology, Delft, The Netherlands, in 2019.

Since 2018, he has been a Senior RF and a Mixed-Signal IC Designer with NXP Semiconductors, Eindhoven, The Netherlands. His current research interests include frequency synthesizer techniques

and integrated circuits for wireless communications and mm-wave radars.